- •Основы построения микропроцессорных систем

- •Основные определения и общие сведения

- •Типы информационного обмена

- •Параллельный обмен

- •Последовательный обмен

- •Протоколы обмена

- •1.3 Особенности применения цифровых микросхем

- •1.4 Структурные принципы микропроцессорных систем

- •Общая структура

- •Управление чтением и записью

- •Временные диаграммы чтения и записи

- •Подключение памяти и устройств ввода-вывода

- •Типы запоминающих устройств

- •Основные устройства микропроцессорной системы

- •Центральный процессор

- •Микропроцессор

- •Структура

- •Обработка команд

- •Временные диаграммы машинных циклов микропроцессора при чтении и записи

- •Система команд

- •Дешифратор адреса

- •Запоминающие устройства

- •Устройства ввода-вывода

- •Устройство звуковой сигнализации

- •Программируемый параллельный интерфейс

- •Универсальный синхронно-асинхронный приемопередатчик

- •Программируемый интервальный таймер

- •Программируемый контроллер приоритетных прерываний

- •Контроллер прямого доступа к памяти

- •Устройство индикации

- •Развитие архитектуры микропроцессорных систем

- •Технические требования

- •Сегментная модель памяти

- •Непрерывная модель памяти

- •Виртуальная адресация

- •Области оперативной памяти

- •Список литературы

- •Оглавление

- •1. Основы построения микропроцессорных систем 3

- •1. Основные устройства микропроцессорной системы 27

- •1. Развитие архитектуры микропроцессорных систем 76

Дешифратор адреса

Дешифратор адреса (ДА) представляет собой устройство, предназначенное для выборки микросхем ЗУ или УВВ, ячейки которых адресует микропроцессор (см. п. 1.4.2). Количество адресуемых ячеек определяется размером адресного пространства — величиной 2n+m, где n + m — число линий ША, передающих n старших и m младших разрядов кода. Единицей измерения этого пространства является величина 210, называемая 1К. Количество же микросхем ЗУ и УВВ, которые могут быть выбраны, зависит с одной стороны от числа выходов ДА, а с другой — от способа подключения устройств к этим выходам: совместного или раздельного (см. п.1.4.4).

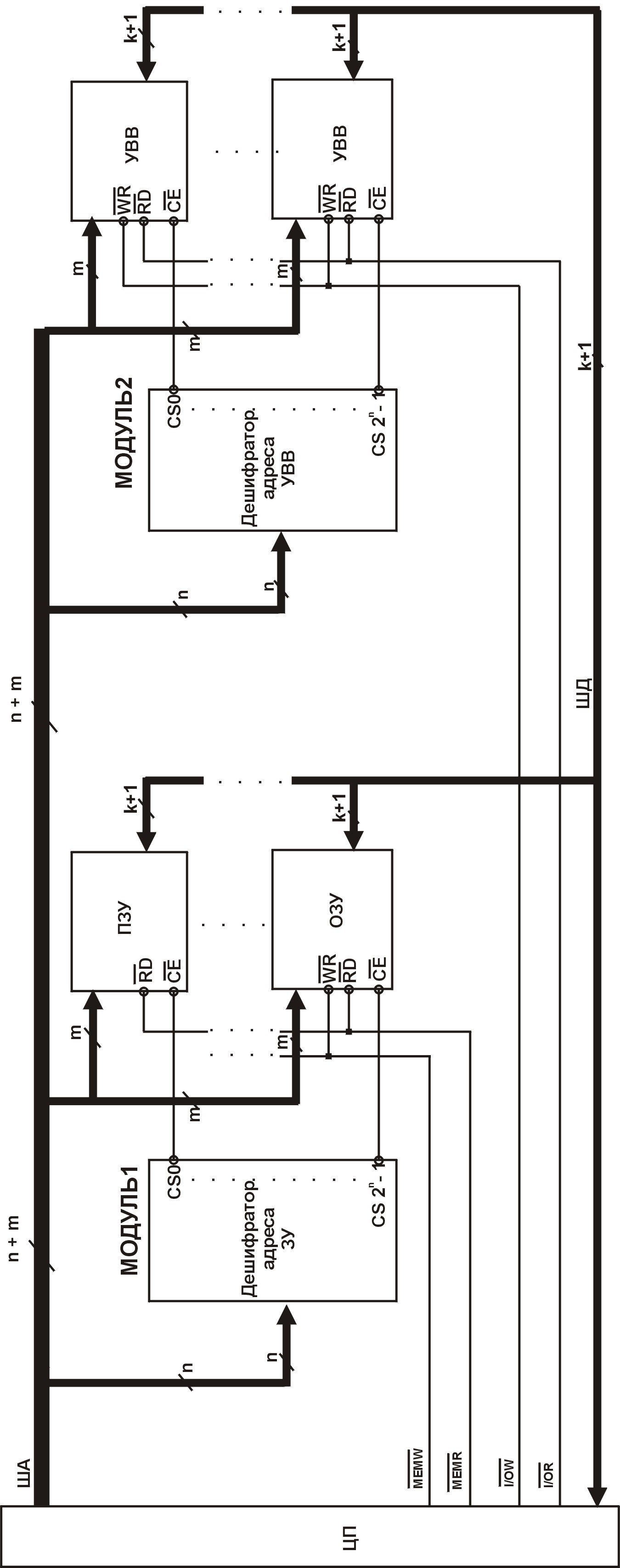

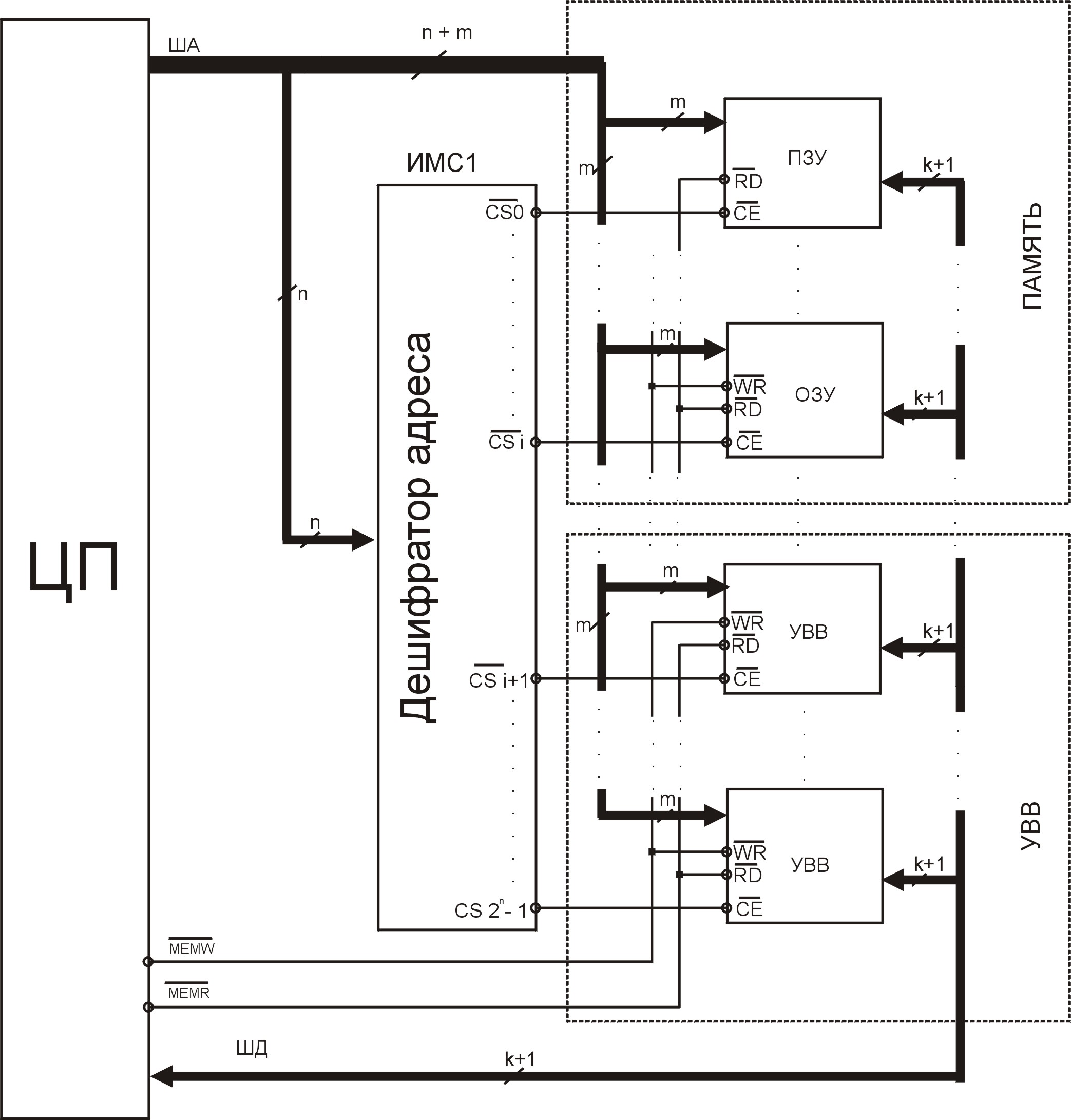

Если УВВ подключены раздельно с памятью, то обычно применяют два модуля ДА — для ЗУ и УВВ. Это необходимо для того, чтобы не перегружать по току выходы одного модуля при подключении к нему большого числа устройств. С точки зрения ЦП модули рассматриваются как один ДА с единой выходной магистралью (см. рис. 2.8), поскольку к их входам подключены одни и те же n линий старших разрядов адресного кода. Младшие m разрядов адреса определяют конкретную ячейку, с которой ЦП производит обмен информацией.

При

совместном подключении памяти и УВВ,

как правило, применяют один модуль ДА,

преобразующий n-разрядный

адресный код в 2n

линий

.

Эти линии распределяют между ЗУ и УВВ

в соответствии с их требуемым количеством

(см. рис. 2.9). На рисунке показано, что

выходы ДА

![]() —

—

![]() подключены к ЗУ, а

подключены к ЗУ, а

![]() —

—

![]() — к УВВ.

— к УВВ.

Микросхемы, применяемые при построении модулей ДА, имеют тристабильные управляемые выходы, что дает возможность реализовать дешифратор с необходимым числом выходных линий на основе нескольких микросхем в том случае, если выходов одной ИМС недостаточно.

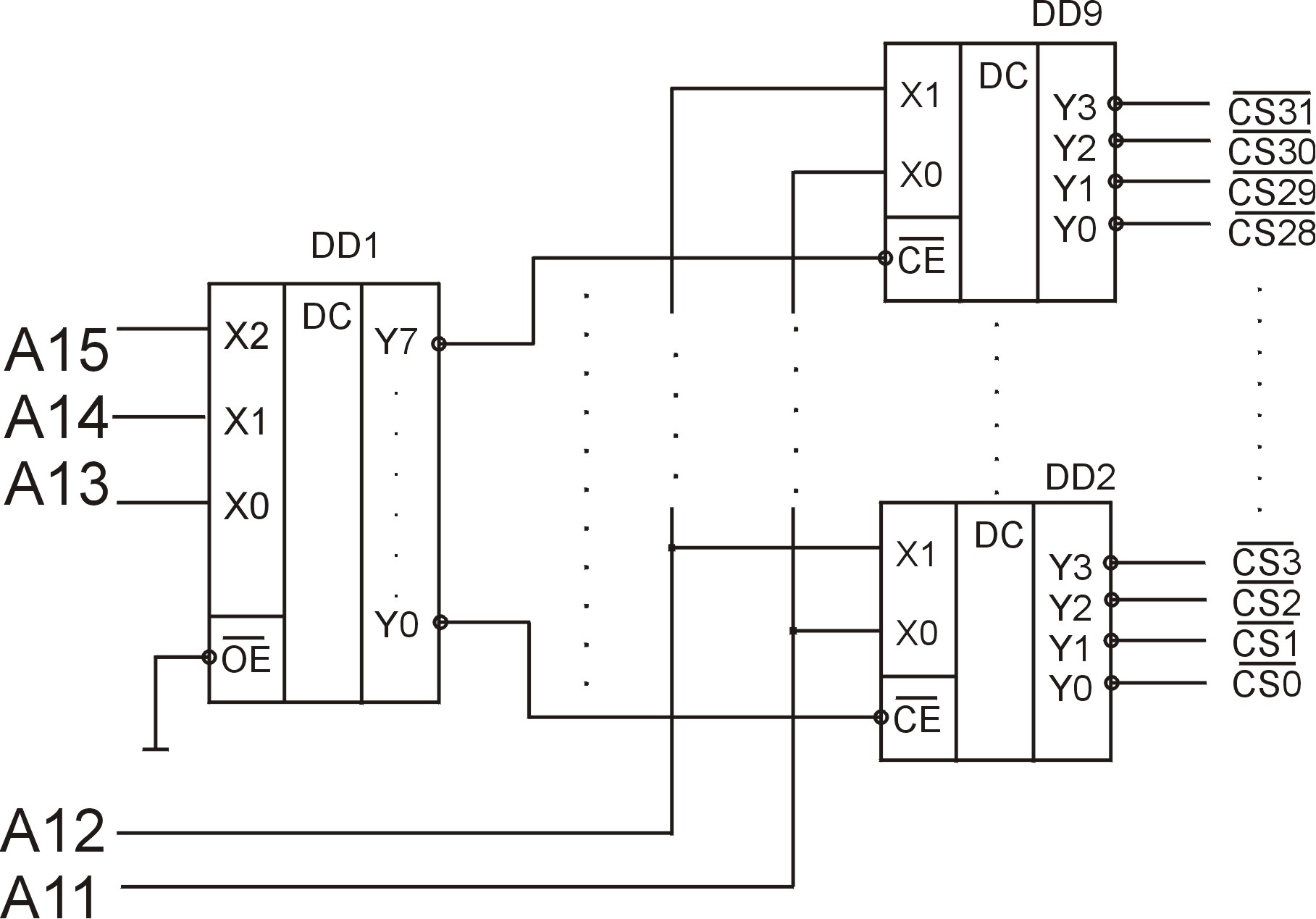

Для

примера рассмотрим модуль ДА, состоящий

из 9 стандартных ИМС, преобразующий

старшие адресные линии А11 — А15 (см. п.

2.1) в 32-разрядную выходную магистраль

![]() —

—

![]() .

Схема ДА приведена на рис. 2.10, где

обозначено:

.

Схема ДА приведена на рис. 2.10, где

обозначено:

DD1 — главного дешифратора;

DD2 — DD9 — подчиненных дешифраторов.

Главный дешифратор преобразует трехразрядный код на линиях А13 — А15 в 8 выходных сигналов, разрешающих работу подчиненным дешифраторам, которые вырабатывают сигналы выборки ЗУ или УВВ согласно базовым адресам. Например, если какое-либо из этих устройств имеет базовый адрес Е800h, то двоичный код на ША будет иметь значение 1110 1000 0000 0000. Соответствие разрядов кода номерам линий ША приведено на рис. 2.11. Двоичный код на линиях А13 — А15 представляет собой

Рис.

2.9

десятичное

число 7. В этой связи на выходе Y7

главного дешифратора будет установлен

L-уровень,

который разрешит работу подчиненному

дешифратору DD9.

Код на линиях А11, А12 соответствует

десятичному числу 1, поэтому ИМС DD9

на выходе Y1

выдаст логический 0 — таким образом

сигнал

![]() станет активен и произведет выборку

адресуемого устройства.

станет активен и произведет выборку

адресуемого устройства.

А15

А14

А13

А12

А11

А10 — А0

1

1

1

0

1

0

0

0

0

0

0

0

0

0

0

0

Рис.

2.11

Рис.

2.10