- •Основы построения микропроцессорных систем

- •Основные определения и общие сведения

- •Типы информационного обмена

- •Параллельный обмен

- •Последовательный обмен

- •Протоколы обмена

- •1.3 Особенности применения цифровых микросхем

- •1.4 Структурные принципы микропроцессорных систем

- •Общая структура

- •Управление чтением и записью

- •Временные диаграммы чтения и записи

- •Подключение памяти и устройств ввода-вывода

- •Типы запоминающих устройств

- •Основные устройства микропроцессорной системы

- •Центральный процессор

- •Микропроцессор

- •Структура

- •Обработка команд

- •Временные диаграммы машинных циклов микропроцессора при чтении и записи

- •Система команд

- •Дешифратор адреса

- •Запоминающие устройства

- •Устройства ввода-вывода

- •Устройство звуковой сигнализации

- •Программируемый параллельный интерфейс

- •Универсальный синхронно-асинхронный приемопередатчик

- •Программируемый интервальный таймер

- •Программируемый контроллер приоритетных прерываний

- •Контроллер прямого доступа к памяти

- •Устройство индикации

- •Развитие архитектуры микропроцессорных систем

- •Технические требования

- •Сегментная модель памяти

- •Непрерывная модель памяти

- •Виртуальная адресация

- •Области оперативной памяти

- •Список литературы

- •Оглавление

- •1. Основы построения микропроцессорных систем 3

- •1. Основные устройства микропроцессорной системы 27

- •1. Развитие архитектуры микропроцессорных систем 76

Устройства ввода-вывода

Данные устройства построены на специальных микросхемах и предназначены для подключения к ЦП внешних устройств (ВУ). К ВУ в частности относятся дисплей, клавиатура, накопители на гибких и жестких магнитных дисках, платы адаптеров, громкоговоритель звуковой сигнализации и т.д. Некоторые из устройств ввода-вывода позволяют расширять функциональные возможности МПС, обеспечивая информационное взаимодействие ЦП с другим оборудованием.

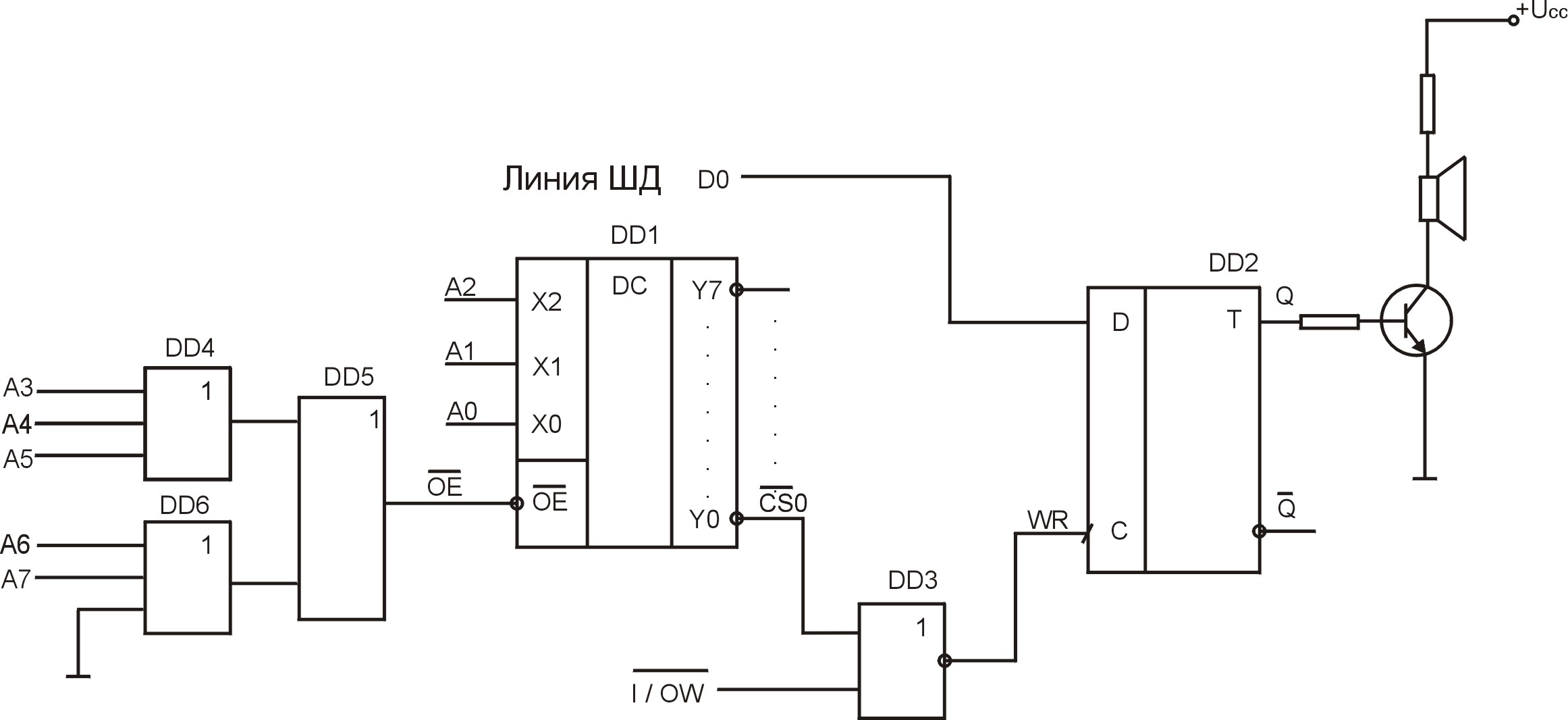

Устройство звуковой сигнализации

Кратковременный звуковой сигнал обычно выдается сразу после включения электропитания МПС, что означает начало функционирования, или формируется в процессе ее работы в необходимых случаях. Схема программируемого устройства звуковой сигнализации (УЗС), адресуемого кодом на линиях А0 — А7 и предназначенного для генерации звука определенной тональности, приведена на рис. 2.20, где обозначено:

DD1 — дешифратор кода адреса на линиях А0—А2 .

DD2 — D-триггер

DD3 — логический элемент 2ИЛИ-НЕ, вырабатывающий сигнал записи WR;

схема на элементах DD4, DD5, DD6, разрешающая работу DD1 сигналом L-уровня.

Микросхема триггера вырабатывает электрические импульсы необходимой длительности и частоты, которые затем усиливаются транзистором по току для их преобразования в звук громкоговорителем. Генерация импульсов на выходе Q осуществляется путем поочередной записи в триггер со звуковой частотой логических единиц и нулей, выдаваемых ЦП на линию D0 в соответствии с программой.

Временная

диаграмма, отображающая процесс

формирования триггером импульса Н-уровня

приведена на рис. 2.21. Согласно диаграмме,

в момент времени t0

ЦП выдает

на ША адресный код УЗС — в данном случае

00h.

В соответствии с этим кодом ДА устанавливает

сигнал

![]() L-уровня,

после чего на линию D0

помещается логическая 1. Далее, в момент

времени t1

ЦП вырабатывает низкоуровневый сигнал

записи

,

поступающий после

на вход DD3.

В результате операции ИЛИ-НЕ между

и

(

L-уровня,

после чего на линию D0

помещается логическая 1. Далее, в момент

времени t1

ЦП вырабатывает низкоуровневый сигнал

записи

,

поступающий после

на вход DD3.

В результате операции ИЛИ-НЕ между

и

(![]() )

микросхема DD3

на отрезке времени [t1,

t2] выдаст

импульс WR

Н-уровня, передний фронт которого

осуществит защелкивание в триггере DD2

логической 1, ранее

)

микросхема DD3

на отрезке времени [t1,

t2] выдаст

импульс WR

Н-уровня, передний фронт которого

осуществит защелкивание в триггере DD2

логической 1, ранее

Рис. 2.20

Рис. 2.21

установленной на линии D0. В этом случае в момент t1 выход триггера Q переключится из 0 в 1. Обратное переключение выхода произойдет в момент t3 при записи 0 — таким образом будет сформирован импульс длительностью [t1, t3].

Для того, чтобы D-триггер вырабатывал импульсы со звуковой частотой, существенно меньшей той, с которой работает микропроцессор, необходима пауза между моментами времени защелкивания единиц и нулей. Длительность паузы задается программно, путем циклического выполнения микропроцессором одной или нескольких команд.

Приведенная ниже программа реализует запись в триггер 65535 импульсов с частотой, определяемой временем выполнения подпрограммы временной задержки DELAY.

Программа 2.2

МЕТКА |

МНЕМОКОД |

КОММЕНТАРИЙ |

|

LXI SP 0900 |

Начало программы Запись в регистр SP адреса вершины стека. |

|

LXI B, FFFF |

Запись в регистровую пару ВС числа повторений цикла START (65535 повторений). |

START: |

XRA А |

Начало цикла START. Поразрядное логическое исключающее ИЛИ аккумулятора с самим собой, в результате чего его разряды устанавливаются в 0 (очистка). |

|

OUT 00 |

Вывод содержимого аккумулятора (нули) в УВВ (D-триггер) с адресом 00h. |

|

CALL DELAY |

Вызов подпрограммы, формирования временной паузы. |

|

CMA |

Инвертирование содержимого аккумулятора, в результате чего все его разряды установятся в 1. После этой операции аккумулятор будет содержать код FFh. |

|

OUT 00 |

Вывод содержимого аккумулятора (FFh) в УВВ. |

|

CALL DELAY |

Вызов подпрограммы, формирования временной паузы. |

|

DCX B |

Уменьшение содержимого регистровой пары ВС на 1. |

|

JNZ START |

Если результат не равен 0, то переход к метке START. Конец цикла START. |

|

HLT |

Конец программы. |

|

RST7 |

|

Подпрограмма 2.2

МЕТКА |

МНЕМОКОД |

КОММЕНТАРИЙ |

DELAY: |

LXI D, FFFF |

Начало подпрограммы DELAY. Запись в регистровую пару DE числа повторений цикла CYCLE. |

CYCLE: |

DCX D |

Начало цикла CYCLE. Уменьшение регистровой пары DE на 1. |

|

JNZ CYCLE |

Если результат не равен 0, то переход на метку CYCLE. Конец цикла CYCLE. |

|

RET |

Возврат в основную программу. Конец подпрограммы DELAY. |

Выполнение основной программы начинается с записи в регистр SP адреса вершины стека, в котором всякий раз будет сохраняться содержимое IP при вызове подпрограммы командами CALL DELAY. При завершении этой подпрограммы командой RET сохраненное в стеке значение IP будет восстановлено. Необходимость сохранения и восстановления IP была рассмотрена в п. 2.2.4.

Программа содержит цикл, начинающийся с метки START. Внутри цикла кроме остальных находятся две команды OUT 00, осуществляющие запись в триггер логических единиц и нулей. Первая команда OUT 00 выводит на ШД код 00h, а вторая — FFh. Если на ШД установлено значение 00h, то разряд D0 равен 0, если же FFh — то 1. Перед началом цикла в регистр В записывается код FFFFh. Счетчиком цикла является команда DCX B, уменьшающая регистр В на 1 до тех пор, пока не произойдет обнуления всех его разрядов, завершающего цикл. Таким образом, в результате циклического выполнения команд OUT 00 на линию D0 будет выдано 65535 единиц и нулей, частота формирования которых определит длительность звучания.