- •Основы построения микропроцессорных систем

- •Основные определения и общие сведения

- •Типы информационного обмена

- •Параллельный обмен

- •Последовательный обмен

- •Протоколы обмена

- •1.3 Особенности применения цифровых микросхем

- •1.4 Структурные принципы микропроцессорных систем

- •Общая структура

- •Управление чтением и записью

- •Временные диаграммы чтения и записи

- •Подключение памяти и устройств ввода-вывода

- •Типы запоминающих устройств

- •Основные устройства микропроцессорной системы

- •Центральный процессор

- •Микропроцессор

- •Структура

- •Обработка команд

- •Временные диаграммы машинных циклов микропроцессора при чтении и записи

- •Система команд

- •Дешифратор адреса

- •Запоминающие устройства

- •Устройства ввода-вывода

- •Устройство звуковой сигнализации

- •Программируемый параллельный интерфейс

- •Универсальный синхронно-асинхронный приемопередатчик

- •Программируемый интервальный таймер

- •Программируемый контроллер приоритетных прерываний

- •Контроллер прямого доступа к памяти

- •Устройство индикации

- •Развитие архитектуры микропроцессорных систем

- •Технические требования

- •Сегментная модель памяти

- •Непрерывная модель памяти

- •Виртуальная адресация

- •Области оперативной памяти

- •Список литературы

- •Оглавление

- •1. Основы построения микропроцессорных систем 3

- •1. Основные устройства микропроцессорной системы 27

- •1. Развитие архитектуры микропроцессорных систем 76

Запоминающие устройства

Типы и условные графические обозначения ИМС запоминающих устройств (ЗУ) были рассмотрены выше в п. 1.5. Подключение к системным шинам этих микросхем должно обеспечивать бесконфликтный доступ к ячейкам памяти при чтении и записи информации. Это возможно только в том случае (см. п. 1.4.3), если их переключение из Z-состояния в режим выдачи или приема данных будет осуществляться только во время действия импульсов синхронизации информационного обмена:

— чтения;

— записи.

Варианты стыковки ЗУ с шинами МПС будут рассмотрены на примерах подключения к этим шинам ИМС ПЗУ и статического ОЗУ.

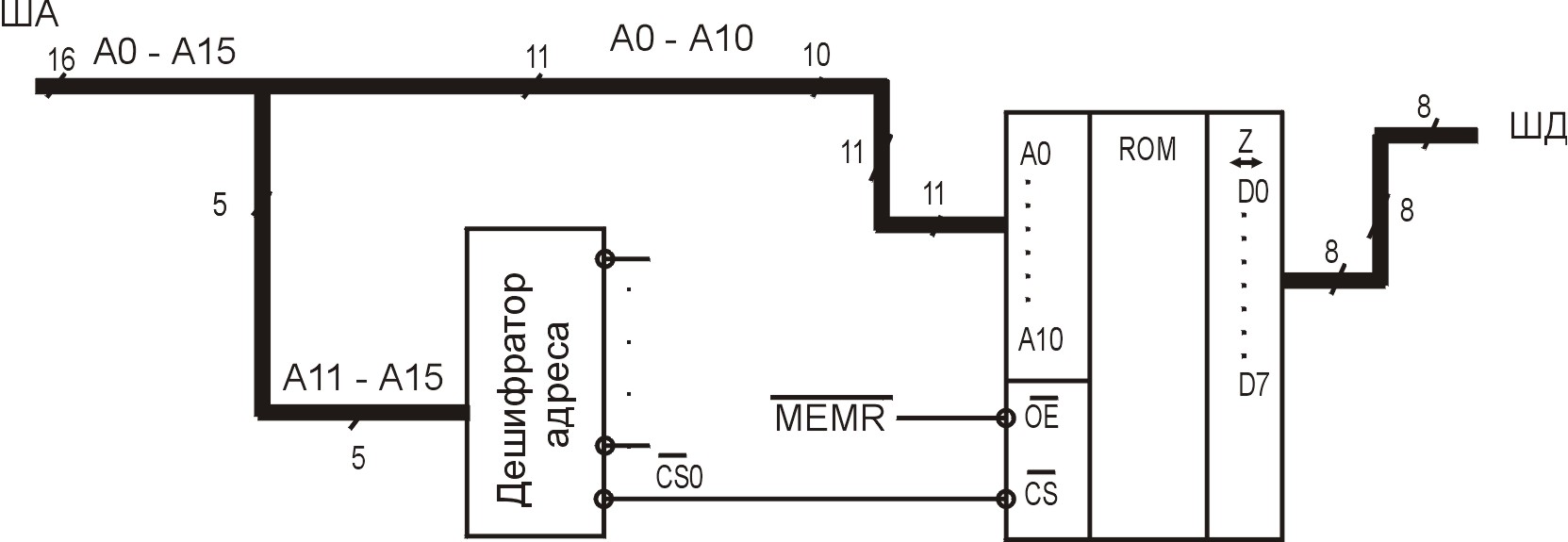

Схема

соединения ИМС ПЗУ с 16-разрядной ША и

8-разрядной ШД приведена на рис. 2.12. ПЗУ

имеет 11 адресных

(А0 — А10)

и 8 информационных линий D0

— D7,

подключенных соответственно к ША и ШД.

Таким образом, ПЗУ представляет собой

блок, содержащий 2К (211)

8-разрядных (однобайтных) ячеек общей

информационной емкостью 2К байт или 2

килобайта — 2КВ. Управление Z-состоянием

приемопередающих информационных линий

D0 —

D7

осуществляется по двум входам:

и

![]() .

Соединение выхода ДА

.

Соединение выхода ДА

![]() с входом

ПЗУ означает,

что начальный адрес блока будет нулевым.

В ячейке с этим адресом должен храниться

код операции команды, которая считывается

микропроцессором первой сразу же после

включения электропитания (см. п. 2.2.2) и

с ее выполнения начинается процесс

программной обработки данных. В этой

связи начальный участок адресного

пространства выделяется для

энергонезависимого хранения в ПЗУ

основы программного обеспечения МПС.

с входом

ПЗУ означает,

что начальный адрес блока будет нулевым.

В ячейке с этим адресом должен храниться

код операции команды, которая считывается

микропроцессором первой сразу же после

включения электропитания (см. п. 2.2.2) и

с ее выполнения начинается процесс

программной обработки данных. В этой

связи начальный участок адресного

пространства выделяется для

энергонезависимого хранения в ПЗУ

основы программного обеспечения МПС.

При адресации ячейки ПЗУ ДА выдает сигнал L-уровня, после чего микропроцессор вырабатывает импульс (чтение). Во время действия этого импульса ПЗУ переключится из Z-состояния на выдачу данных из адресованной ячейки (см. рис. 1.13 б) и таблицу 1.4).

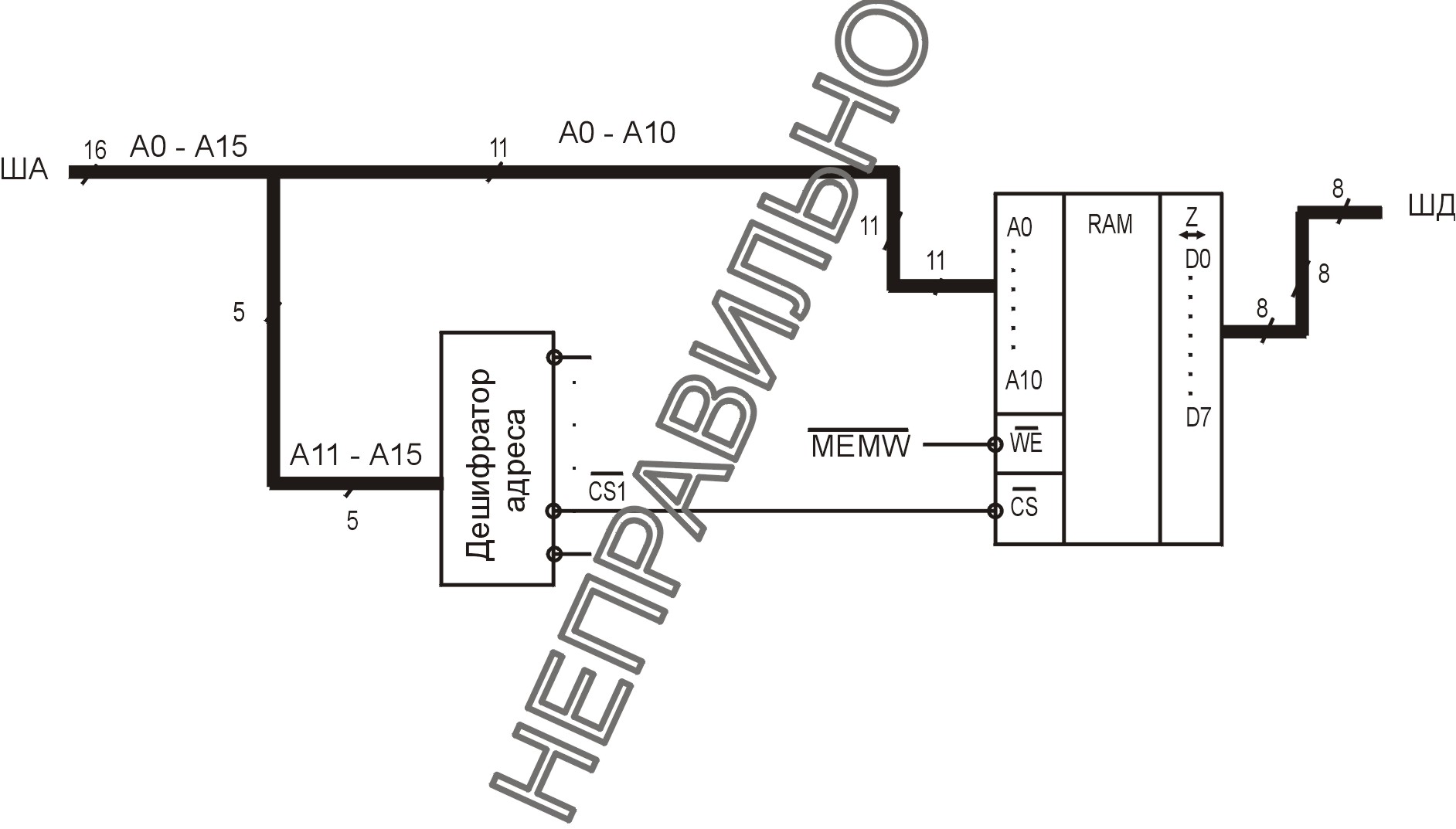

Если

ИМС ОЗУ подключить к системным шинам

аналогично ПЗУ так, как показано на рис.

2. 13, то произойдет конфликт на ШД при

записи данных в эту микросхему.

Действительно, после выборки нужной

микросхемы ОЗУ сигнал

(запись) некоторое время еще остается

пассивен — имеет Н-уровень, а записываемые

данные уже присутствуют на ШД (интервал

времени [t1,

t2] на рис.

1.13 а)). Из таблицы 1.5 следует, что если на

входе

![]() установлен сигнал Н-уровня, то выбранная

ИМС выдаст данные из адресованной

ячейки. В режиме выдачи микросхема будет

работать до тех пор, пока на вход

не поступит сигнал

L-уровня,

настраивающий ее на прием информации

— запись. Таким образом, существует

интервал времени, когда к ШД подключаются

устройства, одновременно являющиеся

источниками данных: с одной стороны —

микропроцессор, сформировавший данные

для записи, а с другой — ИМС ОЗУ, выдавшая

информацию по причине работы в режиме

чтения. Очевидно, что устройства,

подключившиеся к одной и той же шине, и

одновременно работающие в режиме выдачи

данных будут конфликтовать. Если бы

работа ИМС ОЗУ была запрещена при

пассивных значениях

и

,

то данные не выдавались бы, и конфликта

не произошло. Причина, по которой возник

конфликт, состоит в том, что управление

Z-состоянием

микросхемы ОЗУ осуществлялось только

одним сигналом —

установлен сигнал Н-уровня, то выбранная

ИМС выдаст данные из адресованной

ячейки. В режиме выдачи микросхема будет

работать до тех пор, пока на вход

не поступит сигнал

L-уровня,

настраивающий ее на прием информации

— запись. Таким образом, существует

интервал времени, когда к ШД подключаются

устройства, одновременно являющиеся

источниками данных: с одной стороны —

микропроцессор, сформировавший данные

для записи, а с другой — ИМС ОЗУ, выдавшая

информацию по причине работы в режиме

чтения. Очевидно, что устройства,

подключившиеся к одной и той же шине, и

одновременно работающие в режиме выдачи

данных будут конфликтовать. Если бы

работа ИМС ОЗУ была запрещена при

пассивных значениях

и

,

то данные не выдавались бы, и конфликта

не произошло. Причина, по которой возник

конфликт, состоит в том, что управление

Z-состоянием

микросхемы ОЗУ осуществлялось только

одним сигналом —

![]() ,

а сигналы

и

в управлении этим состоянием не

участвовали.

,

а сигналы

и

в управлении этим состоянием не

участвовали.

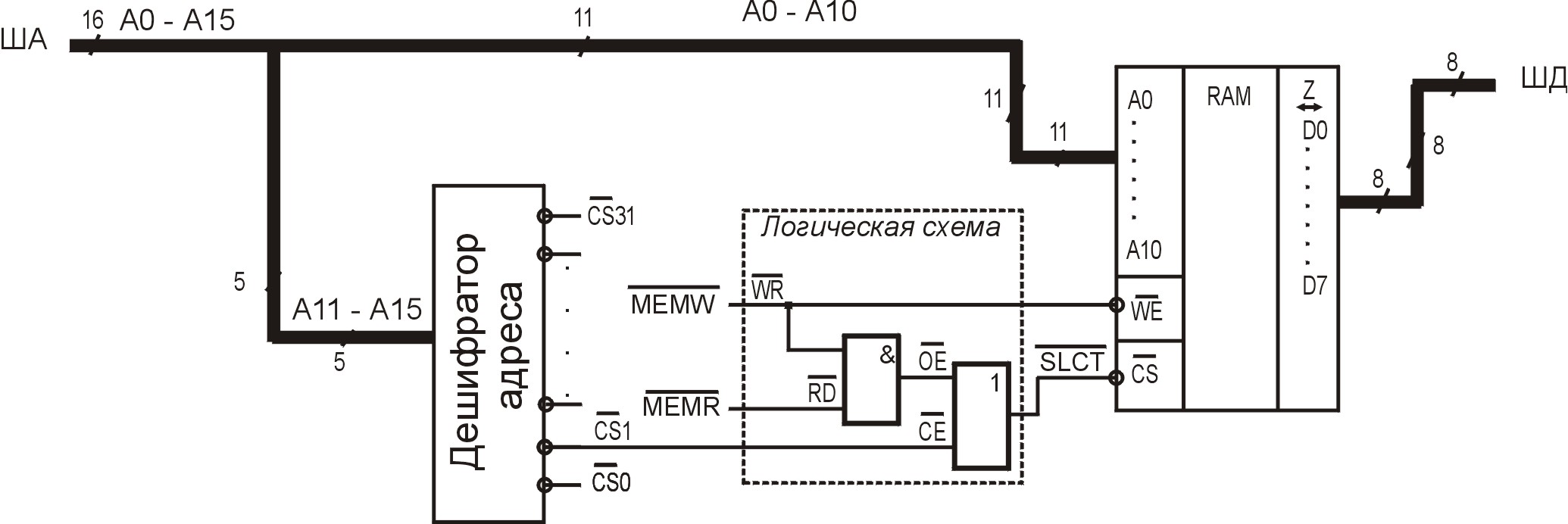

Рассмотренная

выше конфликтная ситуация будет

исключена, если применить логическую

схему на элементах 2ИЛИ и 2И (см. рис.

2.14), которые разрешают работу ИМС ОЗУ

сигналом

![]() лишь в том случае, если

или

,

а также

установлены в «0» (см. таблицу 2.2).

лишь в том случае, если

или

,

а также

установлены в «0» (см. таблицу 2.2).

Таблица 2.2.

Режимы работы

ОЗУ

Сигналы

Z-состояние

0

1

1

1

Чтение

0

0

1

0

Запись

0

1

0

0

Z-состояние

1

Любые значения

1

Рис.

2.12

Рис.

2.13

Рис.

2.14

быстродействием, то моменты времени переключения уровней сигнала , запаздывают относительно . Тогда выход ИМС из Z-состояния произойдет после настройки ОЗУ на прием информации извне. Таким образом прием данных продолжается до тех пор, пока имеет L-уровень.

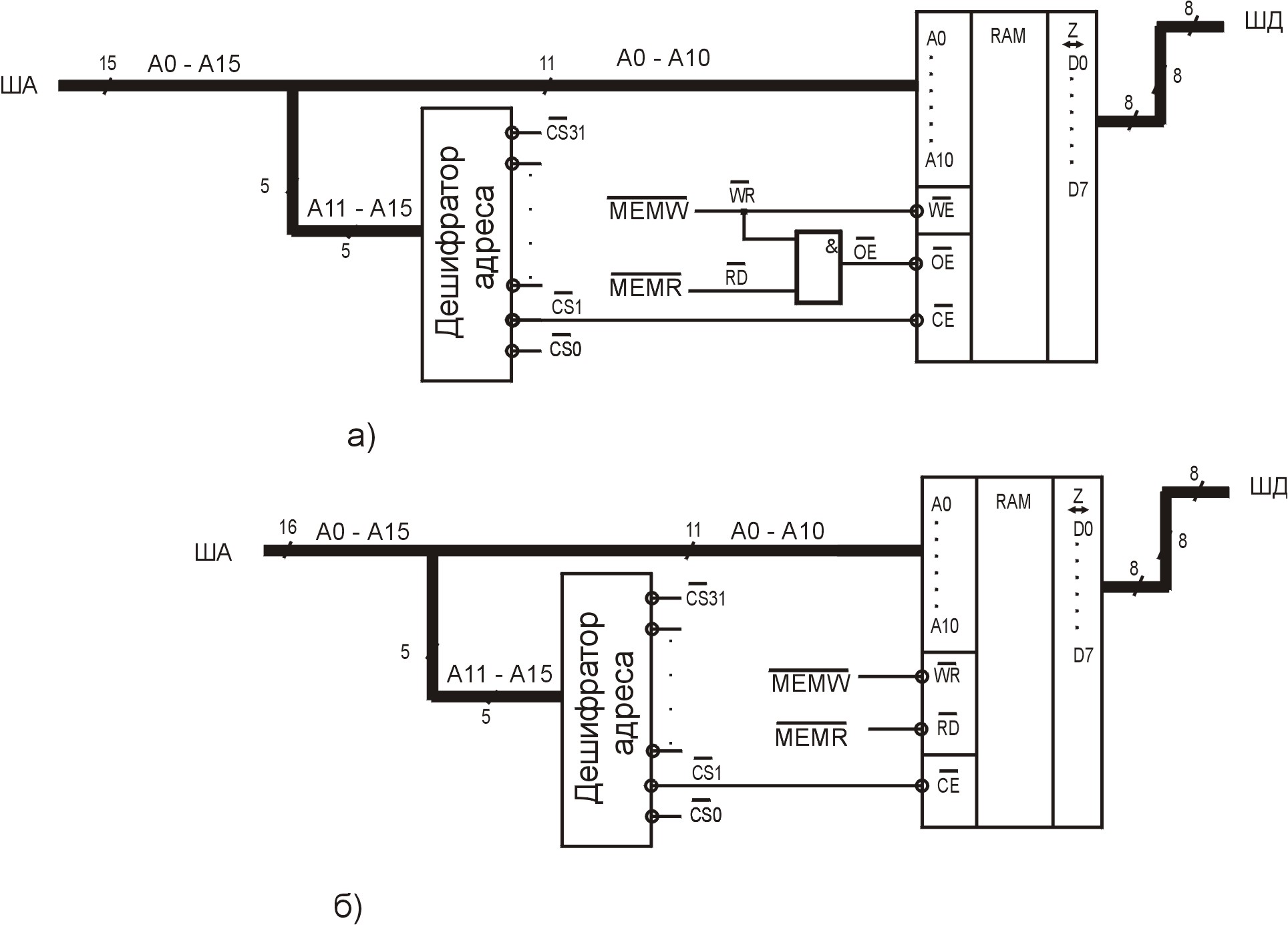

Элементы логической схемы, реализующей бесконфликтный доступ к ОЗУ, у некоторых ИМС могут находиться внутри корпуса. Если ИМС содержит 2ИЛИ, то ее подключение к управляющим сигналам производится только через элемент 2И, как показано на рис. 2.15 а). Микросхемы памяти, заключающие логическую схему целиком, имеют раздельные входы управления чтением и записью данных, обозначаемые соответственно и . Соединение таких микросхем с системными шинами приведено на рис. 2.15 б).

Рис.

2.15

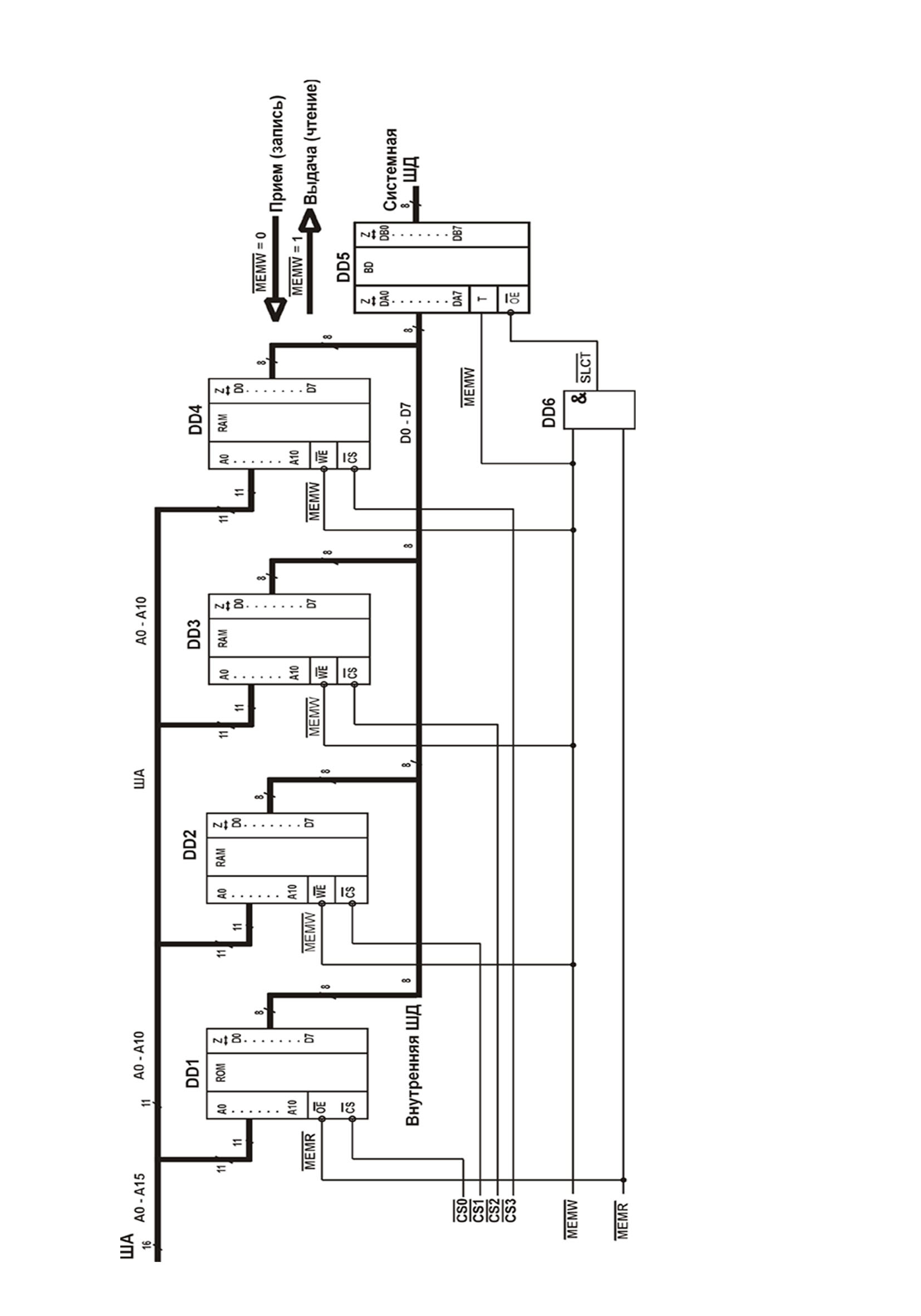

DD1 — ПЗУ;

DD2 — DD4 — ОЗУ;

DD5 — шинный формирователь;

DD6 — логический элемент 2И.

На

этой схеме ИМС ЗУ объединены в блок,

имеющий объем 8 КВ. МПС с 64 КВ памяти

должна содержать 8 таких блоков с

определенными диапазонами адресов. На

рис. 2.16 микросхемы DD1

— DD4 занимают

начало адресного пространства — их

выборка осуществляется по 4 линиям:

—

![]() .

Сигналы на этих линиях может, например,

вырабатывать дешифратор DD2

см. рис.

2.10.

.

Сигналы на этих линиях может, например,

вырабатывать дешифратор DD2

см. рис.

2.10.

Модуль имеет внутреннюю ШД, соединенную с системной ШД через шинный формирователь DD5, переключаемый по управляющему входу Т в режим приема или выдачи данных. Выборка ИМС памяти для любого из этих режимов производится одинаково: ДА вырабатывает сигналы разрешения работы — . При чтении или записи информации в ячейку ИМС, выбранной ДА, формирователь DD5 переключается из Z-состояния сигналом , который вырабатывает элемент 2И как результат логического умножения и . При Н-уровне этих сигналов запретит работу DD5 — в этом случае внутренняя ШД через DD5 будет разъединена с системной. Если же хотя бы один из сигналов или имеет L-уровень, то шинный формирователь переключится из Z-состояния на прием или выдачу данных в соответствии со значением сигнала на входе Т. Таким образом переключение блока в рабочий режим осуществляется только на время действия импульсов синхронизации чтения или записи, чем обеспечивается бесконфликтный доступ к микросхемам памяти (см. п. 1.4.2 — 1.4.4).

Каждая из этих микросхем занимает в адресном пространстве МПС некоторый диапазон адресов, который начинается с базового адреса и заканчивается кодом, указывающим на последнюю ячейку микросхемы. Базовый адрес ИМС DD1 (ПЗУ — см. рис. 2.16) имеет значение 0000h. Очевидно, что код, указывающий на последнюю ячейку этой ИМС, является максимальным смещением относительно базового адреса, и представляет собой двоичное число, выраженное логическими единицами в разрядах А0 — А10 (см. рис. 2.17).

А15... А12

A11

А10

А9

А8

А7

А6

А5

А4

А3

А2

А1

А0

0...0

0

1

1

1

1

1

1

1

1

1

1

1

0

7

F

F

Рис. 2.17

Входы

дешифратора адреса

Адресные входы

ИМС ОЗУ

А15

А14

А13

А12

А11

А10

А9

А8

А7

А6

А5

А4

А3

А2

А1

А0

0

0

0

0

1

0

0

0

0

0

0

0

0

0

0

0

0

8

0

0

а)

Входы

дешифратора адреса

Адресные входы

ИМС ОЗУ

А15

А14

А13

А12

А11

А10

А9

А8

А7

А6

А5

А4

А3

А2

А1

А0

0

0

0

0

1

1

1

1

1

1

1

1

1

1

1

1

7

F

F

0

F

F

F

б) Рис.

2.18

Базовый адрес ИМС ОЗУ DD2, будет определяться кодом на линиях А0 — А15, как показано на рис. 2.18 а). Действительно, на информационные входы А11 — А15 ДА (дешифраторы DD1 и DD2 — см. рис. 2.10) поступают 5 старших разрядов этого кода, десятичным эквивалентом которого является число 1 — номер линии , выбирающей ИМС ОЗУ DD2 (см. рис. 2.16). В этой связи базовый адрес этой ИМС — 0800h. Код смещения определяется также, как и для ПЗУ (см. выше) и соответствует величине 7FFh (см. рис. 2.18 б)). Таким образом, адрес последней ячейки DD2, представляющий собой сумму кодов базового адреса и смещения (см. п.1.4.2), равен числу 0FFFh. Следовательно, диапазон адресов ИМС ОЗУ DD2 начинается с 0800h и заканчивается 0FFFh. Адресные диапазоны остальных микросхем рассчитываются аналогично.

Рис.

2.19

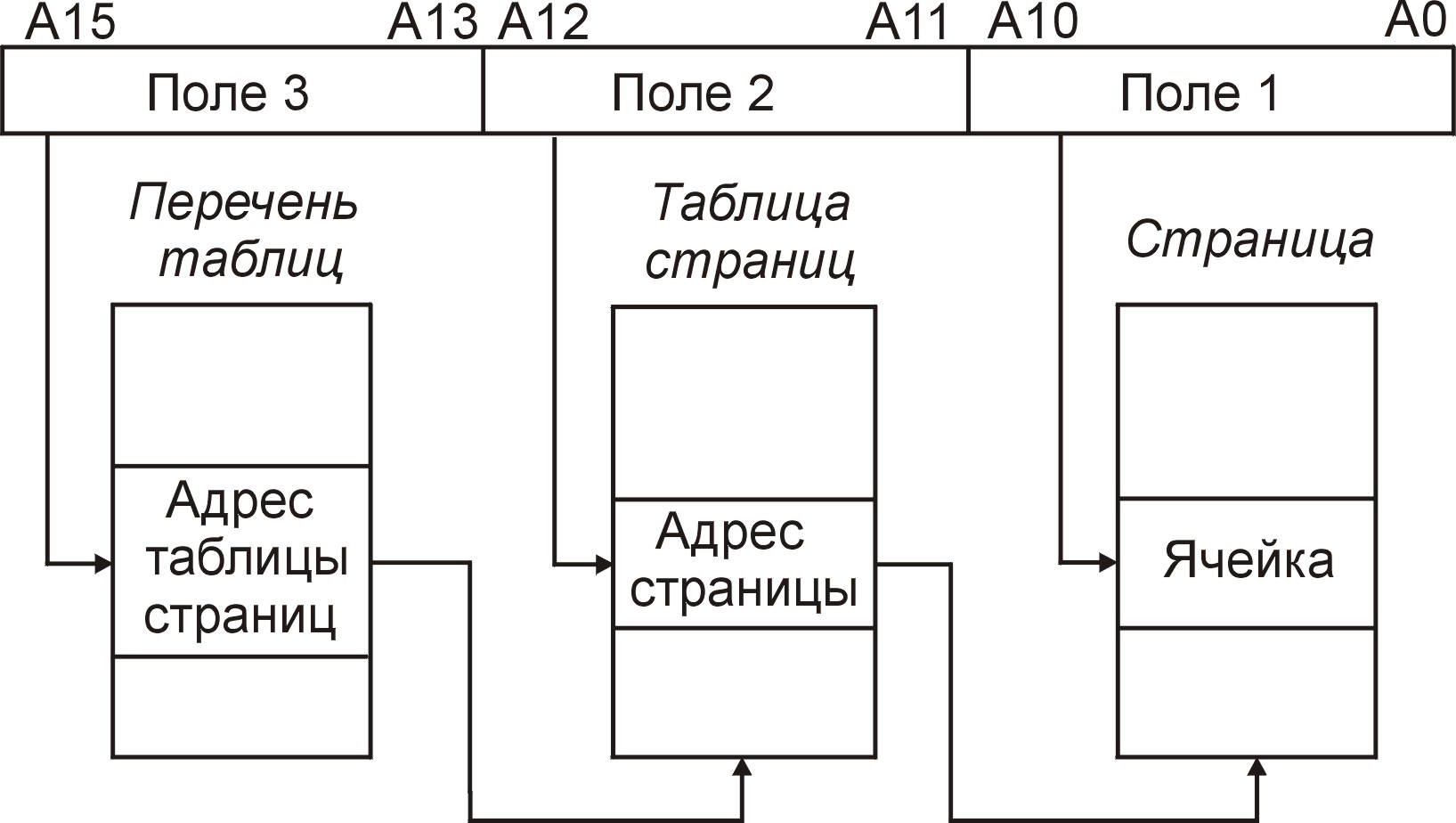

В этой связи существует возможность построения логической модели адресации ячейки, называемой моделью памяти и выражаемой схемой, приведенной на рис. 2. 19. Согласно схеме, 16-разрядный адрес разбит на 3 поля. Поле 1 (разряды А0 — А10 ) содержит код смещения относительно начального адреса страницы, поле 2 (разряды А11, А12) — указатель на таблицу страниц, а поле 3 (разряды А13 — А15) — указатель на перечень таблиц.

Логика адресации выглядит следующим образом. Из перечня таблиц выбирается начальный адрес таблицы страниц, относительно которого указатель, находящийся в поле 2, определяет нужную страницу. Код смещения относительно начального адреса страницы, помещенный в поле 1, непосредственно адресует ячейку памяти.