- •Основы построения микропроцессорных систем

- •Основные определения и общие сведения

- •Типы информационного обмена

- •Параллельный обмен

- •Последовательный обмен

- •Протоколы обмена

- •1.3 Особенности применения цифровых микросхем

- •1.4 Структурные принципы микропроцессорных систем

- •Общая структура

- •Управление чтением и записью

- •Временные диаграммы чтения и записи

- •Подключение памяти и устройств ввода-вывода

- •Типы запоминающих устройств

- •Основные устройства микропроцессорной системы

- •Центральный процессор

- •Микропроцессор

- •Структура

- •Обработка команд

- •Временные диаграммы машинных циклов микропроцессора при чтении и записи

- •Система команд

- •Дешифратор адреса

- •Запоминающие устройства

- •Устройства ввода-вывода

- •Устройство звуковой сигнализации

- •Программируемый параллельный интерфейс

- •Универсальный синхронно-асинхронный приемопередатчик

- •Программируемый интервальный таймер

- •Программируемый контроллер приоритетных прерываний

- •Контроллер прямого доступа к памяти

- •Устройство индикации

- •Развитие архитектуры микропроцессорных систем

- •Технические требования

- •Сегментная модель памяти

- •Непрерывная модель памяти

- •Виртуальная адресация

- •Области оперативной памяти

- •Список литературы

- •Оглавление

- •1. Основы построения микропроцессорных систем 3

- •1. Основные устройства микропроцессорной системы 27

- •1. Развитие архитектуры микропроцессорных систем 76

Контроллер прямого доступа к памяти

При передаче больших массивов информации между ОЗУ и ВУ для уменьшения вычислительной нагрузки на микропроцессор и повышения тем самым скорости обмена ВУ с оперативной памятью необходима пересылка данных без участия микропроцессора. Такой обмен принято называть прямым доступом к памяти (ПДП). Поскольку чтением и записью информации в ОЗУ управляет микропроцессор, то для реализации ПДП необходимо другое устройство, реализующее эти управляющие функции — контроллер ПДП (КПДП). Таким образом, задача КПДП — замещение микропроцессора в организации циклов чтения и записи данных, пересылаемых между памятью и ВУ.

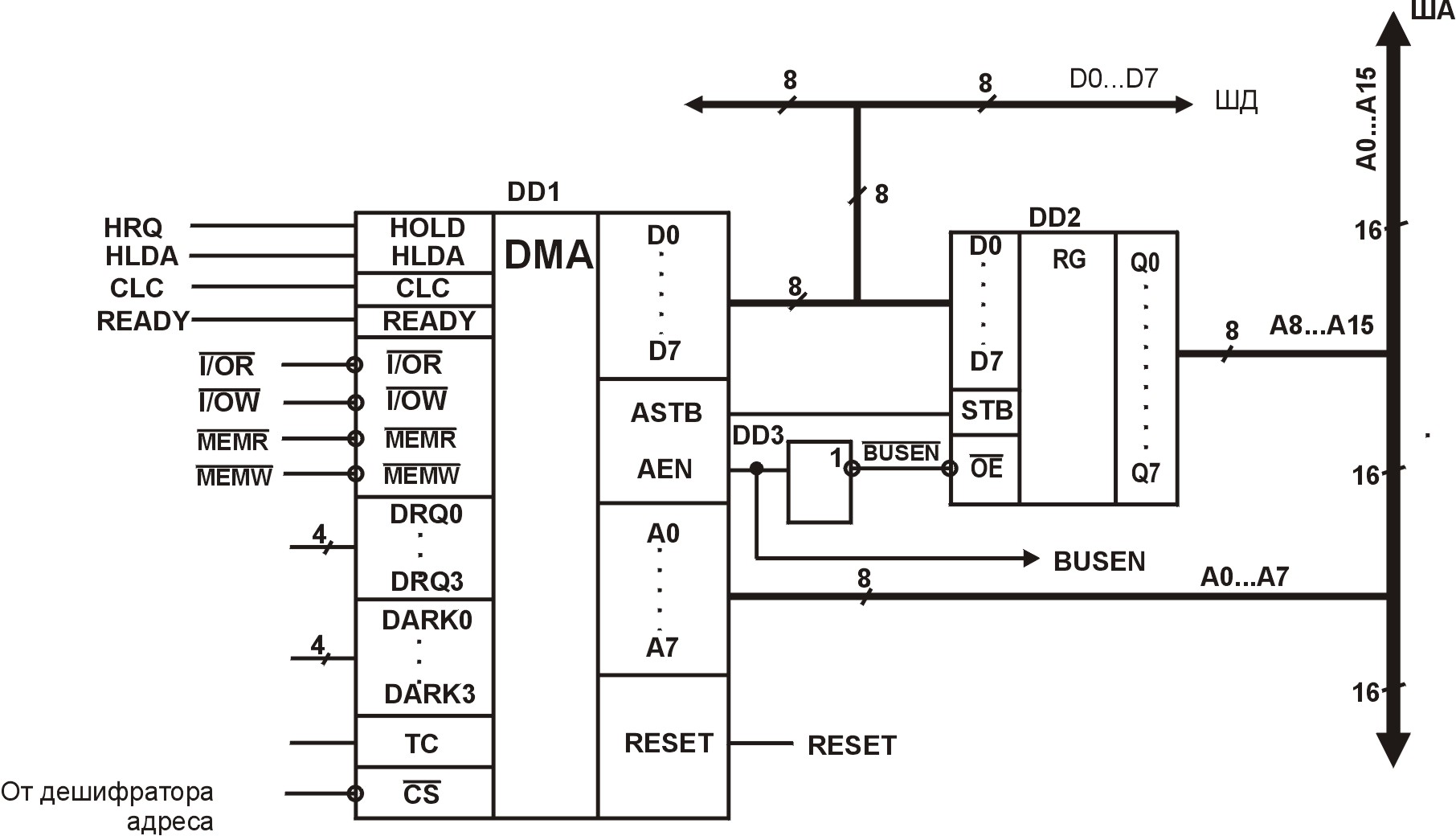

Пример подключения ИМС КПДП к системным шинам МПС приведен на рис 2.27, где обозначено:

DD1 — ИМС КПДП;

DD2 — регистр;

DD3 — логический инвертор.

ИМС КПДП содержит:

каналы ПДП, содержащие регистр адреса ячейки памяти, с которой производится обмен и счетчик циклов обмена;

буфер данных, предназначенный для обмена данными между микропроцессором и КПДП;

схему управления чтением/записью, адресующую внутренние регистры КПДП;

Таблица 2.9

Вывод ИМС

Назначение

HOLD

Запрос ПДП микропроцессору

HLDA

Подтверждение ПДП от микропроцессора

CLC

Вход импульсов тактовой частоты, поступающих от ГТИ микропроцессора (см. рис. 2.1)

READY

Сигнал готовности

Чтение ввода/вывода — тристабильный вход/выход; входное напряжение L-уровня разрешает чтение информации из КПДП; выходной сигнал L-уровня разрешает чтение из ВУ

Запись ввода/вывода — тристабильный вход/выход; входное напряжение L-уровня разрешает программирование КПДП; выходной сигнал L-уровня разрешает запись в ВУ

Чтение из памяти — тристабильный выход; выходное напряжение L-уровня разрешает чтение из ячейки памяти, адресуемой КПДП

Запись в память — тристабильный выход; выходное напряжение L-уровня разрешает запись в ячейку памяти, адресуемую КПДП

DRQ0......DRQ3

Запросы ПДП от внешних устройств

DACK0.....DACK3

Подтверждение ПДП внешним устройствам

TC

Конец счета — напряжение Н-уровня определяет выполнение последнего цикла передачи блока данных

RESET

Вход начальной установки КПДП

ASTB

Выход строба записи части адресного кода в регистр DD2

AEN

Сигнал разрешения работы системных шин

Вход выборки микросхемы КПДП

блок управления, содержащий регистр режима и состояния КПДП и обеспечивающий последовательность операций, необходимую для организации ПДП;блок управления приоритетами, обеспечивающий определенный порядок обслуживания внешних устройств.

Назначение выводов ИМС КПДП приведено в таблице 2.9.

КПДП выполняет следующие основные функции:

получает сигнал внешнего устройства на начало обмена информации в режиме ПДП и формирует соответствующий запрос центральному процессору;

отключает ЦП от системных шин и сообщает внешнему устройству о начале обмена;

Рис. 2.27

формирует адреса ячеек и управляющие сигналы на чтение/запись;задает необходимое количество циклов обмена;

информирует ЦП о завершении цикла обмена и возвращает ему управление системными шинами.

При начальной установке КПДП в регистр режима микропроцессор по команде OUT <номер порта> записывает необходимую информацию. В процессе работы состояние КПДП можно контролировать путем чтения содержимого регистра состояния командой IN <номер порта>.

Работа КПДП осуществляется следующим образом. Запрограммированный на определенный режим работы контроллер ожидает запрос DRQ от ВУ. Если запрос получен, то КПДП вырабатывает для ВУ сигнал подтверждения DACK, а для микропроцессора — HRQ (запрос ПДП) и ожидает выдачи микропроцессором сигнала HLDA (подтверждение ПДП). После получения контроллером подтверждения HLDA начинается цикл обмена данными. В начале обмена КПДП вырабатывает сигнал BUSEN, который запрещает работу ЦП с системными шинами для того, чтобы не произошел конфликт между микропроцессором и КПДП. После этого КПДП вырабатывает код адреса ячейки памяти и сигналы , , , , определяющие направление обмена. Далее КПДП осуществляет необходимое количество циклов обмена данными между памятью и ВУ.