- •Основы построения микропроцессорных систем

- •Основные определения и общие сведения

- •Типы информационного обмена

- •Параллельный обмен

- •Последовательный обмен

- •Протоколы обмена

- •1.3 Особенности применения цифровых микросхем

- •1.4 Структурные принципы микропроцессорных систем

- •Общая структура

- •Управление чтением и записью

- •Временные диаграммы чтения и записи

- •Подключение памяти и устройств ввода-вывода

- •Типы запоминающих устройств

- •Основные устройства микропроцессорной системы

- •Центральный процессор

- •Микропроцессор

- •Структура

- •Обработка команд

- •Временные диаграммы машинных циклов микропроцессора при чтении и записи

- •Система команд

- •Дешифратор адреса

- •Запоминающие устройства

- •Устройства ввода-вывода

- •Устройство звуковой сигнализации

- •Программируемый параллельный интерфейс

- •Универсальный синхронно-асинхронный приемопередатчик

- •Программируемый интервальный таймер

- •Программируемый контроллер приоритетных прерываний

- •Контроллер прямого доступа к памяти

- •Устройство индикации

- •Развитие архитектуры микропроцессорных систем

- •Технические требования

- •Сегментная модель памяти

- •Непрерывная модель памяти

- •Виртуальная адресация

- •Области оперативной памяти

- •Список литературы

- •Оглавление

- •1. Основы построения микропроцессорных систем 3

- •1. Основные устройства микропроцессорной системы 27

- •1. Развитие архитектуры микропроцессорных систем 76

Основные устройства микропроцессорной системы

Центральный процессор

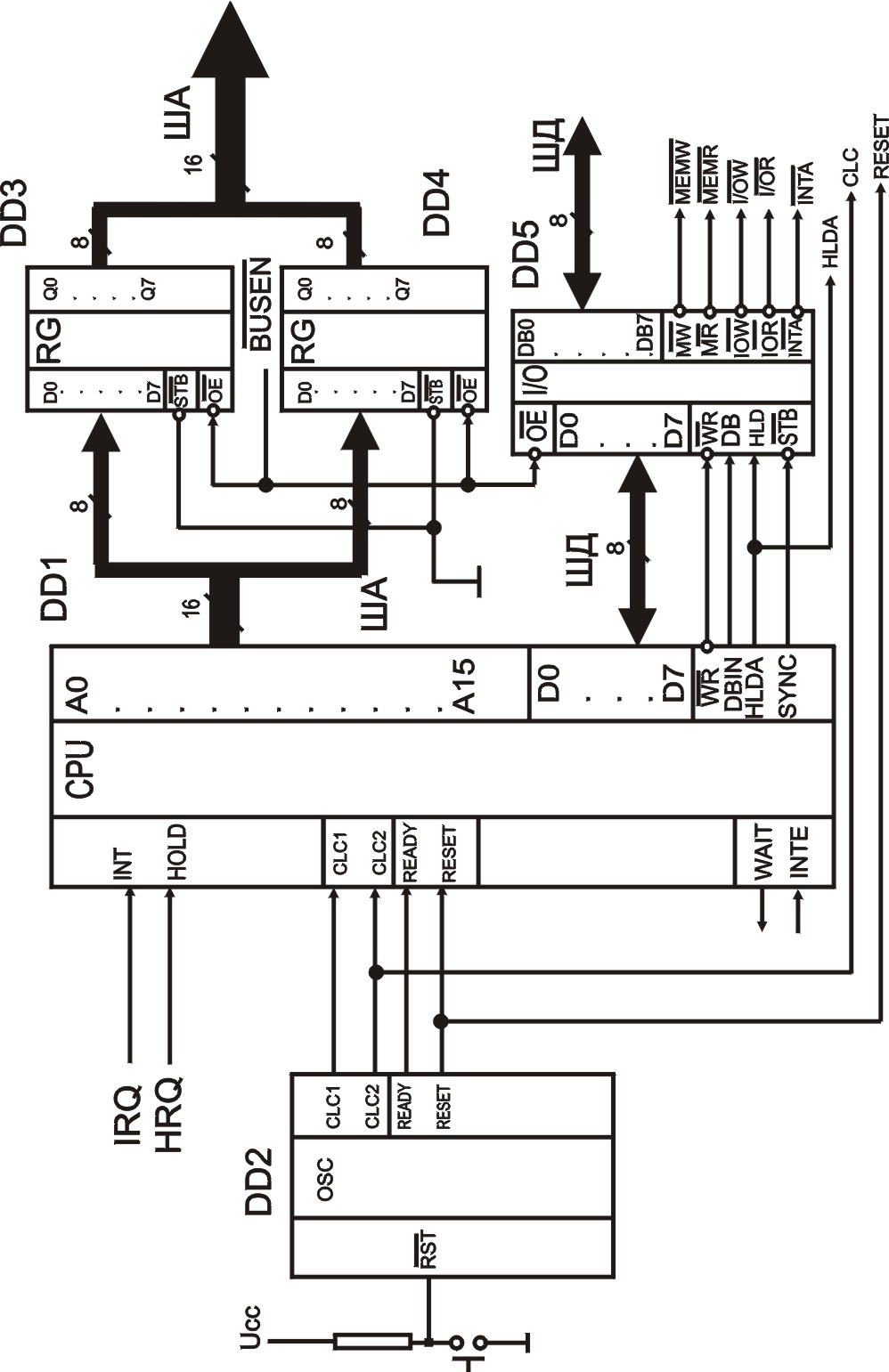

Главные функции по обработке данных и управлению работой других устройств МПС выполняет центральный процессор. Рассмотрим модуль ЦП, построенный на основе одного микропроцессора с 16-разрядной ША и 8-разрядной ШД (16-разрядный микропроцессор). Схема модуля приведена на рис. 2.1, на которой обозначены следующие ИМС:

DD1 — микропроцессор;

DD2 — генератор тактовых импульсов (ГТИ);

DD3, DD4 — регистры-формирователи ША (ФША);

DD5 — системный контроллер-формирователь ШД и части ШУ (СКФ).

ГТИ

вырабатывает синхроимпульсы CLC1,

CLC2 и

предназначен для обеспечения работы

микропроцессора — этими импульсами

осуществляется синхронизация процессов

обработки информации во времени. ФША и

СКФ являются тристабильными ИМС,

повышающими нагрузочную

способность

шин микропроцессора — обеспечивающими

подключение к ним достаточного числа

цифровых устройств со значительным

током потребления, а также позволяющими

отключить от этих устройств микропроцессор

в необходимых случаях по сигналу

![]() (определение сигнала см. ниже). ША и ШД,

соединяющие микропроцессор с

формирователями, называют локальными

шинами,

а те же шины

с повышенной нагрузочной способностью,

к которым подключаются управляемые

микропроцессором устройства —

системными.

(определение сигнала см. ниже). ША и ШД,

соединяющие микропроцессор с

формирователями, называют локальными

шинами,

а те же шины

с повышенной нагрузочной способностью,

к которым подключаются управляемые

микропроцессором устройства —

системными.

ИМС, входящие в ЦП, принимают и выдают следующие сигналы ШУ:

RESET – начальная установка (сброс);

CLC1, CLC2 – сигналы синхронизации;

SYNC – строб синхронизации;

READY – готовность;

–разрешение работы шин;

INTE – разрешение прерываний;

IRQ – запрос прерывания;

– подтверждение

запроса прерывания

– подтверждение

запроса прерыванияHRQ – запрос прямого доступа к памяти (ПДП);

HLDA – подтверждение запроса ПДП;

WR – запись;

DBIN – чтение;

WAIT – ожидание.

Импульсы

синхронизации чтения и записи

![]() ,

и

,

и

![]() ,

,

![]() рассматривались в п. 1.4. Остальные

сигналы, перечисленные выше, их назначение,

а также источники и приемники будут

рассмотрены далее.

рассматривались в п. 1.4. Остальные

сигналы, перечисленные выше, их назначение,

а также источники и приемники будут

рассмотрены далее.

Микропроцессор

Основой ЦП является микропроцессор — программируемая ИМС, непосредственно осуществляющая арифметические и логические действия над данными, а также функции управления устройствами МПС.

Структура

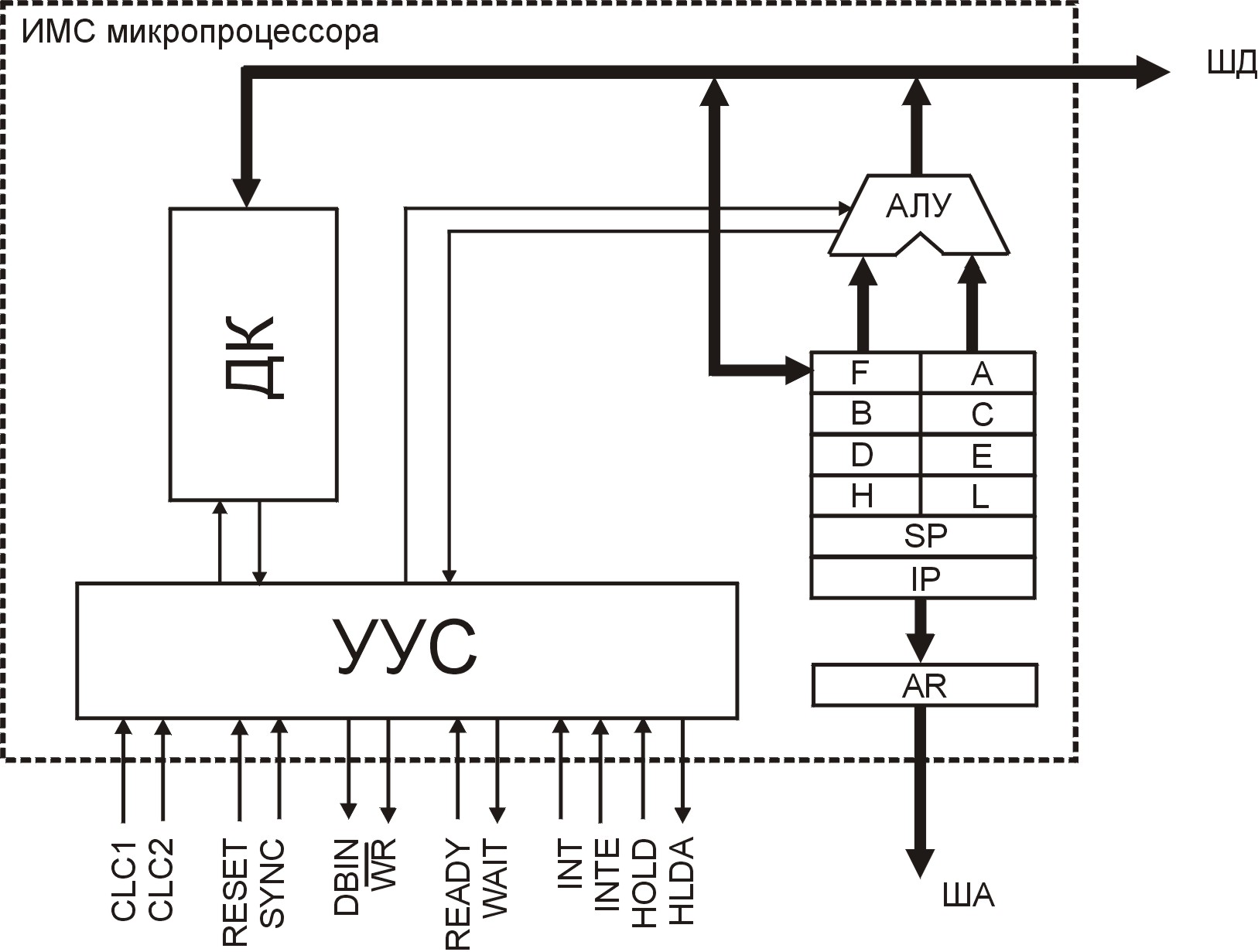

Структура микропроцессора приведена на рис. 2.2, где обозначено:

ДК — дешифратор команд;

УУС — устройство управления и синхронизации;

АЛУ — арифметико-логическое устройство

регистры:

IP — счетчик команд (instruction pointer);

АR — регистр адреса (address register);

SP — указатель стека (stack pointer);

F — регистр признаков результатов операций с данными;

A — аккумулятор;

B, C, D, E, H, L — регистры общего назначения (РОН);

Одним из основных регистров микропроцессора является IP, содержащий адрес ячейки ЗУ или УВВ, с которой осуществляется информационный обмен. Содержимое IP через регистр адреса, выдается на ША. По адресному коду производится выборка нужной ячейки для записи или чтения информации (см. п. 1.4.1).

Из определенных ячеек памяти по ШД микропроцессор считывает команды, указывающие ему действия по обработке данных. Каждая команда представляет собой цифровой код, состоящий из одного или нескольких байтов, формат которого приведен на рис. 2.3. Число байтов называют длиной командного кода или длиной команды. Первый байт команды называют кодом операции — именно он определяет действия с объектами, называемыми операндами. Последними могут быть как сами данные, так и адреса их размещения в памяти. Преобразование кода операции в сигналы, управляющие информационной обработкой, осуществляет дешифратор команд. Эти сигналы могут быть как внутренними, так и внешними, предназначенными другим устройствам. Некоторые внешние сигналы от этих устройств через устройство управления и синхронизации позволяют управлять работой дешифратора команд и АЛУ.

Рис.

2.2

Рис.

2.3![]()

Автоматизация программной обработки данных (организация циклического выполнения нескольких команд, реализация логических условий, осуществляющих переходы в программе, и т.д.) требует учитывать ряд признаков результатов операций в АЛУ, называемых флагами. Каждому флагу соответствует определенный разряд (D0 — D7) регистра F (см. рис. 2.4). Логическая «1» в разрядах этого регистра означает:

CY =1 — перенос из старшего разряда аккумулятора;

Р=1 — число единичных бит в аккумуляторе четное;

АС=1 — в аккумуляторе произошел перенос из разряда D3 в D4;

Z=1 — результат в аккумуляторе нулевой;

S=1 — результат в аккумуляторе отрицателен.

D7

D6

D5

D4

D3

D2

D1

D0

S

Z

-

AC

-

P

-

CY

S

— знак

результата (sign); Z

— бит

нуля (zero); AC

— дополнительный перенос

(auxiliary

carry); P

— четность

(parity); СY

—

перенос(carry).

Рис.

2.4.

Регистры B, C, D, E, H, L могут объединяться в пары в том случае, если число разрядов (разрядность) обрабатываемого числа больше, чем у отдельно взятого регистра. Пары ВС, DE и HL обозначают B, D и Н соответственно. Если результат операции в АЛУ превосходит по разрядности аккумулятор, то последний объединяется в пару с регистром F — этот регистр обеспечивает хранение бита (CY), вытесняемого при переносе из старшего разряда результата. Полное содержимое AF называют словом состояния программы (program status word — PSW).

Регистр SP содержит адрес области ОЗУ, называемой стеком и предназначенной для временного хранения некоторых данных и адресов. Ячейку, которой присвоен начальный адрес названной области, называют вершиной стека. При записи каждого байта в стек содержимое SP всякий раз уменьшается на 1, а записываемые байты образовывают очередь, растущую по уменьшающимся адресам. Чтение данных из этой очереди начинается с адреса, по которому был записан последний байт — в этом случае он считывается первым. При чтении каждого следующего байта содержимое SP увеличивается на 1. Таким образом стек — область ОЗУ, считывание информации из которой осуществляется в порядке обратном записи.