- •Основы построения микропроцессорных систем

- •Основные определения и общие сведения

- •Типы информационного обмена

- •Параллельный обмен

- •Последовательный обмен

- •Протоколы обмена

- •1.3 Особенности применения цифровых микросхем

- •1.4 Структурные принципы микропроцессорных систем

- •Общая структура

- •Управление чтением и записью

- •Временные диаграммы чтения и записи

- •Подключение памяти и устройств ввода-вывода

- •Типы запоминающих устройств

- •Основные устройства микропроцессорной системы

- •Центральный процессор

- •Микропроцессор

- •Структура

- •Обработка команд

- •Временные диаграммы машинных циклов микропроцессора при чтении и записи

- •Система команд

- •Дешифратор адреса

- •Запоминающие устройства

- •Устройства ввода-вывода

- •Устройство звуковой сигнализации

- •Программируемый параллельный интерфейс

- •Универсальный синхронно-асинхронный приемопередатчик

- •Программируемый интервальный таймер

- •Программируемый контроллер приоритетных прерываний

- •Контроллер прямого доступа к памяти

- •Устройство индикации

- •Развитие архитектуры микропроцессорных систем

- •Технические требования

- •Сегментная модель памяти

- •Непрерывная модель памяти

- •Виртуальная адресация

- •Области оперативной памяти

- •Список литературы

- •Оглавление

- •1. Основы построения микропроцессорных систем 3

- •1. Основные устройства микропроцессорной системы 27

- •1. Развитие архитектуры микропроцессорных систем 76

Непрерывная модель памяти

Дальнейшее развитие архитектуры 20-разрядного микропроцессора, а также совершенствование технологии изготовления цифровых ИМС привело к созданию 32-разрядных микропроцессоров. Эти микропроцессоры по-прежнему имели регистры A, F, B, C, D, E, H, L, блок сегментных регистров и сумматор адреса, но их архитектура была дополнена 32-разрядной ША и возможностью работы с особым типом памяти, называемой кэш-памятью (cache memory).

Особенность кэш-памяти состоит в том, что для программ она не представляет дополнительной адресуемой области ОЗУ. Кэш является только дополнительным и быстродействующим устройством хранения копий блоков информации основной памяти, к которым, вероятно, в ближайшее время произойдет обращение микропроцессора. Время доступа к кэш-памяти существенно меньше, чем к динамическому ОЗУ — основному типу оперативной памяти, широко применяемой в МПС по причине малых габаритов микросхем ОЗУ при их значительной информационной емкости. В этой связи существенно повышается скорость обработки информации микропроцессором за счет экономии времени обращения к памяти. Кроме информационных блоков, кэш-память также хранит кэш-каталог (cache directory) — список соответствия этих блоков областям основной памяти. При каждом обращении к памяти специальная микросхема, предназначенная для обеспечения информационного соответствия между кэш и основной памятью и называемая контроллером кэш-памяти, по указанному каталогу проверяет, есть ли действительная копия затребованных данных в cache. Если эта копия есть, то это случай кэш-попадания (cache hit), и обращение происходит только к cache. Отсутствие действительной копии данных означает кэш-промах (cache miss), и данные считываются из основной памяти. В соответствии с алгоритмом кэширования, считанный блок данных, при определенных условиях, заместит один из блоков, хранящихся в cache. Обращение к основной памяти может начинаться одновременно с поиском в кэш-каталоге и прерываться в случае кэш-попадания (архитектура Look Aside). Такой способ экономит время, но лишние обращения к основной памяти приводят к излишнему энергопотреблению. Возможен другой метод обращения, при котором обмен данными с основной памятью начинается только после фиксации кэш-промаха (архитектура Look Through). На это затрачивается, по крайней мере, один такт микропроцессора, но энергопотребление снижается. При малых объемах кэш-памяти (8 — 32 КВ) для повышения производительности информационной обработки часто используется раздельный кэш для команд и данных — Гарвардская архитектура. Существует также Принстонская архитектура, предполагающая общую кэш-память как для команд, так и для данных.

Кроме возможности работы с кэш-памятью 32-разрядные микропроцессоры функционируют в двух режимах:

реальном (real mode);

защищенном (protected mode).

Работа 32-разрядного микропроцессора в реальном режиме осуществляется также, как и 20-разядного. При этом адресуемое пространство не превышает 1МВ несмотря на то, что объем ОЗУ и разрядность ША больше, чем у 20-разрядного микропроцессора. В данном режиме 32-разрядный микропроцессор при обращении к памяти использует сегментную модель, рассмотренную выше.

Рис. 3.3

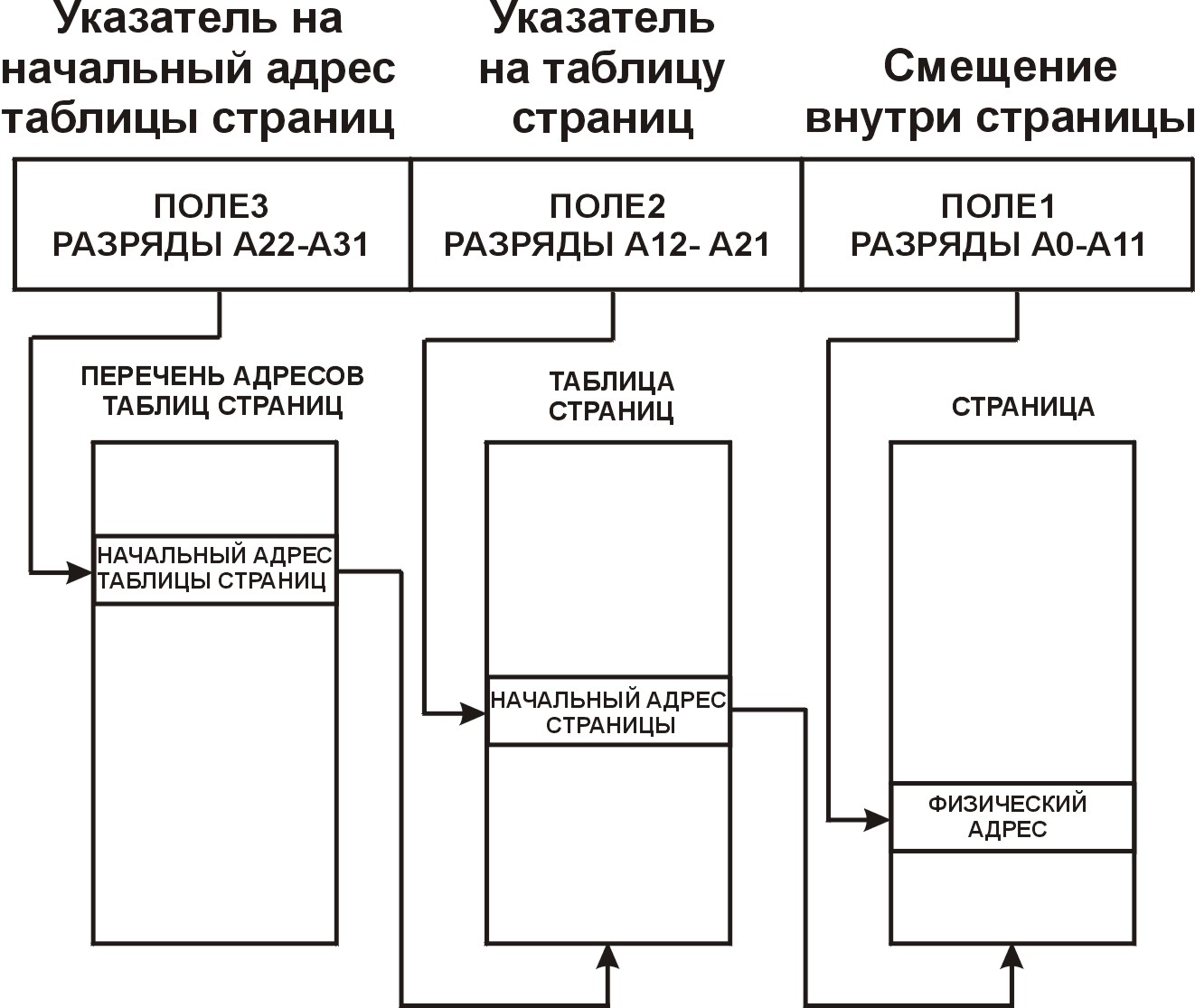

Логика обращения 32-разрядного микропроцессора к ячейкам непрерывной памяти во многом аналогична адресации блока ЗУ в 16-разрядной МПС, как было рассмотрено в п. 2.4. Вся непрерывная память разделена на отдельные участки — страницы. Размер каждой страницы равен 4КВ, в этом случае общее число страниц составит 256. 32-разрядный адрес ячейки памяти разбит на 3 поля (см. рис. 3.3). Поле3 указывает на перечень начальных адресов (таблицу) страниц. Поле2 непосредственно указывает на начальный адрес страницы и занято разрядами с 12 по 21. Поле1 содержит смещение внутри страницы относительно ее начального адреса. Таким образом, адрес ячейки памяти представляет собой сумму начального адреса страницы и смещения.