- •Основы построения микропроцессорных систем

- •Основные определения и общие сведения

- •Типы информационного обмена

- •Параллельный обмен

- •Последовательный обмен

- •Протоколы обмена

- •1.3 Особенности применения цифровых микросхем

- •1.4 Структурные принципы микропроцессорных систем

- •Общая структура

- •Управление чтением и записью

- •Временные диаграммы чтения и записи

- •Подключение памяти и устройств ввода-вывода

- •Типы запоминающих устройств

- •Основные устройства микропроцессорной системы

- •Центральный процессор

- •Микропроцессор

- •Структура

- •Обработка команд

- •Временные диаграммы машинных циклов микропроцессора при чтении и записи

- •Система команд

- •Дешифратор адреса

- •Запоминающие устройства

- •Устройства ввода-вывода

- •Устройство звуковой сигнализации

- •Программируемый параллельный интерфейс

- •Универсальный синхронно-асинхронный приемопередатчик

- •Программируемый интервальный таймер

- •Программируемый контроллер приоритетных прерываний

- •Контроллер прямого доступа к памяти

- •Устройство индикации

- •Развитие архитектуры микропроцессорных систем

- •Технические требования

- •Сегментная модель памяти

- •Непрерывная модель памяти

- •Виртуальная адресация

- •Области оперативной памяти

- •Список литературы

- •Оглавление

- •1. Основы построения микропроцессорных систем 3

- •1. Основные устройства микропроцессорной системы 27

- •1. Развитие архитектуры микропроцессорных систем 76

Развитие архитектуры микропроцессорных систем

Технические требования

Современные технические требования к МПС таковы, что эта система должна иметь следующие атрибуты:

один или несколько микропроцессоров;

единую систему распределения адресов ОЗУ и ПЗУ;

унифицированное распределение адресов УВВ;

систему аппаратных прерываний, позволяющую внешнему оборудованию сообщать МПС о необходимости выполнения определенных процедур;

систему ПДП;

унифицированные интерфейсы ввода/вывода (порты СОМ и LPT, а также порты для подключения клавиатуры и дисковых накопителей);

унифицированные шины расширения (например ISA, а также PCI, AGP и т.д.);

базовую систему ввода/вывода (BIOS) — набор программ, выполняющих тестирование аппаратных средств и начальную загрузку операционной системы, а также обрабатывающих некоторые прерывания и обслуживающих определенные УВВ.

Структурные принципы системной организации современных микропроцессорных аппаратных средств и программного обеспечения во многом основываются на развитии архитектуры МПС, построенной на базе 16-разрядного микропроцессора и рассмотренной в предыдущих разделах. На начальном этапе этого развития была разработана МПС, основу которой составлял микропроцессор с 20-разрядной ША (20-разрядный микропроцессор). Его внутренняя архитектура была во многом аналогична организации 16-разрядного микропроцессора, которая была рассмотрена в п. 2.2.1. Однако по сравнению с 16-разрядной микросхемой новый микропроцессор имел вдвое большую разрядность регистров A, B, C, D, E, H, L, а также следующие дополнительные регистры:

20-разрядный сумматор адреса;

блок регистров, названных сегментными.

Расширение архитектуры 16-разрядного микропроцессора обеспечило возможность адресовать объем памяти до 220 байт, что составляло 1024 килобайта (КВ) или 1 мегабайт (МВ). Для достижения совместимости с программным обеспечением 16-разрядной МПС, а также возможности применения в новой системе ряда широко выпускавшихся промышленностью микросхем ЗУ и УВВ потребовалась организация памяти, названная сегментной моделью.

Сегментная модель памяти

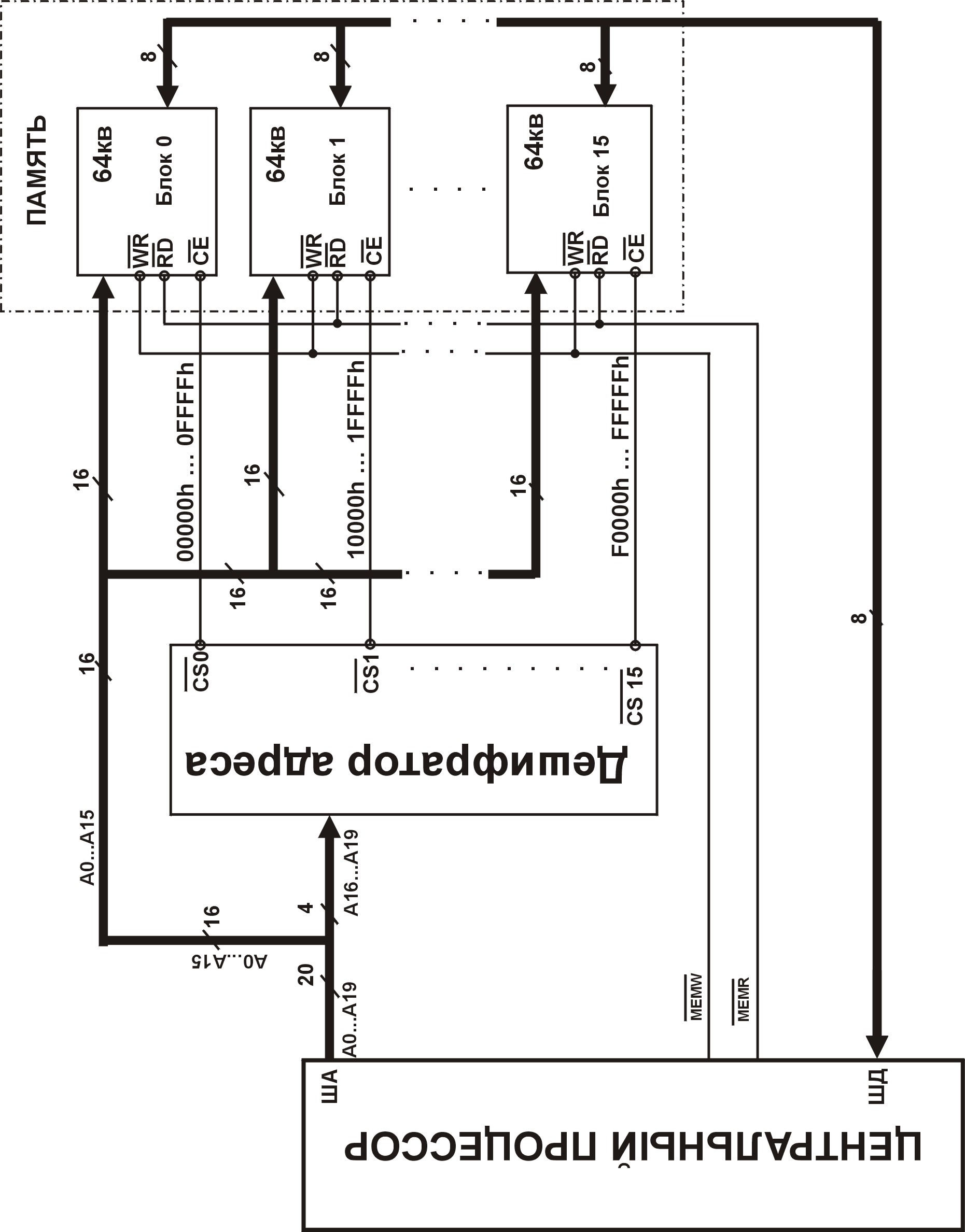

Схема подключения ЗУ к ЦП в 20-разрядной МПС приведена на рис. 3.1. Согласно схеме память в данной МПС организована в 16 блоков, называемых сегментами. Каждый из сегментов имеет информационную емкость 64 КВ (216 байт). Адресация отдельного блока осуществляется с помощью дешифратора адреса, преобразующего код на линиях А16 — А19 в выходные сигналы выборки сегментов памяти.

Системный подход к разработке программного обеспечения МПС предусматривали возможность размещения в блоках памяти следующих программных сегментов, названных логическими сегментами:

кода;

данных;

стека;

дополнительных данных.

Сегмент кода содержал непосредственно команды программы, сегмент данных — данные, сегмент стека — стек, дополнительный сегмент — дополнительные данные. Для адресации этих сегментов программы 20-разрядный микропроцессор имел специальные 16-разрядные сегментные регистры:

Code Segment (CS) — сегмент кода;

Data Segment (DS) — сегмент данных;

Stack Segment (SS) — сегмент стека;

Enhanced data Segment (ES) — сегмент дополнительных данных.

В этих регистрах хранились начальные адреса каждого из четырех перечисленных логических сегментов. Последние могли перекрываться — начинаться с одного и того же адреса. Это означало, что вся программа, содержащая команды, данные и стек размещалась в одном блоке памяти размером 64КВ.

Адреса программных сегментов (кода, данных, стека и дополнительных данных) логически представлялись в форме «сегмент : смещение». Реальный 20-разрядный адрес формировался с использованием сегментных регистров и образовывался двумя 16-разрядными величинами — адресом сегмента и адресом смещения. В пределах любого из сегментов 64К обращение к ячейкам памяти

происходило с помощью 16-разрядного адреса смещения в сегменте, называемого также исполнительным адресом.

Полный 20-разрядный адрес получался путем сложения исполнительного адреса с величиной в сегментном регистре, сдвинутой на 4 разряда влево. Результат сложения, помещенный регистр, названный сумматором адреса, выводился затем на системную ША .

S

S

Дополнение

Код

2

F

8

4

0

hex

0010

1111

1000

0100

0000

bin

a)

Дополнение

S

P

Код

0

0

5

3

2

hex

0000

0000

0101

0011

0000

bin

б)

SS

+

SP

Код

2

F

D

7

2

hex

0010

1111

1101

0111

0010

bin

в)

Рис.

3.2

Следует также отметить, что запись «сегмент : смещение» не является единственным обозначением для указания реального адреса. Например, все следующие логические адреса 0000:0123, 0002:0103, 0008:00А3, 0012:0003 указывают на один и тот же реальный адрес 00123.

С сегментами неразрывно связаны понятия ближней (near) и дальней (far) адресации в программах. При ближнем (внутрисегментном) обращении доступ к требуемой ячейке памяти осуществлялся только указанием смещения, а адрес сегмента определялся текущим содержимым соответствующего сегментного регистра. В программе, использующей дальнее (межсегментное) обращение к памяти, требовалось точное указание как адреса сегмента, так и смещения.

Известно, что долговременное энергонезависимое хранение программ и данных осуществляется не только в ПЗУ, но и в накопителях на гибких или жестких магнитных дисках в виде именованных групп данных — файлах. Также известно, что загрузка программ из накопителя в память и их выполнение осуществляется под управлением программного обеспечения, называемого операционной системой.

Дисковые файлы, содержащие программы, обычно имели либо расширение .COM, либо .EXE. Файл .ЕХЕ до начала программного кода содержал специальную таблицу, по которой операционная система должна была определять адреса загрузки в память логических сегментов. В отличие от .ЕХЕ, файл .СОМ содержал только программный код. Если адреса логических сегментов программы совпадали, то она не могла занимать более 64КВ памяти и использовать дальние обращения. В этом случае операционной системе не требовалось определять различные адреса логических сегментов при загрузке такой программы в память. Поэтому такие программы можно было хранить в файлах, имеющих формат .СОМ. Если же логические сегменты не совпадали, то программа могла использовать как дальние обращения к памяти, так и занимать более 64КВ. Тогда операционной системе уже требовалось определить адреса загрузки сегментов программы по таблице, предшествующей программному коду. Таким образом файлы, содержащие короткие программы с ближними вызовами, могут иметь формат как .СОМ, так и .ЕХЕ. Программы, использующие дальние обращения, а также занимающие в памяти более 64 КВ хранятся в файлах только формата .ЕХЕ.