- •Основы построения микропроцессорных систем

- •Основные определения и общие сведения

- •Типы информационного обмена

- •Параллельный обмен

- •Последовательный обмен

- •Протоколы обмена

- •1.3 Особенности применения цифровых микросхем

- •1.4 Структурные принципы микропроцессорных систем

- •Общая структура

- •Управление чтением и записью

- •Временные диаграммы чтения и записи

- •Подключение памяти и устройств ввода-вывода

- •Типы запоминающих устройств

- •Основные устройства микропроцессорной системы

- •Центральный процессор

- •Микропроцессор

- •Структура

- •Обработка команд

- •Временные диаграммы машинных циклов микропроцессора при чтении и записи

- •Система команд

- •Дешифратор адреса

- •Запоминающие устройства

- •Устройства ввода-вывода

- •Устройство звуковой сигнализации

- •Программируемый параллельный интерфейс

- •Универсальный синхронно-асинхронный приемопередатчик

- •Программируемый интервальный таймер

- •Программируемый контроллер приоритетных прерываний

- •Контроллер прямого доступа к памяти

- •Устройство индикации

- •Развитие архитектуры микропроцессорных систем

- •Технические требования

- •Сегментная модель памяти

- •Непрерывная модель памяти

- •Виртуальная адресация

- •Области оперативной памяти

- •Список литературы

- •Оглавление

- •1. Основы построения микропроцессорных систем 3

- •1. Основные устройства микропроцессорной системы 27

- •1. Развитие архитектуры микропроцессорных систем 76

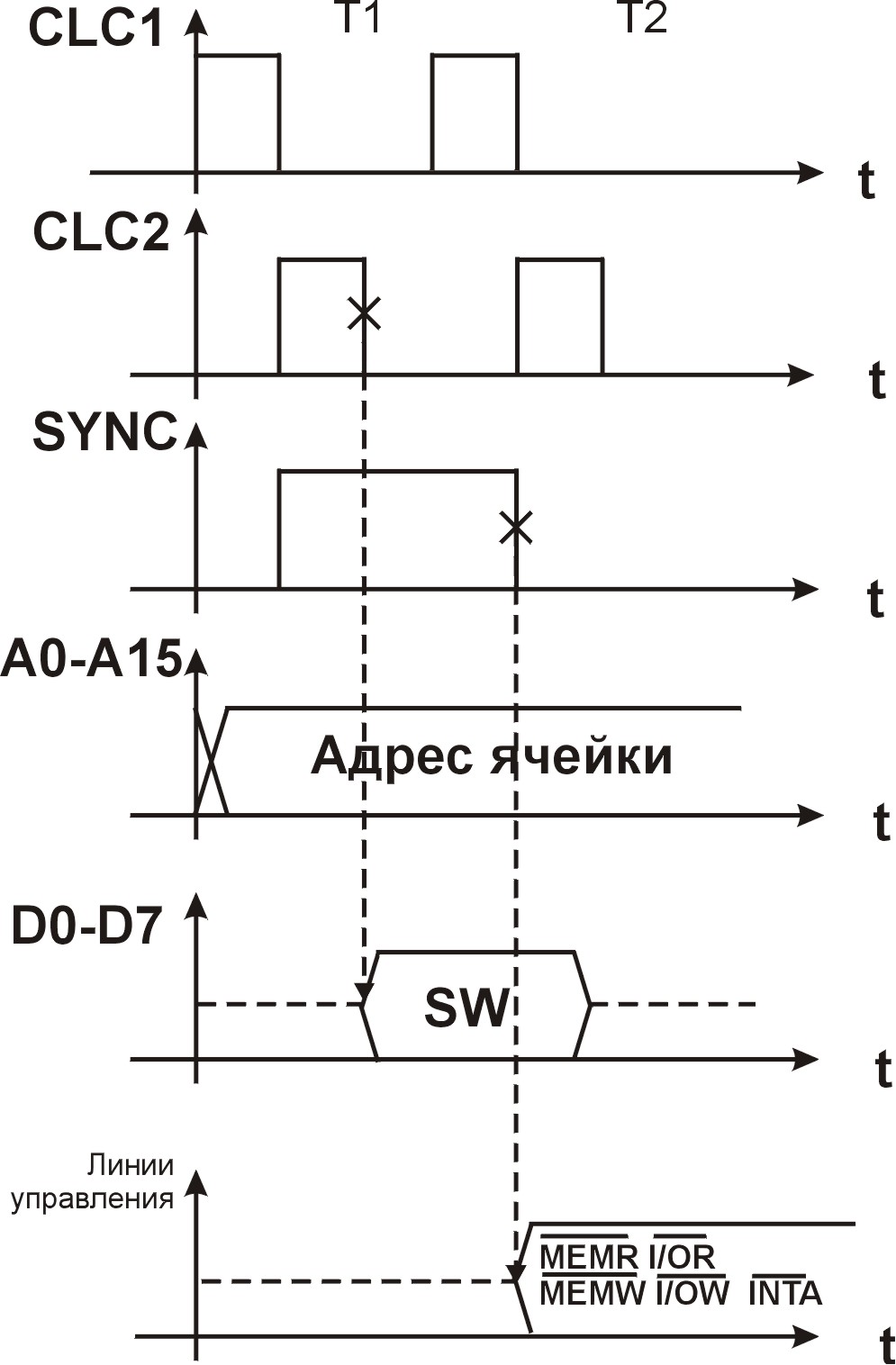

Временные диаграммы машинных циклов микропроцессора при чтении и записи

Эти

диаграммы отображают распределение во

времени процессов чтения и записи данных

на локальных шинах. Управление названными

процессами на этих шинах микропроцессор

осуществляет с помощью двух сигналов:

DBIN

— чтение

и

![]() — запись.

На системных шинах синхронизация чтения

и записи осуществляется уже по четырем

линиям:

— запись.

На системных шинах синхронизация чтения

и записи осуществляется уже по четырем

линиям:

![]() ,

,

![]() ,

,

![]() и

и

![]() (см. п. 1.4). Сигналы на эти линии выдает

СКФ после приема кода SW

(см. таблицу 2.1).

(см. п. 1.4). Сигналы на эти линии выдает

СКФ после приема кода SW

(см. таблицу 2.1).

Временная

диаграмма записи SW

представлена на рис. 2.5. В начале первого

такта (Т1) по сигналу SYNC

SW

записывается во внутренний регистр

СКФ, после чего снимается с локальной

ШД, освобождая ее для передачи информации

— приема микропроцессором команды или

обмена данными с другими устройствами.

В соответствии с SW

комбинационной

схемой, находящейся внутри СКФ, к началу

второго такта (Т2) выдаются сигналы

,

,

,

или

![]() ,

уровни которых определяет тип цикла.

Так при чтении кода команды или данных

из памяти L-уровень

будет иметь сигнал

,

а при чтении информации из УВВ —

и т.д. Назначение сигнала

будет рассмотрено в дальнейшем.

,

уровни которых определяет тип цикла.

Так при чтении кода команды или данных

из памяти L-уровень

будет иметь сигнал

,

а при чтении информации из УВВ —

и т.д. Назначение сигнала

будет рассмотрено в дальнейшем.

Рис.

2.5

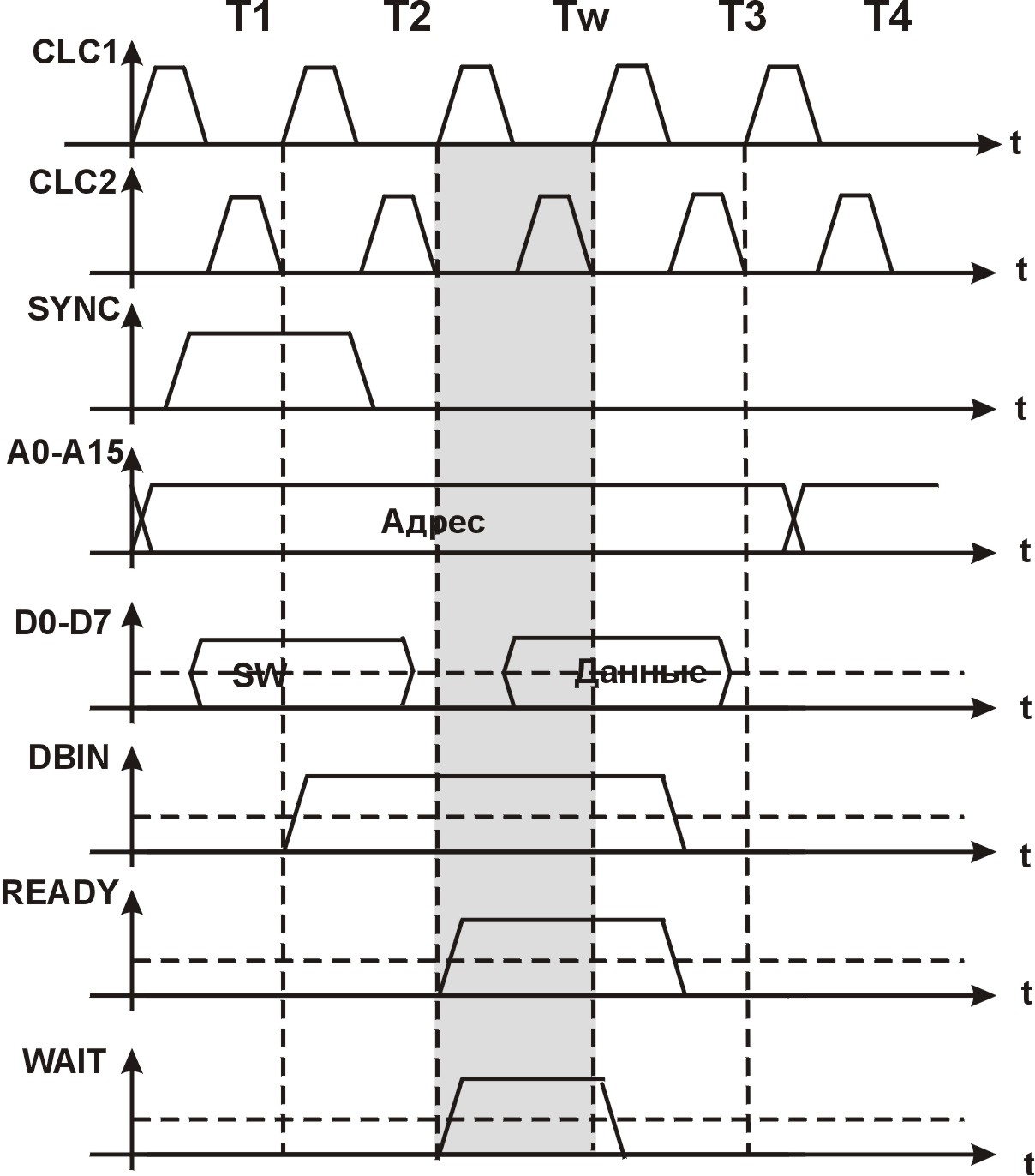

Временная диаграмма цикла чтения приведена на рис. 2.6. Согласно этой диаграмме микропроцессор осуществляет следующие действия:

в такте Т1 выдается:

на ША — адрес ячейки памяти или УВВ;

на ШД — код SW;

Рис.

2.6

Рис.

2.7

на линию SYNC — сигнал SYNC, отмечающий начало машинного цикла и сопровождающий SW;

в такте Т2:

если READY имеет высокий уровень, то производится переход к такту Т3;

если READY имеет низкий уровень, то это означает, что адресуемое устройство не успевает выдать данные на ШД, в этом случае микропроцессор устанавливает сигнал ожидания готовности WAIT и вставляет между тактами Т2 и Т3 такты ожидания ТW;

в тактах ТW анализируется состояние входа READY и если последний имеет высокий уровень (данные появились), то микропроцессор переходит к такту Т3;

в такте Т3 микропроцессором производится считывание данных из памяти или УВВ по сигналам СКФ

или

или

,

момент выдачи которых определяет сигнал

микропроцессора DBIN

(чтение).

,

момент выдачи которых определяет сигнал

микропроцессора DBIN

(чтение).

Последующие такты обычно требуются для внутренних операций микропроцессора.

Цикл записи (см. рис. 2.7) отличается от цикла чтения следующим:

данные для записи выдаются микропроцессором на ШД без задержки после снятия SW;

управляющим сигналом является

,

по которому СКФ выдает

или

,

синхронизирующие запись байта в память

или УВВ.

,

по которому СКФ выдает

или

,

синхронизирующие запись байта в память

или УВВ.

Первым машинным циклом каждого командного цикла всегда является чтение — микропроцессор считывает первый байт команды, содержащий код операции (выборка команды из памяти). Далее, в зависимости от информации, полученной после расшифровки этого кода, осуществляется переход либо к циклу чтения данных из памяти или УВВ, либо к записи информации в эти устройства, а также к останову или обработке прерывания, порядок которой будет рассмотрен далее.