- •Учебная программа дисциплины – Syllabus

- •1. 1Данные о преподавателях:

- •1. 2 Данные о дисциплине:

- •1.5. Краткое содержание дисциплины:

- •1.6. Виды и перечень заданий и сроки их выполнения:

- •Виды заданий и сроки их выполнения

- •1. 7 Список литературы

- •1.8. Система оценки знаний

- •Распределение рейтинговых баллов по видам контроля

- •Календарный график сдачи всех видов контроля по дисциплине «Цифровые устройства и микропроцессоры»

- •Оценка знаний студентов

- •1.9 Политика и процедура

- •2. Содержание активного раздаточного материала

- •2. 1 Тематический план курса

- •Системы счисления

- •Кодирование положительных и отрицательных чисел

- •Алгебраическое сложение чисел с фиксированной запятой

- •Умножение чисел в прямом коде.

- •Умножение чисел в дополнительном коде.

- •Деление чисел с фиксированной запятой

- •Деление двоичных чисел в прямом коде.

- •Деление двоичных чисел в дополнительном коде.

- •Функции алгебры логики (фал).

- •Способы задания фал.

- •Комбинационные схемы и реализация булевых функций.

- •Конечные автоматы

- •Компаратор

- •Триггеры

- •Регистры

- •Счетчики

- •Сумматоры

- •Иерархическая организация зу

- •О рганизация буферных зу

- •Тема лекции 9. Микропроцессоры (мп) и микропроцессорные системы(мпс). Классификация мп и мпс. Структура базового мп

- •Структура базового мп

- •Микропроцессоры

- •Интерфейсы микро-эвм.

- •Озу динамического типа (dram)

- •Тема лекции 13. Архитектура микропроцессоров(мп) и микропроцессорных систем (мпс). Шинная организация ibm pc. Система шин. Передача информации в мпс. Методы ввода/вывода и их классификация.

- •Методы ввода/вывода и их классификация

- •Сигнальные процессоры dsp (цифровая обработка сигналов dsp (digital signal processor) ) представляют собой специализированные процессоры для приложений, требующих интенсивных вычислений .

- •2.3 Наименование тем лабораторные занятия, их содержание и объем в часах (15 часов)

- •2.4. Самостоятельная работа студентов под руководством преподавателя (срсп) (45часов).

- •2.6 Курсовая работа

- •2.7. Тестовые задания для самоконтроля с указанием правильных ответов (не более 30)

- •Коды правильных ответов

- •2.8. Перечень экзаменационных вопросов по пройденному курсу (80 вопросов)

- •Глоссарий

- •Умк дс обсужден на заседании кафедры

Компаратор

Цифровые компараторы

осуществляет сравнение двух двоичных

чисел путем поразрядного их сопоставления.

У компаратора три выхода показывающий

результаты сравнения (больше, меньше

и равно):

![]() –если

два числа между собой равны

(a = b);

–если

два числа между собой равны

(a = b);

![]() –если

(a

> b);

и

–если

(a

> b);

и

![]() если

–

a

< b.

если

–

a

< b.

Работа компаратора описывается следующей логической функцией:

Таблица 5.1.

-

A

b

0

0

1

0

0

0

1

0

0

1

1

0

0

1

0

1

1

1

0

0

Таблица истинности компаратора приведена на табл. 5.1. а схема на рис. 5.4.

Рис. 5.4. Схема одноразрядного компаратора

На ри. 5.4. показана схема реализации одноразрядного компаратора на логических схемах И-НЕ и ИЛИ-НЕ.

Основная литература: 4 [182-199], 7 [51-82]

Дополнительная литература:9 [236-283], 10 [35-61]

Контрольные вопросы:

Назовите основную функцию выполняемую мультиплексором?

Назовите основную функцию выполняемую демультиплексором?

Назовите основную функцию выполняемую компаратором?

В каких случаях демультиплексор называют полным?

Какой функциональный узел используется на управляющих входах мультиплексора?

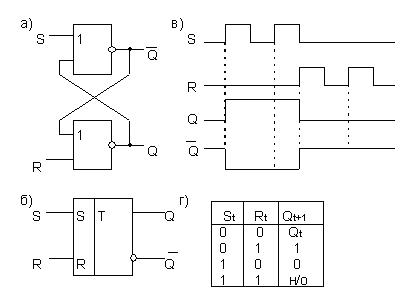

Темы лекций 6. Последовательностные схемы (конечные автоматы). Триггеры. Регистры.

Триггеры

Классификацмя триггеров осуществляется по следующим направлениям:

По методу синхронизации – синхронные и асинхронные:

По базису – на основе схе И-НЕ; - на основе схем ИЛИ-НЕ (см. рис. 6.1.); -на комбинационной основе.

По типу: - RS; D; DV; T; TV; JK.

Структуру триггера можно представить

в виде запоминающей ячейки (ЗЯ) и схемы

управления (СУ). Запоминающая ячейка

представляет собой схему, имеющую два

выхода Q и

![]() ,

сигналы на которых в устойчивом состоянии

всегда противоположны и два входа S и

R. Переключающий сигнал по входу S

(Set-установка) устанавливает запоминающую

ячейку в состояние 1, а по входу R (Reset -

сброс) - в состояние О. Принято, что

триггер находится в состоянии 1, если

на его выходах установлены логические

уровни Q=l и

,

сигналы на которых в устойчивом состоянии

всегда противоположны и два входа S и

R. Переключающий сигнал по входу S

(Set-установка) устанавливает запоминающую

ячейку в состояние 1, а по входу R (Reset -

сброс) - в состояние О. Принято, что

триггер находится в состоянии 1, если

на его выходах установлены логические

уровни Q=l и![]() =0,

в состоянии О триггер имеет логические

уровни Q=0 и

=0,

в состоянии О триггер имеет логические

уровни Q=0 и![]() =1.

=1.

Рис. 6.1. Схема RS-триггера ИЛИ-НЕ и его условное обозначение

В настоящее время в цифровых устройствах применяются несколько разновидностей триггеров, отличающихся количеством и назначением входов, способом записи информаций, организацией логических связей и способом синхронизации и др. По способу записи информации триггеры подразделяются на синхронные и асинхронные. По способу синхронизации различают синхронные триггеры со статическим и динамическим управлением записью. По способу организации логических связей триггеры делятся на RS, JК, Т, D, DV-триггеры. По количеству ступеней бывают триггеры одно- и двухступенчатые. Двухступенчатые триггеры иногда называют MS-схемами (Master-Slave). Рассмотрим схемы триггеров, которые наиболее часто употребляются в цифровых устройствах.

RS-триггеры. Асинхронные RS-тригеры можно построить на элементах ИЛИ- НЕ (рис.6.1) или И-НЕ (рис.6.2).

Рис. 6.2. Схема RS – триггера на схемах И-НЕ и его условное обозначение

Асинхронный RS-триггер на элементах ИЛИ-НЕ имеет два входа (S и R) для раздельной установки состояний О и 1. При подаче единичного сигнала на вход S триггер устанавливается в состояние 1 (при этом Q=l), а на вход R - в состояние О (Q=0). При одновременной подаче сигналов на оба управляющих входа триггер окажется в неопределенном состоянии (Н/О) (рис. 6.1г). Поэтому одновременная подача cигналов на оба входа RS-триггеров запрещается.

При R=S=0 триггер хранит предыдущее состояние, т.е. находится 'в режиме хранения. RS-триггер, построенный на элементах ИЛИ-НЕ (рис. 6.1) переключается в соответствующее состояние в момент перехода управляющих сигналов из 0 в 1, а RS-триггер на элементах И-НЕ (рис.6.2), наоборот, при переходе входных сигналов из 1 в 0. Условные обозначения триггера показаны на рис.6.1и6.2. Здесь знак Т в основном поле означает, что триггер является одноступенчатым. На рис.6.1 в показаны временные диаграммы работы триггеров, поясняющие процесс их переключения.

Для устойчивой работы триггера длительность входного сигнала tc должна быть не меньше времени переключения триггера tТ. Время переключения триггера tT=2tcp, где tср- среднее время переключения логического элемента ИЛИ - НЕ или И - НЕ.

Синхронные RS- триггеры отличаются от асинхронных триггеров дополнительным синхронизирующим или тактирующим входом. Схема синхронного RS-триггера на элементах И-НЕ приведена .на рис. 6.2, и состоит из двух частей - из асинхронного RS-триггера и из схем управления на элементах И-НЕ. Входы R и S являются информационными, а вход С - синхронизирущим.

Запись информации в RS-триггер осуществляется только при наличии единичного сигнала на входе С. При C=0 триггер хранит записанную информацию. Входы Ra и Sa

являются асинхронными, которые служат для асинхронной установки триггера соответственно в нулевое и единичное состояния.

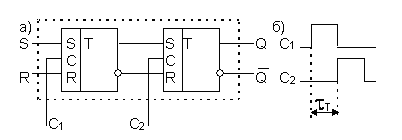

Рис.6.3. Двухтактный триггер

В однотактных триггерах устойчивость работы обеспечивается только в том случае, если занесение очередной информации в триггер осуществляется после завершения передачи информации о прежнем его состоянии в другое устройство. Это требование может быть реализовано с помощьюдвуступенчатыхтриггеров, где запись информации осуществляется с помощью двух синхросигналов.

Базовыми схемами для построения двухступенчатых триггеров являются одноступенчатые RS-триггеры.

Двухступенчатые триггеры содержат две запоминающие ячейки, запись информации в которые осуществляется последовательно в разные . моменты времени, с помощью сигналов С1 и C2 (рис. 3.9). Такая стрятура триггеров в литературе имеет несколько наименований: “ведущий - ведомый", "главный и вспомогательный", MS-структура. Первая ступень - "ведущий" - служит для записи информации в такте t, а вторая - "ведомый" - для последующего запоминания и хранения, начиная с такта автоматического времени t+1. Все двухступенчатые триггеры-являются тактируемыми. Таким образом, у двухступенчатых триггеров формирование нового состояния происходит за два такта. Потому, иногда такие триггеры называют двухтактными.

Рис. 6.4.

Рис. 6.5.

Функциональные свойства всей триггерной

схемы (RS, JK, D и Т-триггеры) определяются

первой ступенью, вторая ступень в

большинстье случаев представляет

синхронный RS-триггер со статическим

управлением, хотя это и не является

обязательным условием. В таких триггерах

ввод информации в ведущую ступень

происходит с приходом тактового импульса

0. Перезапись состояния ведущего триггера

в ведомый осуществляется с приходом

следующего тактового импульса С2. В это

время и происходит обновление информации

на внешних выходах триггера Q и

![]() .

На практике для управления двухступенчатым

триггером используется один и тот же

тактовый импульс (рис. 3.10). При этом

запись информации в первую ступень

происходит во время действия тактового

импульса, а перезапись во вторую ступень

- в момент его окончания. Синхронный

двухступенчатый RS-триггер (MS- структура)

представляет собой схему, состоящую из

двух синхронных RS-триггеров (рис. 3.11) и

инвертора в цепи синхронизации. Здесь

элементы (1-4) образуют ведущий (М) триггер,

а элементы (6-9) - ведомый (5). Тактовый вход

М связан со входом 5 инвертором

(5). По асинхронным входам 5а и Ra триггер

устанавливается соответственно в 1 и 0

состояние без использования синхросигналов.

.

На практике для управления двухступенчатым

триггером используется один и тот же

тактовый импульс (рис. 3.10). При этом

запись информации в первую ступень

происходит во время действия тактового

импульса, а перезапись во вторую ступень

- в момент его окончания. Синхронный

двухступенчатый RS-триггер (MS- структура)

представляет собой схему, состоящую из

двух синхронных RS-триггеров (рис. 3.11) и

инвертора в цепи синхронизации. Здесь

элементы (1-4) образуют ведущий (М) триггер,

а элементы (6-9) - ведомый (5). Тактовый вход

М связан со входом 5 инвертором

(5). По асинхронным входам 5а и Ra триггер

устанавливается соответственно в 1 и 0

состояние без использования синхросигналов.

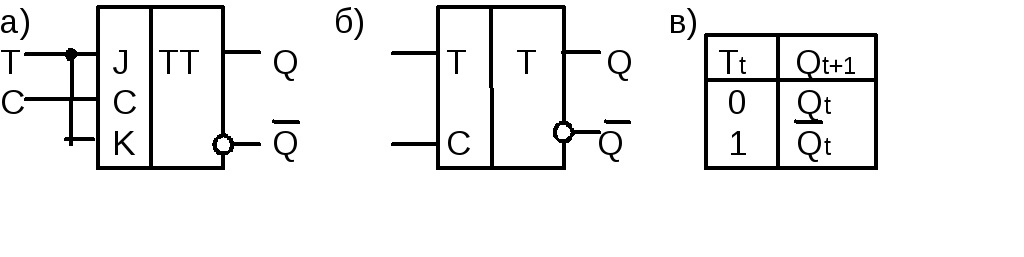

JK и Т-триггеры. В JK-триггере вход J называется единичным установочным входом, а вход К нулевым установочным. В отличие от RS-триггера в JK- триггере допускаются подача входных сигналов J=l и K=l. При этом триггер переключается в состояние, противоположное предыдущему. Таблица переходов JK- 1 триггера приведена на рис 3.12в. JK-триггер можно построить на двух RS - триггерах (рис. 3.12 а).

Рис. 6.6.

![]() на входы эле ментов (1 и 2).

на входы эле ментов (1 и 2).

Синхронный Т-триггер можно получить из JK-триггера путем объединения входов J и К в один, который называется Т- Рис.6.7. входом (счетным входом). Получение Т-триггера из JK- триггера поясняется рис. 3.13а.

Рис.6.8.

Условное обозначение на функциональных схемах показаны на рис. 3.13б. Таблица переходов Т-триггера приведена на рис. 3.13в. При T=0 триггер нахо-дится в состоянии хра-пения информации, а сигнал T=l вызывает переключение триггера в противоположное со стояние.

3.3.3. D-триггеры. Прием информации осуществляется по одному D-входу. С и н х р о н н ы й двухступенчатый D - триггер организован из двух одноступенчатых триггеров (рис. 3.14а). В качестве первой ступени служит синхронный D-триггер со статическим управлением записью, а для второй ступени использован RS-триггер с инверсными входами. Обозначение на функциональных схемах показано на рис. 3.146. Двухступенчатый DV-триггер можно получить из D-триггера путем введения управляющего V-входа, как это показано пунктирной линией на рис. 3.14а. Таблица переходов DV-триггера приведена на рис. 3.14в.