- •Учебная программа дисциплины – Syllabus

- •1. 1Данные о преподавателях:

- •1. 2 Данные о дисциплине:

- •1.5. Краткое содержание дисциплины:

- •1.6. Виды и перечень заданий и сроки их выполнения:

- •Виды заданий и сроки их выполнения

- •1. 7 Список литературы

- •1.8. Система оценки знаний

- •Распределение рейтинговых баллов по видам контроля

- •Календарный график сдачи всех видов контроля по дисциплине «Цифровые устройства и микропроцессоры»

- •Оценка знаний студентов

- •1.9 Политика и процедура

- •2. Содержание активного раздаточного материала

- •2. 1 Тематический план курса

- •Системы счисления

- •Кодирование положительных и отрицательных чисел

- •Алгебраическое сложение чисел с фиксированной запятой

- •Умножение чисел в прямом коде.

- •Умножение чисел в дополнительном коде.

- •Деление чисел с фиксированной запятой

- •Деление двоичных чисел в прямом коде.

- •Деление двоичных чисел в дополнительном коде.

- •Функции алгебры логики (фал).

- •Способы задания фал.

- •Комбинационные схемы и реализация булевых функций.

- •Конечные автоматы

- •Компаратор

- •Триггеры

- •Регистры

- •Счетчики

- •Сумматоры

- •Иерархическая организация зу

- •О рганизация буферных зу

- •Тема лекции 9. Микропроцессоры (мп) и микропроцессорные системы(мпс). Классификация мп и мпс. Структура базового мп

- •Структура базового мп

- •Микропроцессоры

- •Интерфейсы микро-эвм.

- •Озу динамического типа (dram)

- •Тема лекции 13. Архитектура микропроцессоров(мп) и микропроцессорных систем (мпс). Шинная организация ibm pc. Система шин. Передача информации в мпс. Методы ввода/вывода и их классификация.

- •Методы ввода/вывода и их классификация

- •Сигнальные процессоры dsp (цифровая обработка сигналов dsp (digital signal processor) ) представляют собой специализированные процессоры для приложений, требующих интенсивных вычислений .

- •2.3 Наименование тем лабораторные занятия, их содержание и объем в часах (15 часов)

- •2.4. Самостоятельная работа студентов под руководством преподавателя (срсп) (45часов).

- •2.6 Курсовая работа

- •2.7. Тестовые задания для самоконтроля с указанием правильных ответов (не более 30)

- •Коды правильных ответов

- •2.8. Перечень экзаменационных вопросов по пройденному курсу (80 вопросов)

- •Глоссарий

- •Умк дс обсужден на заседании кафедры

Микропроцессоры

Как известно, процессор является основным вычислительным блоком компьютера, в наибольшей степени определяющим его мощь. Процессор является устройством, исполняющим программу - последовательность команд (инструкций), задуманную программистом и оформленную в виде модуля программного кода. Чтобы понять, что делаетпроцессор, рассмотрим его в окружении системных компонентов IBM PC-совместимого компьютера. Этой компьютерной архитектурой, естественно, не ограничивается сфера применения процессоров. Всем известный IBM PC-совместимый компьютер представляет собой реализацию так называемой фон-неймановской архитектуры вычислительных машин. Эта архитектура была представлена Джоном фон-Нейманом еще в 1945 году и имеет следующие основные признаки. Машина состоит из блока управления, арифметико-логического устройства (АЛУ), памяти и устройств ввода/вывода. В ней реализуется концепция хранимой программы: программы и данные хранятся в одной и той же памяти. Выполняемые действия определяются блоком управления и АЛУ, которые вместе являются основой центрального процессора. Центральный процессор выбирает и исполняет команды из памяти последовательно, адрес очередной команды задается "счетчиком адреса" в блоке управления. Этот принцип исполнения называется последовательной передачей управления. Данные, с которыми работает программа, могут включать переменные - именованные области памяти, в которых сохраняются значения с целью дальнейшего использования в программе. Фон-неймановская архитектура - не единственный вариант построения ЭВМ, есть и другие, которые не соответствуют указанным принципам (например, потоковые машины). Однако подавляющее большинство современных компьютеров основано именно на этих принципах, включая и сложные многопроцессорные комплексы, которые можно рассматривать как объединение фон-неймановских машин. Конечно же, за более чем полувековую историю ЭВМ классическая архитектура прошла длинный путь развития. В общем смысле под архитектурой процессора понимается его программная модель, то есть программно-видимые свойства. Сейчас существует множество архитектур процессоров, которые делятся на две глобальные категории - RISC и CISC. RISC - Reduced (Restricted) Instruction Set Computer - процессоры (компьютеры) с сокращенной системой команд. Эти процессоры обычно имеют набор однородных регистров универсального назначения, причем их число может быть большим. Система команд отличается относительной простотой, коды инструкций имеют четкую структуру, как правило, с фиксированной длиной. В результате аппаратная реализация такой архитектуры позволяет с небольшими затратами декодировать и выполнять эти инструкции за минимальное (в пределе 1) число тактов синхронизации. Определенные преимущества дает и унификация регистров. CISC - Complete Instruction Set Computer - процессоры (компьютеры) с полным набором инструкций, к которым относится и семейство х86. Состав и назначение их регистров существенно неоднородны, широкий набор команд усложняет декодирование инструкций, на что расходуются аппаратные ресурсы. Возрастает число тактов, необходимое для выполнения инструкций. Процессоры х86 имеют самую сложную в мире систему команд. Хорошо ли это, вопрос спорный, но груз совместимости с программным обеспечением для IBM PC, имеющим уже 20-летнюю историю, не позволяет расставаться с этим "наследием тяжелого прошлого". В процессорах семейства х86, начиная с 486, применяется комбинированная архитектура - CISC-процессор имеет RISC-ядро. Различают следующие способы организации вычислительного процесса:

один поток команд - один поток данных (Simple Instruction - Simple Data, SISD) - характерно для традиционной фон-неймановской архитектуры (иногда вместо Simple пишут Single);

один поток команд - множественный поток данных (Simple Instruction - Multiple Data, SIMD) - технология MMX;

множественный поток команд - один поток данных (Multiple Instruction - Simple Data, MISD);

множественный поток команд - множественный поток данных (Multiple Instruction - Multiple Data, MIMD).

8-разрядный микропроцессор i8080

На рис. 9.2. представлена внутренняя структура МП i 8080, включающего в себя 8-разрядное АЛУ с буферным регистром и схемой десятичной коррекции, блок РОН, регистры указателя стека SP и счетчика команд PC, первичный управляющий автомат УА, буферные схемы шин адреса и данных и схему управления системой.

Рис. 9.2. Внутренняя структура МП i8080

Внешний интерфейс представлен 8-разрядной двунаправленной шиной данных D[7:0], 16-разрядной шиной адреса A[15:0] и группой линий управления.

Назначение входных и выходных линий МП :

D[7:0]- двунаправленная шина данных служит для приема и выдачи данных, приема команды, приема вектора прерывания, выдачи дополнительной управляющей информации (слово PSW);

A[15:0]- однонаправленная шина адреса служит для выдачи адреса памяти и устройств ввода/вывода;

Ф1,Ф2- сигналы тактового генератора частотой 1..2,5 МГц;

RESET- сброс (начальная установка и запуск программы с адреса 0000);

READY- входной сигнал готовности памяти или ВУ к обмену (обеспечивает асинхронный режим обмена);

INT- запрос внешнего прерывания;

HOLD- захват шины (требование прямого доступа в память со стороны ВУ);

WR- запись - выходной сигнал, определяющий направление передачи информации по шине данныхот процессора к памятиили ВУ;

RD- чтение - выходной сигнал, определяющий направление передачи информации по шине данныхот памяти или ВУ к процессору;

SYNC- выходной сигнал, идентифицирующий наличие на шине данных дополнительной управляющей информации (PSW);

WAIT- выходной сигнал, отмечающий состояние ожидания или останова МП;

INTE- выходной сигнал, подтверждающий режим внешних прерываний;

HLDA- выходной сигнал, подтверждающий режим прямого доступа в память (подтверждение захвата).

Командный цикл микропроцессора

МП работает в составе МПС, обмениваясь информацией с памятью и ВУ. В основе работы МП лежит командный цикл- действия по выбору из памяти и выполнению одной команды. В зависимости от типа и формата команды, способов адресации и числа операндов командный цикл может включать в себя различное число обращений к памяти и ВУ и следовательно - иметь различную длительность.

Любой командный цикл (КЦ) начинается с извлечения из памяти первого байта команды по адресу, хранящемуся в PC, что команды i8080 имеют длину 1, 2 или 3 байта, причем в первом байте содержится информация о длине команды. В случае 2- или 3-байтовой команды реализуются дополнительные обращения к памяти по соседним (большим) адресам.

После считывания команды начинается ее выполнение, причем в процессе выполнения может потребоваться еще одно или несколько обращений к памяти или ВУ (чтение операнда, запись результата).

Для реализации команды i8080 может потребоваться от 1 до 5 обращений к памяти (ВУ). Хотя обращения к ЗУ/ВУ располагаются в разных частях КЦ, выполняются они по единым правилам, соответствующим интерфейсу МПС и реализованы на общем оборудовании управляющего автомата. Действия МПС по передаче в/из МП одного байта данных/команды называются машинным циклом.

Машинные циклы и их идентификация

Командный цикл представляет собой последовательность машинных циклов (МЦ), причем КЦ i8080 может содержать от 1 до 5 МЦ, которые принято обозначать M1, M2,..M5.

МЦ обязательно включает в себя действия по передаче байта информации. Кроме того, в некоторых МЦ дополнительно реализуются действия по пересылке и/или преобразованию информации внутри МП. Поэтому длительность МЦ может быть различной - за счет различного числа содержащихся в них машинных тактов (T1, T2,...).

Машинный такт (такт) образует пара сигналов тактового генератора Ф1, Ф2, поэтому длительность такта постоянна - период тактового генератора (за исключением такта Tw - см. ниже). Таким образом, просматривается иерархия процедур при работе микропроцессора (не только i8080):

Командный цикл Машинный цикл Машинный такт

Каждому такту соответствует определенное состояние управляющего автомата. Любой МЦ i8080 обязательно содержит такты T1, T2, T3, предназначенные для передачи байта по интерфейсу. МЦ, в которых осуществляется передача и/или преобразование информации в МП, содержат дополнительно один или два такта T4, T5. МП i8080 вырабатывает несколько типов МЦ, основными из которых являются циклы ПРИЕМ и ВЫДАЧА

МЦ микропроцессора i8080 предусматривает возможность обмена как в синхронном, так и васинхронномрежиме. Если в составе МПС использованы только "быстрые" устройства, т.е. такие, которые могут работать с тактовой частотой МП, то передача информации в МЦ осуществляется в синхронном режиме. В этом случае на вход READY МП подается константа "1" и после такта T2начинается такт T3. При работе с "медленными" устройствами, быстродействие которых не позволяет переключаться с частотой тактового генератора МП, необходимо "растянуть" во времени МЦ, реализовав асинхронный принцип обмена. Для этого в начале МЦ обмена с "медленными" устройствами на входе READY формируется уровень логического нуля. В такте T2МП анализирует состояние READY, и если READY = 0, то МП после T2переходит не к T3, а к такту ожидания Tw, который может длиться произвольное число периодов тактового генератора. Переход к T3осуществляется по фазе Ф1, если в предыдущей Ф2 READY установился в "1". С помощью входа READY можно не только согласовывать работу МП с устройствами различного быстродействия, но и реализовывать пошаговый и потактовый режимы работы МП.

WAIT

Рис.9.3. Временная диаграмма МЦ "ПРИЕМ "

- выдача адреса;

- выдача информации о начатом МЦ;

-анализ значения входных сигналов;

-при необходимости – ожидание сигнала готовности;

- прием/выдача данных;

- при необходимости – внутренняя обработка/пересылка данных.

При реализации одного МЦ процессор может:

принять из памяти байт команды;

принять из памяти байт данных;

принять из УВВ байт данных;

принять из стека байт данных;

принять вектор прерывания;

выдать в память байт данных;

выдать в стек байт данных;

выдать на УВВ байт данныхю

Дефицит внешних выводов МП не позволяет выводить во внешний интерфейс достататочный для эффективного функционирования объем управляющей информации. Для выдачи более полной информации о состоянии МП в текущемМЦ используется мультиплексированные шины данных. В начале каждого МЦ на линий шины данных D[7:0] выдается байт дополнительной управляющей информации, разряды которого имеют следующее значение:

D0 - подтверждение прерывания;

D1 - запись (в ЗУ) или вывод (на УВыв);

D2 - обращение в стек;

D3 - подтверждение останова;

D4 - вывод (на УВыв);

D5 - M1 (считывание из памяти первого байта команды);

D6 - ввод (из УВв);

D7 - чтение (из ЗУ).

Наличие на D[7:0] управляющей информации отмечается специальным выходным сигналом SYNC.

Байт управляющей информации присутствует на шине данных (ШД) один такт, а использоваться может в течение всего МЦ. Поэтому в МПС, использующих информацию PSW, предусматривается специальный, внешний по отношению к МП, регистр-защелка для фиксации PSW.

Структура и функционирование микропроцессора

Во всём мире широко применяются микропроцессоры фирмы Intelи их аналоги. Эта фирма разработал первый МП, затем целый ряд их семейств и в настоящее время по разным оценкам производит 80-90% от общего мирового объёма выпуска микропроцессоров. При изучении МП целесообразно ориентироваться на конкретные образцы. В данном случае выбран МП К1821ВМ85А - аналог микропроцессораIntel8085A. Это простой для изучения объект, на котором легко проследить основные принципы работы МП. Несмотря на свой многолетний возраст, этот МП до сих пор встречается в каталогах фирм. Естественно, что областью применения подобных микропроцессоров не являются компьютеры, в которых сейчас применяют гораздо более мощные и производительные МП. Простые МП используются в тех системах управления различной аппаратуры, где их возможностей хватает для решения поставленных задач.

Структура микропроцессора К1821ВМ85А

Рис. 9.4. Структура микропроцессора К1821ВМ85А

Структура микропроцессора К1821ВМ85А показана на рис. 9.4

Микропроцессор имеет восьмиразрядную шину данных (внутреннюю), через которую его блоки обмениваются информацией. На схеме приняты следующие обозначения.

AC(Accumulator) – регистр-аккумулятор, выполненный на двухступенчатых триггерах и способен хранить одновременно два слова (один из операндов и результат операции);

TR(TemporaryRegister) – регистр временного хранения одного из операндов;

ALU(Arithmetic-LogicUnit) – арифметико-логическое устройство (АЛУ), выполняющее действие над двумя словами- операндами, подаваемыми на его входы. Аккумулятор служит источником и приёмником данных,TR– источником слова данных, хранимым на время выполнения операции. АЛУ функционирует согласно отношениюA:=A*B, гдеBхранится вTR, второй операнд поступает от аккумулятора, в него же поступает результат операции. АЛУ непосредственно выполняет лишь операции сложения, вычитания, сдвига, сравнения слов, поразрядные логические операции (конъюнкцию, дизъюнкцию, сложение по модулю 2). Более сложные операции (умножение и деление и др.) выполняется по подпрограммам. В АЛУ имеется схема перевода двоичных чисел в двоично-десятичные (DA,DecimalAdjust).

RF(RegisterFlags) – регистр флажок, т. е. битов, указывающих признаки результатов арифметических или логических операций, выполненных в АЛУ.

Указываются паять признаков: Z (Zero) – нулевой результат, C (Carry) – перенос, AC (Auxiliary Carry) – вспомогательный перенос, S (Sing) – знак, P (Parity) – чётность веса слова. Признак вспомогательного переноса ( переноса между младшей и старшей тетрадами восьмиразрядного слова) нужен при выполнении операции в двоично-десятичном коде. Смысл остальных признаков ясен из их наименований. Признаки служат для управления ходом процесса обработки информации.

Блок регистров

С внутренней шиной данных через мультиплексор связан блок регистров, часть которых специализирована, другая часть ( регистры общего назначения, POH) программно доступна и может быть использована по усмотрению программиста. Регистры обозначены черезW,Z,B,C,D,E,H,L,SPиPC. РегистрыWиZпредназначены только для временного хранения данных при выборке команды из памяти и недоступны для программиста. РегистрыB,C,D,E,H,Lотносятся к регистрам общего назначения, т. к. могут быть использованы по усмотрению программиста. Эти восьмиразрядные регистры могут применяться либо по отдельности, либо в виде парB-C,D-E,H-L, играющих роль 16-разрядных регистров. Пары регистров именуются по первым регистрам пары как парыB,D,H.

Пара H-L, как правило, используется для размещения в ней адресов при косвенной адресации. В блоке регистров имеются также 16-разрядные регистрыSPиPC. РегистрSP(StackPointer) - указатель стека. Стек (магазинная память) удобен для запоминания массива слов, т. к. при этом не требуется адресовать каждое слово отдельно. Слова загружаются в стек в определённом порядке, при считывании также заранее известен порядок их следования. В частности, стек удобен при запоминании состояний регистров в момент прерывания программы. Порядок ввода слов в стек и их считывания предопределены его устройством. При организации типаLIFO(LastIn–FirstOut) последнее записанное в стек слово при считывании появляется первым. СтекLIFOпо порядку записи-считывания подобен стопке тарелок – для использования снимается верхняя, т. е. последняя положенная, затем вторая и т. д. Интересно отметить, что сам термин «стек» произошёл именно от обозначения такой стопки.

Стек имеет дно и верхушку, направление возрастания номеров ячеек в нём может быть различным (обычный и перевёрнутый стеки). Операции со стеком – PUSH(запись слова) иPOP(считывания слова).

Аппаратно стек реализуется в ОЗУ, где для него выделяется определённая область. Указатель стека SPсодержит адрес последней занятой ячейки (Рис. 5.6). При выполнении операцииPUSHиPOPзначениеSPуменьшается или увеличивается. Задавая вSPначальное значение, можно размещать стек в той или иной области ОЗУ, следя при этом за тем, чтобы эта область не использовалась для других целей.

Рис.9.5. Реализация стека в микропроцессорной системе.

При байтовой организации памяти и занесении в стек содержимого регистровой пары старший байт запоминается по адресу SP-1, а младший – по адресуSP-2, содержимоеSPуменьшается на 2. При выборке содержимое двух верхних ячеек стека помещается в соответствующие регистры, а содержимоеSPувеличивается на 2.

Основное назначение стека – обслуживание прерываний программы и выполнения подпрограмм.

Программный счётчик PC(ProgramCounter) даёт адрес команды и может обращаться в любую из 64KЯчеек АП. При выполнении операции сброса микропроцессораPCпринимает нулевое состояние, которое, таким образом, является адресом первой исполняемой команды, иначе говоря, выполнение программы начинается с нулевой ячейки. Длина команды составляет 1-3 байта. Содержимое программного счётчика после выборки очередного байта из памяти автоматически инкрементируется, так что вPCпоявляется адрес следующей команды, если текущая команда была однобайтовой, или следующего байта текущей команды в противном случае. Второй и третий байты команды поступают в регистрыWиZ, которые не адресуются программой и используются только блоком внутреннего управления. СхемаINC/DEC(Increment/Decrement) (см. рис. 5.5) изменяет передаваемые через неё слова +1 или -1.

Регистр команд IR(InstructionRegister) принимает из памяти первый байт команды, который после дешифрации порождает сигналы, необходимые для реализации машинных циклов, предписанных кодом операции.

Блок синхронизации и управления.

Этот блок использует выход дешифратора команд и шифратора машинных циклов для синхронизации циклов, генерации сигналов состояния и управления шиной (внешними устройствами микропроцессорной системы).

При обмене между МП и памятью или ВУ адрес соответствующей ячейки памяти или ВУ от выбранной команды или одной из регистровых пар передаётся в регистр адреса RA(RegisterAddress) (см. рис. 5.5). Буфер адреса ВА стремя состояниями выхода выдаёт сигналы старших разрядов адреса на линии адресной шины А15-8. Буфер шины адресов/данныхBA/Dс тремя состояниями выхода передаёт с разделением во времени на шинуADмладший байт адреса или байт данных.

Внутренняя восьмиразрядная шина данных передаёт байты между различными внутренними регистрами или обменивается с другими модулями МПС через мультиплексируемую шину адресов/данных.

Назначение блоков управления прерыванием и последовательным вводом/выводом ясно из их названий. Режимы прерывания и последовательного ввода/вывода подробнее рассмотрены далее.

При естественном следовании команд МП, начав работу, выбирает из памяти и выполняет одну команду за другой, пока не дойдёт до команды ”Останов”(HLT). Выборка и выполнение одной команды образуюткомандный цикл. Командный цикл состоит из одного или нескольких машинных циклов МЦ. Каждое обращение к памяти или ВУ требует машинного цикла, который связан с передачей байта в МП или из него. В свою очередь машинный цикл делится на то или иное число тактовТ, число которых зависит от типа машинного цикла.

Микропроцессор К1821ВМ85А имеет следующие типы машинных циклов:

- Выборки команды (OF, Opcode Fetch).

- Чтения из памяти (MR, Memory Read).

- Записи в память (MW, Memory Write).

- Чтение из ВУ (IOR, Input-Output Read).

- Записи в ВУ (IOW, Input-Output Write).

- Подтверждение прерывания (INA, Interrupt Acknowledge).

- Освобождения шин (BI, Bus Idle).

- Останов (HALT).

В начале каждого машинного цикла генерируются сигналы состояния, идентифицирующие тип цикла и действующие в течение всего цикла

Функции вывода и сигналов микропроцессора.

В этом разделе представлены функции выводов и сигналов микропроцессора Л1821ВМ85А.

А15-8 – Выходные линии с тремя состояниями для выдачи старшего байта адреса памяти или полного адреса ВУ. Переходит в третье состояние в режимах HOLD,HALTиRESET.

AD7-0 – двунаправленные мультиплексированные линии с тремя состояниями для выдачи младшего байта адреса памяти или полного адреса ВУ в первом такте машинного цикла, после чего используется как шина данных. Как видно из сказанного, при адресации ВУ адресная информация обеих полушин (А15-8 иAD7-0) дублируется.

ALE(AddressLatchEnable) – строб разрешения загрузки младшего байта адреса памяти во внешний регистр для его хранения в течении машинного цикла. Появляется в первом такте машинного цикла. Регистр загружается задним фронтом сигналаALE.

R

D,WR– микропроцессорные

сигналы строба чтения и строба записи.

Низкий уровень соответствующего сигнала

свидетельствует о том, что адресованная

ячейка памяти или внешнее устройство

должны выполнить операцию чтения или

записи. Выводы переходят в третье

состояние в режимахHOLD,HALTиRESET.

D,WR– микропроцессорные

сигналы строба чтения и строба записи.

Низкий уровень соответствующего сигнала

свидетельствует о том, что адресованная

ячейка памяти или внешнее устройство

должны выполнить операцию чтения или

записи. Выводы переходят в третье

состояние в режимахHOLD,HALTиRESET.

READY– входной сигнал, показывающий, что память или ВУ готовы к обмену с МП. Если готовности памяти или ВУ нет, МП входит в состояние ожидания, которое может длиться любое число тактов вплоть до появления единичного уровня сигналаREADY.

S1,S0 - сигналы состояния МП, сообщаемые внешней среде. Формируются в начале и сохраняются во время всего машинного цикла.

IO/M– сигнал выбора памяти или внешнего устройства. При высоком уровне происходит обращение к ВУ, при низком – к памяти.

С

овместно

с сигналамиS1,S0

сигналIO/Mидентифицирует тип машинного цикла.

Сигналы состояния и управляющие сигналыRD,WRиINTAдля различных машинных циклов имеют

значения, представленные в таблице 5.1.

овместно

с сигналамиS1,S0

сигналIO/Mидентифицирует тип машинного цикла.

Сигналы состояния и управляющие сигналыRD,WRиINTAдля различных машинных циклов имеют

значения, представленные в таблице 5.1.

-

Тип

МЦ

Сигналы состояния

Сигналы управления

IO/M

S1

S0

RD

WR

INTA

OF

MR

MW

IOR

IOW

INA

BI

HALT

0

0

0

1

1

1

TC*

TC

1

1

0

1

0

1

X

0

1

0

1

0

1

1

X

0

0

0

1

0

1

1

1

TC

1

1

0

1

0

1

1

TC

1

1

1

1

1

0

1

1

В приведённой таблице TCобозначается третье состояние

X

1,X2 – эти выводы присоединяются

к кварцевому резонатору или другим

частотно-задающим цепям для обеспечения

работы внутреннего генератора

синхроимпульсов МП. Частота на выходахX1 иX2 в 2

раза выше рабочей частоты.

1,X2 – эти выводы присоединяются

к кварцевому резонатору или другим

частотно-задающим цепям для обеспечения

работы внутреннего генератора

синхроимпульсов МП. Частота на выходахX1 иX2 в 2

раза выше рабочей частоты.

RESIN(RESETIN) – вход сигнала сброса МП в начальное состояние. Сигнал может поступить в любое время по команде оператора. Автоматически формируется при включении питания. Под его воздействием сбрасываются регистрыPCиIR, триггеры разрешения прерывания, подтверждение захвата и др.

CLK(Clock) – выход синхроимпульсов для микропроцессорной системы. Частота этих импульсов в два раза ниже частоты на выходахX1 иX2

R ESET- выходной сигнал сброса для внешних

модулей системы, привязанный к тактовым

импульсамCLK, т. е.

отличающийся от сигналаRESINпо фазе.

ESET- выходной сигнал сброса для внешних

модулей системы, привязанный к тактовым

импульсамCLK, т. е.

отличающийся от сигналаRESINпо фазе.

I

NTR(InterruptRequest)

– вход запроса векторного прерывания,

вызывающий генерацию стробаINTA,

если прерывание разрешено программой.

Адрес подпрограммы, вызываемой этим

входом, выдаётся внешним устройством.

При сбросе приём сигнала запрещается

(прерывания запрещены).

NTR(InterruptRequest)

– вход запроса векторного прерывания,

вызывающий генерацию стробаINTA,

если прерывание разрешено программой.

Адрес подпрограммы, вызываемой этим

входом, выдаётся внешним устройством.

При сбросе приём сигнала запрещается

(прерывания запрещены).

INTA(InterruptAcknowledge) – микропроцессорный сигналINTAвыход строба подтверждения векторного прерывания после завершения текущего командного цикла. Используется для чтения вектора прерывания.

RST5,5.RST6,5.RST7,5 (Restart) – входы запросов радиального прерывания типаRSTn(n=5,5. 6,5. 7,5.). Начальные адреса подпрограмм обслуживания равны 8n. Приоритеты фиксированы, высший приоритет у входаRST7,5. Приоритеты всей группы запросов выше приоритета запросаINTR. Запросы маскируемые, причём независимо друг от друга.

TRAP– вход запроса немаскируемого прерывания, имеющий максимальный приоритет.

SID,SOD(SerialInputData,SerialOutputData) – вход и выход последовательной передачи данных. По командеRIMвходной бит загружается в старший разряд аккумулятора, по командеSIMвыводится из этого разряда.

HOLD– сигнал запроса захвата шин. Формируется внешним устройством.

H

OLDA(HoldAcknowledge)

– сигнал подтверждения захвата. Является

ответом на сигналHOLD,

формируемым в конце текущего машинного

цикла. Свидетельствует об отключении

МП от системных шин. При этом шины и

линии управляющих сигналовRD,WR,IO/MиALEпереводятся в третье

состояние.

OLDA(HoldAcknowledge)

– сигнал подтверждения захвата. Является

ответом на сигналHOLD,

формируемым в конце текущего машинного

цикла. Свидетельствует об отключении

МП от системных шин. При этом шины и

линии управляющих сигналовRD,WR,IO/MиALEпереводятся в третье

состояние.

Основная литература: 4 [182-199], 7 [51-82]

Дополнительная литература:9 [236-283], 10 [35-61]

Контрольные вопросы:

Принцип организации и архитектура микропроцессора i8080?

Отличие микропроцессора i8086 от микропроцессорi8080?

Состав микропроцессора микропроцессор i8080?

Состав микропроцессора микропроцессор i8086?

Из скольких Машиных циклов состоит процесс записи и считывания ?

Основные функции выполняемые микропроцессором i8080?

Основные функции выполняемые микропроцессором i8086?

Тема лекции 10. Универсальные МП. Организация однокристальных 32-разрядных и 64 разрядных МП.

Организация однокристальных 32-разрядных МП.

Дальнейшим расширением архитектурных возможностей МП явилось создание БИС сопроцессоров, которые работая параллельно и совместно с БИС ЦП, разгружают его от выполнения ряда функций, которые он может выполнять лишь с помощью подпрограмм. К этим БИС относятся:

1) арифметический сопроцессор (80-и разрядный) на два порядка повышающий скорость выполнения высокоточных, операций над числами с плавающей точкой;

2) сопроцессор ввода-вывода осуществляет функции контроллера с двумя каналами прямого доступа к памяти (ПДП), что позволяет выполнять команды ввода-вывода. параллельно с выполнением операций о центральном процессоре (ЦП);

3) сопроцессор ядра операционной системы (ОС), содержащий в кристалле ПЗУ ядро ОС, а также ряд таймеров, буферных устройств и блоки прерывания.

Микропроцессор 80386имеет целый ряд отличий от МП80286, которые значительно расширяют функциональные возможности этой модели:

- дополнительно введен режим "Системы виртуальных машин", при котором пользовательские программы могут выполняться параллельно во времени под управлением разных ОС;

- непосредственный доступ к физическому адресному пространству в 4 Гбайт и виртуальной памяти емкостью 64 Гбайт (около 70 триллионов байт);

- сегментно-страничная организация памяти; - производительность в 2-3 раза выше, чем у МП80286, за счет большей тактовой, частоты, более быстрого доступа к памяти благодаря использованию размещенных на кристалле МП КЭШ (скрытой) - памяти и блока защиты памяти ( в том числе блока быстрого преобразования адресов);

- система команд МП80386 является расширением системы команд МП8086 и МП80286, что обеспечивает программную совместимость с этими моделями (на уровне двоичных кодов программ);

- использование в командах 32-,16-, 8-разрядных операндов; - наличие встроенных средств. самотестирования. запускаемых сигналом сброса и проверяющих примерно 75% всех транзисторов, расположенных, на кристалле.

Микропроцессор INTEL 80386 состоит из центрального процессора, блока управления памятью и шины интерфейса (рис.10.1.).

Рис. 10.1. Структура микропроцессораINTEL 80386

Центральный процессор включает в себя исполнительный блок, содержащий восемь 32-х разрядных регистров общего назначения, которые используются как для вычисления адреса, так и для операций с данными, 64-х разрядный сдвигатель и устройства, используемые для ускорения операций умножения и деления. Устройство обработки команд дешифрует коды операций команд и помещает их в очередь для немедленного выполнения исполнительным блоком. Устройство управления памятью состоит из блока сегментации и устройства замещения страниц или подкачки. Механизм подкачки работает "внизу" и параллелен процессу сегментации, что позволяет управлять пространством физического адреса. Одна страница его составляет 4 Килобайта. Для использования системы виртуальной памяти- МП80386 поддерживает полную восстанавливаемость для всех ошибок на странице сегмента. Память может быть организована в 1 или более сегментов различной длины до 4-х мегабайт.

Блок сегментации обеспечивает четыре уровня защиты устройств и операционных систем друг от друга. Любое задание на 80386 может иметь 16 тыс. 381 сегмент по 4-е мегабайта каждый, т.о. обеспечивается 64-е терабайта виртуальной памяти для каждой задачи.

Для совмещения компьютера с высокоэффективными системами, интерфейс шины МП80386 имеет конвейерную обработку данных. Динамическое резервирование шины данных и прямые сигналы BYTE ENABLE.

МП 80386 работает в двух режимах:

1) режим реальной адресации,

2) режим защищенной виртуальной адресации.

В режиме реальной адресации МП80386 работает как очень быстрый МП8086, но с 32х разрядным расширением. Этот же режим используется для подготовки МП к работе в защищенном режиме.

В режиме защищенной виртуальной адресации обеспечивается доступ к сложному, современнейшему способу управления памятью, а также подкачка (замещения) страниц и других возможностей МП.

МП80386 имеет 32 программно доступных регистра (рис.10.4) в следующих категориях:

1) регистры общего назначения (РОИ),

2) регистры сегментации,

3) регистр флагов,

4) регистры управления,

5) регистры системного адреса,

6) регистр тестов,

7) регистр отладки.

Микропроцессор имеет восемь 32-х разрядных РОИ. Младшие 16 разрядов каждого регистра могут использоваться по отдельности. В свою очередь, младшие 16 разрядов разбиваются на младший (0-7р.) и старший (8-15р.) байты. Индивидуальная доступность байтов РОН обеспечивает дополнительную гибкость для операций с данными.

Регистр указателя команд(IР) представляет собой 32-х разрядный регистр, который содержит смещение следующей команды. Смещение всегда определяется относительно кода сегмента. Его младшие 16 бит называются IР и используются при шестнадцатиразрядной. адресации.

32-х разрядный регистр флажков EFLAGS управляет некоторыми операциями. Младшие 16 разрядов регистра представляют собой регистр FLAGS, который может использоваться при выполнении операций с МП8086. Неопределенные биты регистра являются зарегистрированными и могут быть использованы для специальных целей в последующих версиях микропроцессора. Все флаги младшего байта, регистра устанавливаются арифметическими или логическими операциями МП. За исключением флага переполнения, все флаги старшего байта младшего слова отражают состояние МП и влияют на характер выполнения программ.

Сегментные регистры (шесть 16-и разрядных) содержат базовые адреса сегментов, определяющие сегменты памяти текущей адресации. В защищенном режиме каждый сегмент может иметь размеры до 4 Гбайт, в режиме реальной адресации размер сегмента ограничен до 64 Кбайт.

Регистры дескриптора сегмента невидимы для программиста и соотнесены с каждым видимым регистром селектора. Каждый из них содержит 32-х битовый базовый адрес сегмента, его границу (предел) и другие необходимые признаки сегмента. Когда адрес сегмента загружается в сегментный регистр, ассоциативный (соотнесенный) регистр дескриптора автоматически модифицируется в соответствии с новой информацией. В режиме реальной адресации только базовый адрес модифицируется напрямую, путем сдвига его значения на четыре разряда влево. В защищенном режиме базовый адрес, граница, другие признаки модифицируются содержимым регистра дескриптора сегмента, индексированного селектором.

Три управляющих регистра МП80З86 имеют по 32-а разряда каждый. Это регистры СRО, СR2 и СRЗ. 16 разрядов младшего порядка СRО также известны как "Слово состояния машины" (MSW). Команды LMSW и SMSW используются как для загрузки и хранения в памяти СRО (младшие 16 бит). При работе с ОС МП 80286 старшие 16 разрядов информируются. Новые ОС должны использовать команды для загрузки регистра СRО полностью.

Регистр CR2 содержит 32-х битовый адрес, который определяет наличие ошибки на последней странице. Регистр СRЗ содержит физический базовый адрес таблицы страниц. Таблица страниц в МП 80386 всегда постранично выровнена (т.е. располагается через 4 Кбайта). Поэтому самые младшие 12 бит СRЗ информируются и всегда помещаются в памяти как неопределенные.

Четыре специальных регистра Системного адреса существуют для обращения к таблицам или сегментам GDI, IDI, LDI, ТSS, поддерживаемыми 80286/80366 моделью защиты. Адреса этих таблиц и сегментов помещены в память регистров системного адреса (GDIR и IDTR) и регистров системного сегмента (LDTR и ТR).

Два регистра МП используются для управления и тестирования (RАМ/САМ) в буфере предыстории трансляции. ТR-б-регистр тестирования команд, а ТR-7-регистр данных, который хранит результат тестирования буфера предыстории трансляции.

Прерывания и исключения изменяют нормальное выполнение задачи, чтобы отработать внешние условия, сообщить об ошибках или исключительных обстоятельствах. Различия между прерываниями и исключениями состоят в том, что прерывания обрабатывают синхронные внешние условия, в то время как исключения обрабатывают ошибки команд. Прерывания, произведенные машинным оборудованием, происходят в результате событий и могут быть двух видов: маскируемые и немаскируемые, и выполняются после выполнения текущей команды. После того, как программа обслуживания прерывания заканчивает свою работу, выполнение программы продолжается с команды, которая следует сразу за командой прерывания. МП80386 способен обрабатывать до 256 различных прерываний (исключений). Для обслуживания прерываний необходимо составить таблицу прерываний с 256 векторами прерываний. Вектор прерываний это указатель соответствующей программы обслуживания. Вектор прерываний являются 8-ми байтовыми величинами, которые помещены в таблицу дескрипторов прерываний. Из 256 возможных прерываний, 32 резервированы для использования INTEL, оставшиеся 224 свободны для использования пользователем. В таблице содержится начальный адрес программы обработки прерываний. После этого выполняется вызываемая программа обработки. И наконец, после команды IRET восстанавливается старое состояние процессора и по адресу возврата (сохраненному в стеке) возобновляется выполнение прерванной программы.

Таким образом, огромные функциональные возможности МП80386 полностью определяют функциональные возможности микроэвм в случае, если в качестве центрального процессора в ней будет использован МП80386. Быстродействие такой микроЭВМ будет определяться тактовой частотой МП, специальными средствами ускоренного-формирования физического адреса (Кэш-память) и аппаратурными средствами ускоренного умножения и деления. Использование сегментации и постраничной организации памяти позволяет адресовать виртуальное адресное пространство в 64 терабайта, пространство ввода/вывода состоит из 64 Кбайт, МП80386 способен обрабатывать до 256 различных прерываний. Кроме того этот МП осуществляет самоконтроль, тестирование, отладку, защиту памяти и программ.

Микропроцессор i486

Микропроцессор i486 является представителем второго поколения 32-разрядных микропроцессоров фирмы Intel (США). В отличие от микропроцессора 80386 на его кристалле дополнительно размещены Кэш-память и процессор обработки данных с плавающей точкой (FPU), размещены структура магистрали и протоколы обмена, а также и совершенствована система синхронизации.

Микропроцессор содержит 1,2 млн транзисторов, обеспечивает сверхвысокую производительность, которая составляет 50 млн. операций в секунду для наиболее быстродействующей модели i4B6DX2-66. Следует отметить, что под названием i486 выпускается несколько типов микропроцессоров: i486DX, i486DX2, i486SX. Кроме того, каждый из типов имеет ряд моделей, отличающихся тактовой частотой (33, 40, 50 МГц).

Микропроцессор i486DX2 функционально совершенно аналогичен i486DX и отличается только наличием внутреннего удвоения тактовой частоты (i486DX2 с внешней тактовой частотой 25 или 33 МГц работает с внутренними синхросигналами, имеющими частоту 50 или 66 МГц).

На рис.10.2.приведена структурная схема наиболее распространенного микропроцессора i486DX. Микропроцессор содержит центральный процессор, блок процессора с плавающей точкой, устройство управления, диспетчер памяти, блок предвыборки команд и данных, интерфейс магистрали.

Рис.

10.6

Рис. 10.2. Структурамикропроцессор i486

Центральный процессор включает арифметико-логическое устройство (АЛУ), восемь 32-разрядных регистров общего назначения (регистровый файл) и многоразрядный сдвигатель, используемый при арифметических и циклических сдвигах, операциях умножения и деления. Блок процессора с плавающей точкой обеспечивает обработку данных с плавающей точкой. Он имеет собственные регистры данных и управления.

Устройство управления состоит из дешифратора команд и блока микропрограммного управления, содержащего ПЗУ микропрограмм. Диспетчер памяти (MMU - memory management unit) состоит из блока сегментации и блока страничной адресации.

Диспетчер осуществляет двухступенчатое формирование физического адреса ячейки памяти сначала в пределах сегмента, а затем в пределах страницы. В системе на основе микропроцессора i486 каждой задаче доступны до 16387 сегментов величиной до 4 Гбайт каждый. Следовательно, обеспечивается возможность использования до 64 Тбайт виртуальной памяти для каждой задачи.

Блок предвыборки команд и данных включает устройство предвыборки команд и внутреннюю Кэш-память. Первое осуществляет заполнение очереди команд длиной 32 байта. Внутренняя Кэш-память представляет собой 4-входовую ассоциативную память со стратегией сквозной записи, и имеет несколько режимов работы, обеспечивающих гибкость при выполнении рабочих программ и в процессе отладки.

Интерфейс магистрали реализует протоколы обмена микропроцессора i486 с памятью, контроллерами ввода/вывода, c другими активными устройствами системы обмен осуществляется с помощью 32-разрядной двунаправленной шины данных, 32-разрядной шины адреса и 32-разрядной шины управления.

Шина данных микропроцессора i486 двунаправленная, ее разрядность может изменяться в ходе работы. За один цикл могут быть переданы 8,16 или 32 бита. Шины адреса включают тридцать адресных линий (АЗ1-А2) и четыре линии выбора байтов (BE3#-BEO#). Сигналы выбора байтов определяют, какие байты 32-разрядной шины данных участвуют в текущем цикле обмена. Это позволяет без дополнительной аппаратуры согласовать 32-рязрядную шину данных микропроцессора с байтной организацией памяти системы. Линии адреса АЗ1-А2 являются двунаправленными, адрес вводится в микропроцессоре в циклах закрытия строки Кэш-памяти. Шина управления включает одиннадцать выводов, сигналы которых управляют циклами магистрали, и двадцать один вывод управления состоянием процессора, взаимодействием с другими активными устройствами магистрали.

Организация однокристальных 64-разрядных МП (Pentium).

Одним из наиболее популярных процессоров, разработанных фирмой INTEL, в последнее время стал процессор Pentium. Воздействие процессора Pentium на персональные компьютеры оказывается более сильным, чем переход от старых 16-разрядных микросхем фирмы INTEL к 32-битовым процессором 386 и 486.

В свое время 32-битовая архитектура позволила реализовать в персональных компьютерах оконные среды с мультизадачностью, более высокую производительность и большую память для поддержки графических приложений, автоматизированного проектирования, настольных издательств и мультимедиа.

Высокопроизводительные системы на основе процессора Pentium поднимают персональные компьютеры на более высокий уровень. Обладая достаточной мощностью для реализации функций прежних компьютеров, на основе Pentium разработаны рабочие станции для обработки графической информации, редактирования видеоизображений, сетевых серверов, дисковых серверов и других приложений (cм. табл. 1.1, 1.2, 1.3). Процессор Pentium может работать с операционными системами и средами DOS, UNIX, MS Windows и MS Windows NT. Эта его возможность образует основу универсальной архитектуры компьютеров, доступных пользователям почти любого уровня. Процессор Pentium кроме реального и защищенного режимов имеет режим управления системой (System Management Mode - SMM). Этот режим обеспечивает экономию при работе с другими компонентами системы. Например, в режиме SMM можно задействовать средства экономии энергии токопитания на жестком диске, выключать двигатель при продолжительных периодах бездействия.

Pentium размещен в керамическом корпусе и имеет 273 контакта. Адресная шина процессора имеет 32 разряда, что позволяет адресовать память объемом 4 Гбайт. Тракт данных вдвое больше чем у процессоров 386 и 486 и составляет 64 бита, что при использовании дополнительных средств позволяет значительно повысить производительность (рис. 10.3).

Рис. 10.3. Структура микропроцессора

Pentium

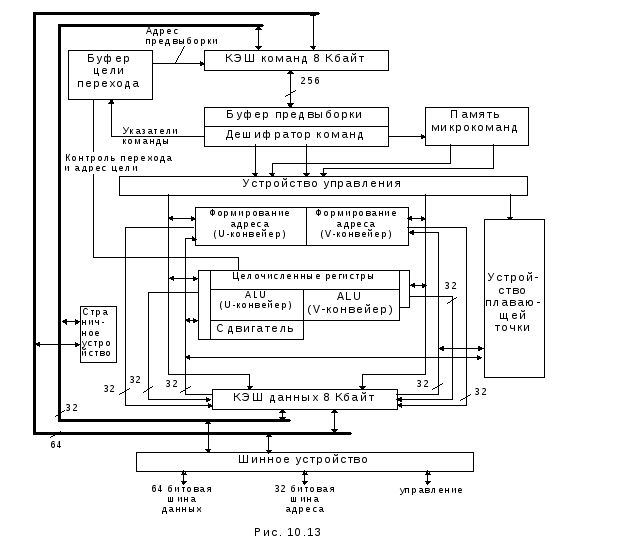

Во всех современных процессорах применяется конвейерный режим, т.е. считывание команды во время выполнения предыдущей команды. В процессоре Pentium конвейерный режим значительно усовершенствован. Повышение производительности достигается за счет суперскалярной архитектуры процессора. Он может выполнять две параллельные команды одновременно, поэтому для выборки команд требуются два конвейера (U - конвейер и V - конвейер). U - конвейер предназначен для выполнения большинства целочисленных команд и команд с плавающей точкой,а V - конвейер - для выполнения простых целочисленных команд и команды FXCH (обмен содержимого регистров) с плавающей точкой. Благодаря параллельному выполнению (или спариванию команд) целочисленные команды в каждом конвейере могут выполняться за один такт синхронизации.

Спаривание команд удваивает быстродействие процессора за исключением того факта, что два конвейера не одинаковы. U - конвейер может выполнять любую команду системы семейства 86, но V - конвейер выполняет только “простые” команды, которые заранее определены, как команды, допускающие спаривание с другими командами. Каждый конвейер состоит из пяти ступеней, действующих по порядку: предвыборка, декодирование команды, формирование адреса, выполнение и запись результата. Для одновременного выполнения обе команды должны классифицироваться как простые. Под ними понимаются команды, полностью встроенные в схемы процессора и не требующие микропрограммного управления. В этом случае обе команды выполняются за один такт синхронизации. Для оптимизации программы программист, изучив список спариваемых команд, должен помещать их рядом. Другим средством процессора Pentium является предсказание перехода и заглядывания вперед. Сам буфер перехода (Branch Target Buffer - BTB) не может правильно предсказать абсолютно все переходы, но точностьперехода или предсказания составляет 90% и большинство переходов выполняется без задержки. Для этого предусмотрено два буфера предвыборки, в которые команды считываются до их фактического выполнения. В результате большинство переходов выполняется за один такт синхронизации и параллельно с другими целочисленными командами.

Для повышения производительности в большинстве современных процессоров применяется внутреннее кэширование. В процессоре Pentium имеется два внутренних кэша по 8 Кбайт для команд и данных. Такое разделение снижает конфликты к кэше, кроме того, процессор знает, куда обращаться за данными, чем при разделении данных и команд “на лету”. Как известно, кэш предназначен для хранения данных или команд, которые не

нужны, но вскоре потребуются. Схема управления в 95% случаев правильно выбирает данные и команды для хранения в кэше. Оба кэша допускают одновременную адресацию, поэтому программа в одном такте синхронизации может извлечь 32 байта команд и произвести два обращения к данным.

Как и процессор 486, процессор Pentium имеет внутренний математический сопроцессор. Однако устройство с плавающей точкой в процессоре Pentium полностью модернизировано, поэтому для таких операций, как сложение, умножение и загрузка, его быстродействие в 10 раз выше.

Режим SMM, упомянутый выше, позволяет системотехникам реализовать системные функции очень высокого уровня, включать управление питанием или защиту, прозрачные для операционной системы и выполняющихся приложений. Средствами этого режима управляет микропрограмма в ROM, которая встроена в схемы процессора. Pentium может перейти в режим SMM из любого другого режима, выполнить необходимые действия и возвратиться в первоначальный режим. Такой переход возможен потому, что Pentium имеет специальную область памяти, называемую RAM управления ситемой (System Managment Random Access Memory -SMRAM), которая применяется для хранения команд программы SMM и сохранения состояния регистров прерванной программы. Одновременно запрещаются все прерывания, которые обычно сбрасывает операционная система или приложение, что представляет программе SMM полное управление системой.

После выполнения программы SMM все возвращается в то состояние, которое было до появления прерывания SMM. Приложение или системная программа возвращаются в точку прерывания.

Наиболее очевидное применение этого средства связано с управлением питания. Программа SMM может перевести процессор или ПУ в пассивное состояние после определенного интервала бездействия и активизировать их при нажатии клавиш или движении мыши. Однако режим SMM может полностью управлять системой, включая управление вводом - выводом и адресацию всех 4 Гбайт RAM.

Основная литература: 4 [182-199], 7 [51-82]

Дополнительная литература:9 [236-283], 10 [35-61]

Контрольные вопросы:

Принцип организации и архитектура микропроцессора i80386?

Отличие микропроцессора i80386 от микропроцессорi80486?

Состав микропроцессора микропроцессор i80386?

Состав микропроцессора микропроцессор i80486?

Основные функции выполняемые микропроцессором Pentium?

Основные функции выполняемые микропроцессором i80486?

Тема лекции 11. Интерфейсы ввод и вывода информации МПС. Последовательная и паралельна передача данных. Прерывание. Прямой доступ памяти.