- •Методичні вказівки до лабораторних робіт і самостійної роботи з курсу Комп'ютерна схемотехніка

- •Загальні положення

- •Лабораторна робота №1

- •Теоретичні відомості.

- •Відомості про навчальний стенд

- •Порядок виконання завдання 1

- •Лабораторна робота №2

- •Теоретичні відомості.

- •Повний дешифратор

- •Аналітичний підхід у проектуванні повних дешифраторів.

- •Неповні дешифратори

- •Порядок виконання завдання 2.1

- •Порядок виконання завдання 2.2

- •Контрольні запитання

- •Лабораторна робота №3

- •Теоретичні відомості.

- •Контрольні запитання

- •Лабораторна робота №4

- •Теоретичні відомості.

- •Порядок виконання завдання 1

- •Контрольні запитання

- •Лабораторна робота №5

- •Теоретичні відомості.

- •Лабораторна робота №6

- •Теоретичні відомості.

- •Порядок виконання завдання 6.1.1.

- •Порядок виконання завдання 6.1.2.

- •Порядок виконання завдання 6.2.1

- •Порядок виконання завдання 6.2.2.

- •Контрольні запитання

- •Лабораторна робота № 7 Проектування та дослідження лічильників

- •Теоретичні відомості.

- •Порядок виконання завдання 7.1.

- •Порядок виконання завдання 7. 2.

- •Контрольні запитання

- •Лабораторна робота №8

- •Теоретичні відомості.

- •2) Спосіб попереднього запису коду.

- •3) Спосіб збільшення модуля на одиницю (від до).

- •4) Спосіб побудови двійково-кодованого лічильника як цифрового автомату.

- •Порядок виконання завдань 8.1-8.3.

- •Контрольні питання

- •Лабораторна робота №9

- •Теоретичні відомості.

- •Рекомендована література

Порядок виконання завдання 1

Ознайомитись з теоретичними відомостями та завданням.

Визначити вимоги до проектованого пристрою.

Використовуючи закони алгебри логіки довести тотожність визначених завданням формул базовим. В якості базових обрати формули 1 або 3 для Si та 2 або 4 для Pi

Розробити схему електричну функціональну суматора.

Скласти перелік логічних елементів, необхідних для реалізації суматора.

Проаналізувати наявну елементну базу, визначити перелік недостаючи елементів та спосіб їх реалізації на наявних елементах.

На базі стандартних елементів мікросхем ТТЛ і ТТЛШ логіки розробити схему електричну принципову проектованого пристрою.

Скласти перелік мікросхем, необхідних для реалізації розробленої схеми.

Отримати у викладача допуск до реалізації розробленої схеми на навчальному монтажному стенді.

Зібрати та налагодити спроектований пристрій згідно розробленої схеми.

Впевнитися в правильності функціонування пристрою. Результати перевірки законів функціонування пристрою оформити у вигляді часових діаграм.

Контрольні запитання

1. Призначення суматора.

2. Однорозрядний напівсуматор.

3. Побудова повного суматора в різних логічних базисах.

4. Повний суматор.

5. Побудова повного суматора в різних логічних базисах.

6. Ознаки суматорів.

7. Паралельні, послідовні та паралельно-послідовні суматори

8. Переваги і недоліки послідовного суматора.

9. Переваги і недоліки паралельного суматора.

10. Переваги і недоліки комбінованого суматора.

11. Послідовне та паралельне формування переносів.

12. Секціонування суматорів (мета, принцип побудови).

Лабораторна робота №5

Проектування та дослідження тригерів як базових елементів схем з пам’яттю.

Мета: Провести дослідження особливостей роботи універсальних тригерів в інтегральному виконанні, вивчити методи проектування тригерів, їх призначення та типи, отримати навички в застосуванні альтернативних способів включення тригерів.

Теоретичні відомості.

(література: 1, c. 96-110;2, с. 85-112;3, с. 170-174;4, с. 590-595)

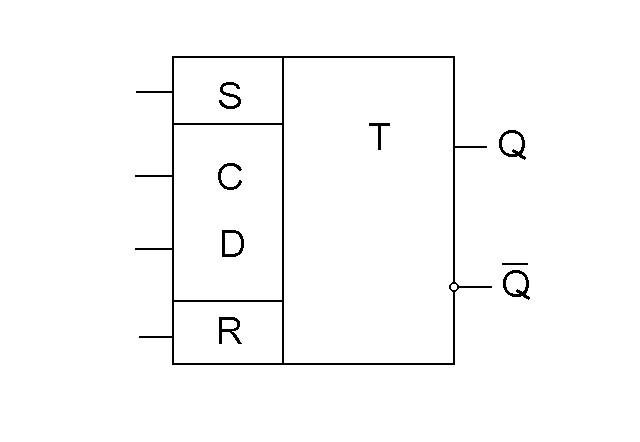

У даний час відома велика кількість різних типів тригерів, що виготовляються у вигляді інтегральних мікросхем. Як правило, це універсальні sid2427501 тригери, тобто тригери, що суміщають в собі функціональні можливості декількох простіших видів тригерів (наприклад: RS- і D- тригерів, RS- і JK- тригерів і т.д.). Так, наприклад, тригер, зображений на рисунку 5.1, поєднує в собі можливості RS- і D- тригерів.

Рисунок 5.1 - D-тригер з додатковими прямими входами RS-тригера і потенційним входом синхронізації

Запис інформації в D-тригер проводиться по входу D. Для визначення моментів запису інформації на вхід С подаються імпульси синхронізації.

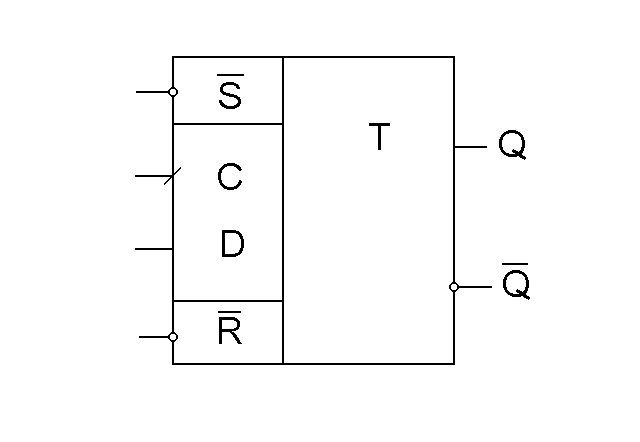

Вхід синхронізації С може бути як потенційним (рис. 5.1), так і динамічним (рис. 5.2).

Рисунок 5.2 - D-тригер з додатковими інверсними входами RS-тригера і динамічним входом синхронізації

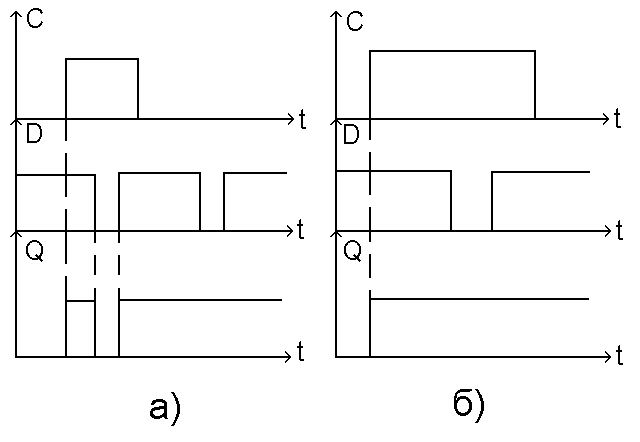

Особливості роботи тригерів з потенційним і динамічним входом синхронізації С відображені на часових діаграмах (рис.5.3.а і рис.5.3.б відповідно).

Рисунок 5.3 - Часові діаграми роботи D-тригера з потенційним (а) і динамічним (б) входом синхронізації С

Як випливає з рисунку 5.3.а, запис інформації у тригер з потенційним входом синхронізації (рис. 5.1) відбувається за наявності на вході С рівня логічної “1”. При цьому зміна стану тригера пов'язана з надходженням сигналів на вхід D.

Як випливає з рисунку 5.3.б, в динамічному тригері (рис.5.2) запис інформації відбувається по позитивному фронту сигналу на вході С (перехід із стану “0” в стан “1”). Існує тип тригерів, у яких запис інформації здійснюється по негативному фронту сигналу на вході С (перехід із стану “1” в стан “0”).

Крім входу D і С, розглянуті тригери мають вхід установки “0” (R - вхід) і вхід установки “1” (S - вхід).

Для управління роботою тригера можуть використовуватися управляючі сигнали різних рівнів. Так, вищезгаданий тригер (рис. 5.1) спрацьовує при подачі на входи S і R сигналів логічної “1” (прямі входи). При управлінні сигналом логічного нуля “0” вводиться спеціальне позначення інверсного входу мікросхем (рис.5.2). Відповідно, цей тригер (рис. 5.1) спрацьовує при подачі на входи S і R сигналів логічної “0” (інверсніі входи).

Роботу тригера, як і інших логічних пристроїв, можна описати за допомогою таблиці істинності. Таблиця істинності тригера з потенційним входом (рис.5.1) має вигляд, представлений нижче (табл.5.1).

Таблиця 5.1

|

S |

R |

D |

С |

Qn |

Режим роботи |

|

0 |

0 |

0 |

0 |

0 |

Зберігання інформації |

|

1 0 1 0 0 1 |

0 1 1 0 0 0 |

х х х 1 0 0 |

0 0 0 1 1 1 |

1 0 ? 1 0 1 |

Установка “1” Установка “0” Заборонена комбінація Запис “1” Запис “0” Див. в тексті п.2.4.4 |

Примітка: Позначка «х» в таблиці істинності означає, що сигнал може бути довільним (“0” або “1”), оскільки його значення за зазначених у відповідному рядку таблиці умов не впливає на характер спрацьовування тригера.

Режим “зберігання інформації” означає, що тригер знаходиться в стані, відповідному попередньому такту роботи (управляючі сигнали, що призводять до зміни стану тригера, відсутні).

У

режимі “Установка “1” і “Установка

“0” універсальний тригер функціонує

як стандартний RS-тригер. Комбінація

вхідних сигналів R = S = 1 є забороненою,

оскільки при цьому обидва виходи тригера

встановлюються в один стан

![]() ,

що суперечить нормальній роботі

логічного пристрою.

,

що суперечить нормальній роботі

логічного пристрою.

У режимі “Запис “0” і “Запис “1” універсальний тригер функціонує як стандартний D-триггер.

Останній рядок в таблиці 5.1 ілюструє ситуацію, коли, з одного боку, проводиться запис “0” по входу D, а з другого боку - установка “1” по входу S. В цьому і подібних випадках тригер підкоряється сигналам на настановних входах R і S.

Якщо тригер має динамічний вхід синхронізації С (як це показано на рис. 5.2), то в таблиці істинності для позитивного і негативного фронту вводяться спеціальні позначення (“↑” або “ ” для позитивного і “ ↓ ” або “ ” для негативного фронту відповідно).

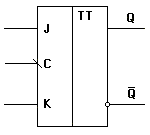

Особливістю тригерів як елементів цифрової схемотехніки є можливість реалізації схем включення тригерів одного типу для їх застосування в якості тригерів іншого типу. Найбільша кількість альтернативних варіантів включення передбачена для J-Kтригерів, через що їх також називають універсальними тригерами. На рисунках 5.4-5.7 наведені деякі типові альтернативні схеми включенняJ-Kтригерів.

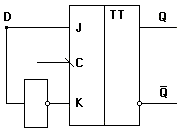

Рисунок 5.4 – Схема включення універсального J-K тригера в якості синхронного R-S-тригера

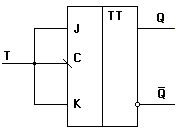

Рисунок 5.5 – Схема включення універсального J-K тригера в якості синхронного D-тригера

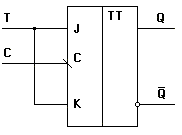

Рисунок 5.6 – Схема включення універсального J-K тригера в якості асинхронного Т-тригера

Рисунок 5.7 – Схема включення універсального J-K тригера в якості синхронного Т-тригера

Завдання 5.1.

На базі стандартних елементів мікросхем ТТЛ і ТТЛШ логіки розробити тригер із заданими характеристиками. Змакетувати спроектований тригер на навчальному стенді і провести дослідження реалізованої схеми. Навести таблицю переходів (істинності) спроектованого тригера та часові діаграми його роботи.

Завдання 5.2.

Розробити схему включення стандартних елементів мікросхем тригерів ТТЛ і ТТЛШ логіки в якості тригера. На навчальному стенді реалізувати схему альтернативного включення тригера і провести її дослідження. Навести таблицю переходів (істинності) спроектованого тригера та часові діаграми його роботи.