- •Методичні вказівки до лабораторних робіт і самостійної роботи з курсу Комп'ютерна схемотехніка

- •Загальні положення

- •Лабораторна робота №1

- •Теоретичні відомості.

- •Відомості про навчальний стенд

- •Порядок виконання завдання 1

- •Лабораторна робота №2

- •Теоретичні відомості.

- •Повний дешифратор

- •Аналітичний підхід у проектуванні повних дешифраторів.

- •Неповні дешифратори

- •Порядок виконання завдання 2.1

- •Порядок виконання завдання 2.2

- •Контрольні запитання

- •Лабораторна робота №3

- •Теоретичні відомості.

- •Контрольні запитання

- •Лабораторна робота №4

- •Теоретичні відомості.

- •Порядок виконання завдання 1

- •Контрольні запитання

- •Лабораторна робота №5

- •Теоретичні відомості.

- •Лабораторна робота №6

- •Теоретичні відомості.

- •Порядок виконання завдання 6.1.1.

- •Порядок виконання завдання 6.1.2.

- •Порядок виконання завдання 6.2.1

- •Порядок виконання завдання 6.2.2.

- •Контрольні запитання

- •Лабораторна робота № 7 Проектування та дослідження лічильників

- •Теоретичні відомості.

- •Порядок виконання завдання 7.1.

- •Порядок виконання завдання 7. 2.

- •Контрольні запитання

- •Лабораторна робота №8

- •Теоретичні відомості.

- •2) Спосіб попереднього запису коду.

- •3) Спосіб збільшення модуля на одиницю (від до).

- •4) Спосіб побудови двійково-кодованого лічильника як цифрового автомату.

- •Порядок виконання завдань 8.1-8.3.

- •Контрольні питання

- •Лабораторна робота №9

- •Теоретичні відомості.

- •Рекомендована література

Теоретичні відомості.

(література: 1, c. 132-140;2, с. 141-143;3, с. 181;4, с. 602-603; 5, с. 157-169)

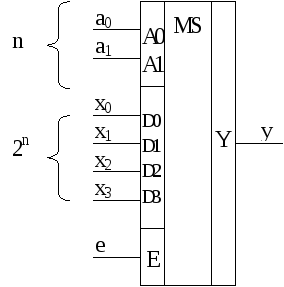

Мультиплексор – логічний елемент комбінаційного типу, що містить n входів вибірки (адресні входи), 2n інформаційних входів і один інформаційний вихід. Мультиплексор призначений для передачі на інформаційний вихід даних з одного із інформаційних входів, номер якого задається поданим на входи вибірки значенням. Додатково мультиплексор може оснащуватися керуючими входами дозволу, за допомогою яких вихід мультиплексора переводиться в неактивний стан.

Традиційно двійкове значення коду, що подається на входи вибірки мультиплексора, безпосередньо визначає номер каналу, з якого дані будуть подаватися на вихід. Тобто, якщо на входи вибірки мультиплексора подасться в двійковому коді значення “і”, дані на вихід будуть подаватися з інформаційного входу DIі (наприклад, якщо на входи вибірки S1-S0 подано двійковий код 10, що відповідає десятковому значенню 2, то дані на вихід мультиплексора дані будуть подаватися з інформаційного входу DI2).

Демультиплексор виконує функцію, зворотну мультиплексору.

Демультиплексор – логічний елемент комбінаційного типу, що містить n входів вибірки (адресних входів), один інформаційний вхід і 2n інформаційних виходів. Демультиплексор призначений для передачі даних з інформаційного входу на один з інформаційних виходів, номер якого задається поданим на входи вибірки значенням. Як і мультиплексор, демультиплексор може оснащуватися керуючими входами дозволу, за допомогою яких виходи демультиплексора переводяться в неактивний стан.

Умовне графічне зображення мультиплексора наведене на рисунку 3.1, таблиця істинності представлена в таблиці 3.1.

Рисунок 3.1 - Умовне графічне зображення чотирьохканального однорозрядного мультиплексора

Таблиця 2.1.

|

e |

a1 |

a0 |

y |

|

0 |

* |

* |

0 |

|

1 1 1 1 |

0 0 1 1 |

0 1 0 1 |

x0 x1 x2 x3 |

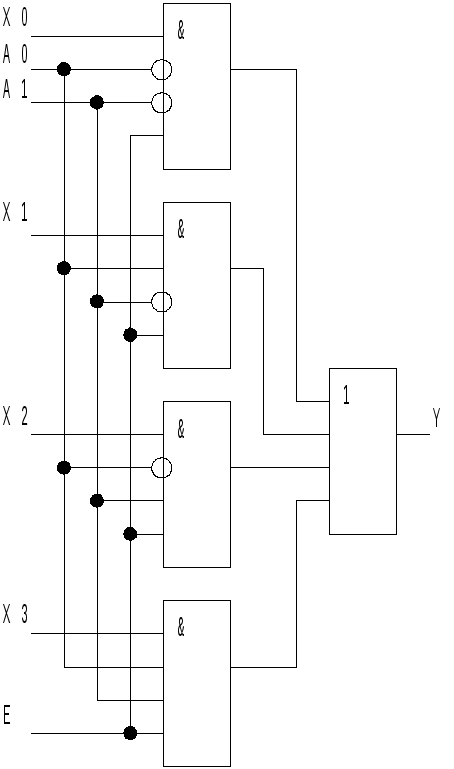

Побудова мультиплексора на основі логічних елементів І та АБО зображена на рисунку 3.2, на основі елементів І-НЕ на рисунку 3.3.

Нарощування розрядності мультиплексорів (демультиплексорів) до N розрядів за наявності n-розрядних секцій виконується шляхом спільного використання N/n секцій з об’єднанням однойменних керуючих входів цих секцій.

Рисунок 3.2. Рис. 3.3.

Нарощування кількості каналів мультиплексорів (демультиплексорів) виконується побудовою з них пірамідальної структури – дерева мультиплексорів (демультиплексорів).

В дереві мультиплексорів (демультиплексорів) виходи елементів попереднього шару з’єднуються із входами елементів наступного шару. Однойменні входи вибірки секцій одного шару з’єднуються між собою.

Кількість шарів, з яких буде складатися дерево, можна визначити із знання наявної кількості входів вибірки у використовуваних елементів та кількості входів вибірки, необхідної для управління роботою проектованого елемента. При побудові мультиплексора (демультиплексора) з кількістю входів вибірки M на секціях мультиплексорів (демультиплексорів) з m входами вибірки, кількість шарів К, з яких буде складатися дерево мультиплексорів (демультиплексорів) визначається за формулою:

К=M/m. (3.1)

Кількість елементів першого шару обирається таким чином, щоб сумарна кількість їх інформаційних входів була не меншою за необхідну кількість інформаційних входів (каналів) проектованого мультиплексора (демультиплексора). В кожному наступному шарі кількість елементів обирається таким чином, щоб їх інформаційних входів було достатньо для підключення до них інформаційних виходів всіх задіяних елементів попереднього шару.

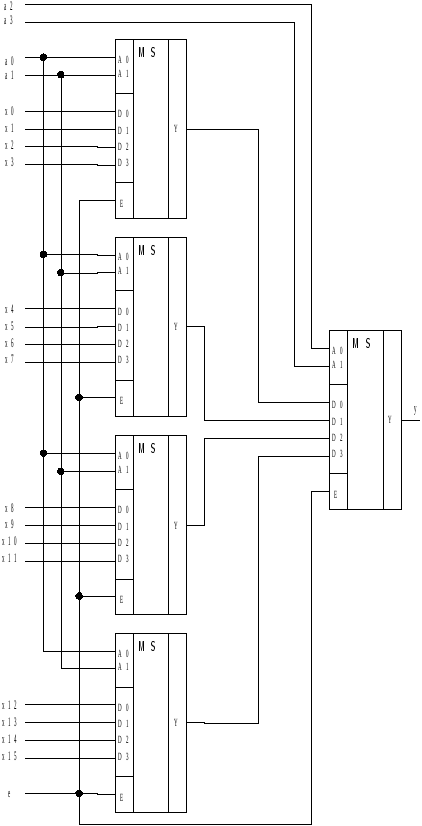

Схему нарощування кількості каналів мультиплексора розглянемо на прикладі побудови однорозрядного мультиплексора з 4 входами вибірки на базі секцій однорозрядних мультиплексорів з 2 входами вибірки.

За формулою 3.1 визначаємо кількість шарів мультиплексорів з 2 входами вибірки, з яких буде складатися дерево мультиплексорів:

К=4/2=2.

Визначимо тепер кількість каналів (кількість інформаційних входів) для проектованого пристрою та наявних секцій мультиплексорів. Виходячи з визначення кількість каналів N мультиплексора, що містить n входів вибірки, визначається як N= 2n .

Отримуємо для проектованого пристрою:

Nпр= 24=16.

Для наявних секцій мультиплексорів:

Nс= 22=4.

Для того, щоб у проектованого пристрою було 16 входів, нам необхідно в першому шарі дерева використати 16/4=4 елемента з чотирма входами.

Для об’єднання чотирьох наявних виходів елементів першого шару нам достатньо використати ще одну наявну секцію однорозрядного чотирьохканального мультиплексора (рисунок 3.4)

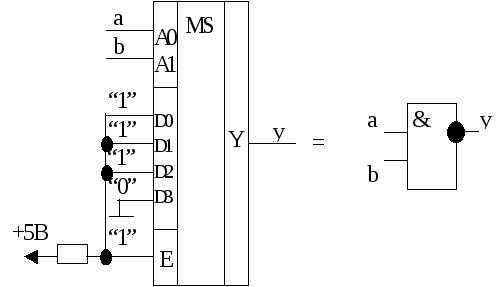

Мультиплексор можна використовувати в якості універсального логічного елемента, тобто з його допомогою можна реалізувати будь-яку функцію з кількістю аргументів, що дорівнює кількості входів вибірки. Для цього вхідні змінні подаються на адресні входи, а на інформаційні входи подаються логічні “1” або ”0” у відповідності із таблицею значень функції, що реалізується на мультиплексорі. Приклад реалізації елемента 2І-НЕ (таблиця істинності представлена в таблиці 3.2) з допомогою двохадресного мультиплексора зображена на рисунку 3.5.

Рисунок 3.4 – Реалізація шістнадцятиканального однорозрядного мультиплексора на чотирьоканальних однорозрядних секціях

Таблиця 3.2

|

a |

b |

y |

|

0 0 1 1 |

0 1 0 1 |

1 1 1 0 |

Рисунок 3.5 – Схема включення мультиплексора в якості логічного елемента 2І-НЕ

Завдання 3.1.

На базі стандартних елементів мікросхем ТТЛ і ТТЛШ логіки розробити однорозрядний мультиплексор (М) або демультиплексор (Д) на N каналів. Вимоги до проектованого пристрою наведено в таблиці 3.3.

Таблиця 3.3.

|

№ вар. |

Тип пристрою |

Кількість каналів |

Елемент дешифрації |

Елемент комутації |

Вхід дозволу |

Інверсія сигналу |

|

|

М |

2 |

Довільний |

ЛЛ1 |

- |

- |

|

|

Д |

2 |

Довільний |

ЛЛ1 |

- |

+ |

|

|

М |

2 |

ЛИ1 |

ЛИ1 |

+ |

- |

|

|

Д |

2 |

ЛИ1 |

ЛИ1 |

+ |

+ |

|

|

М |

2 |

ЛЕ1 |

ЛЕ1 |

+ |

- |

|

|

Д |

2 |

ЛЕ1 |

ЛЕ1 |

+ |

+ |

|

|

М |

2 |

ЛЛ1 |

ЛЛ1 |

+ |

- |

|

|

Д |

2 |

ЛЛ1 |

ЛЛ1 |

+ |

+ |

|

|

М |

2 |

ЛА3 |

ЛА3 |

+ |

- |

|

|

Д |

2 |

ЛА3 |

ЛА3 |

+ |

+ |

|

|

М |

2 |

Довільний |

ЛА3 |

- |

- |

|

|

Д |

2 |

Довільний |

ЛА3 |

- |

+ |

|

|

М |

2 |

ЛИ1 |

ЛЕ1 |

+ |

- |

|

|

Д |

2 |

ЛИ1 |

ЛЕ1 |

+ |

+ |

|

|

М |

2 |

ЛЕ1 |

ЛЛ1 |

+ |

- |

|

|

Д |

2 |

ЛЕ1 |

ЛЛ1 |

+ |

+ |

|

|

М |

2 |

ЛЛ1 |

ЛА3 |

+ |

- |

|

|

Д |

2 |

ЛЛ1 |

ЛА3 |

+ |

+ |

|

|

М |

2 |

ЛА3 |

ЛИ1 |

+ |

- |

|

|

Д |

2 |

ЛА3 |

ЛИ1 |

+ |

+ |

|

|

М |

2 |

Довільний |

ЛИ1 |

- |

- |

|

|

Д |

2 |

Довільний |

ЛИ1 |

- |

+ |

|

|

М |

2 |

ЛИ1 |

ЛЛ1 |

+ |

- |

|

|

Д |

2 |

ЛИ1 |

ЛЛ1 |

+ |

+ |

|

|

М |

2 |

ЛЕ1 |

ЛА3 |

+ |

- |

|

|

Д |

2 |

ЛЕ1 |

ЛА3 |

+ |

+ |

|

|

М |

2 |

ЛЛ1 |

ЛИ1 |

+ |

- |

|

|

Д |

2 |

ЛЛ1 |

ЛИ1 |

+ |

+ |

|

|

М |

2 |

ЛА3 |

ЛЕ1 |

+ |

- |

|

|

Д |

2 |

ЛА3 |

ЛЕ1 |

+ |

+ |

|

|

М |

2 |

Довільний |

ЛЕ1 |

- |

- |

|

|

Д |

2 |

Довільний |

ЛЕ1 |

- |

+ |

|

|

М |

2 |

ЛИ1 |

ЛА3 |

+ |

- |

|

|

Д |

2 |

ЛИ1 |

ЛА3 |

+ |

+ |

|

|

М |

2 |

ЛЕ1 |

ЛИ1 |

+ |

- |

|

|

Д |

2 |

ЛЕ1 |

ЛИ1 |

+ |

+ |

|

|

М |

2 |

ЛЛ1 |

ЛЕ1 |

+ |

- |

|

|

Д |

2 |

ЛЛ1 |

ЛЕ1 |

+ |

+ |

|

|

М |

2 |

ЛА3 |

ЛЛ1 |

+ |

- |

|

|

Д |

2 |

ЛА3 |

ЛЛ1 |

+ |

+ |

|

|

Д |

2 |

Довільний |

ЛЛ1 |

- |

- |

|

|

М |

2 |

Довільний |

ЛЛ1 |

- |

+ |

|

|

Д |

2 |

ЛИ1 |

ЛИ1 |

+ |

- |

|

|

М |

2 |

ЛИ1 |

ЛИ1 |

+ |

+ |

|

|

Д |

2 |

ЛЕ1 |

ЛЕ1 |

+ |

- |

|

|

М |

2 |

ЛЕ1 |

ЛЕ1 |

+ |

+ |

|

|

Д |

2 |

ЛЛ1 |

ЛЛ1 |

+ |

- |

|

|

М |

2 |

ЛЛ1 |

ЛЛ1 |

+ |

+ |

|

|

Д |

2 |

ЛА3 |

ЛА3 |

+ |

- |

|

|

М |

2 |

ЛА3 |

ЛА3 |

+ |

+ |

|

|

Д |

2 |

Довільний |

ЛА3 |

- |

- |

|

|

М |

2 |

Довільний |

ЛА3 |

- |

+ |

|

|

Д |

2 |

ЛИ1 |

ЛЕ1 |

+ |

- |

|

|

М |

2 |

ЛИ1 |

ЛЕ1 |

+ |

+ |

|

|

Д |

2 |

ЛЕ1 |

ЛЛ1 |

+ |

- |

|

|

М |

2 |

ЛЕ1 |

ЛЛ1 |

+ |

+ |

|

|

Д |

2 |

ЛЛ1 |

ЛА3 |

+ |

- |

|

|

М |

2 |

ЛЛ1 |

ЛА3 |

+ |

+ |

|

|

Д |

2 |

ЛА3 |

ЛИ1 |

+ |

- |

|

|

М |

2 |

ЛА3 |

ЛИ1 |

+ |

+ |

|

|

Д |

2 |

Довільний |

ЛИ1 |

- |

- |

|

|

М |

2 |

Довільний |

ЛИ1 |

- |

+ |

|

|

Д |

2 |

ЛИ1 |

ЛЛ1 |

+ |

- |

|

|

М |

2 |

ЛИ1 |

ЛЛ1 |

+ |

+ |

|

|

Д |

2 |

ЛЕ1 |

ЛА3 |

+ |

- |

|

|

М |

2 |

ЛЕ1 |

ЛА3 |

+ |

+ |

|

|

Д |

2 |

ЛЛ1 |

ЛИ1 |

+ |

- |

|

|

М |

2 |

ЛЛ1 |

ЛИ1 |

+ |

+ |

|

|

Д |

2 |

ЛА3 |

ЛЕ1 |

+ |

- |

|

|

М |

2 |

ЛА3 |

ЛЕ1 |

+ |

+ |

|

|

Д |

2 |

Довільний |

ЛЕ1 |

- |

- |

|

|

М |

2 |

Довільний |

ЛЕ1 |

- |

+ |

|

|

Д |

2 |

ЛИ1 |

ЛА3 |

+ |

- |

|

|

М |

2 |

ЛИ1 |

ЛА3 |

+ |

+ |

|

|

Д |

2 |

ЛЕ1 |

ЛИ1 |

+ |

- |

|

|

М |

2 |

ЛЕ1 |

ЛИ1 |

+ |

+ |

|

|

Д |

2 |

ЛЛ1 |

ЛЕ1 |

+ |

- |

|

|

М |

2 |

ЛЛ1 |

ЛЕ1 |

+ |

+ |

|

|

Д |

2 |

ЛА3 |

ЛЛ1 |

+ |

- |

|

|

М |

2 |

ЛА3 |

ЛЛ1 |

+ |

+ |

Завдання 3.2.

Використовуючи мікросхему К555КП11 (додаток Д), яка містить чотири двоканальних однорозрядних мультиплексора з одним об’єднаним входом вибірки, розробити схему електричну принципову однорозрядного трьохадресного мультиплексора (однорозрядного мультиплексора на 8 каналів).

Розробити схему включення спроектованого мультиплексора в якості неповного трьохвходового дешифратора (X2 X1 X0) з одним виходом (Y). Для формування таблиці істинності проектованого дешифратора номер свого варіанту з десяткової системи перевести в двійкову і записати у вигляді 76543210. Визначивши значення і, підставити їх в табл. 3.4.

Таблиця 3.4.

|

X2 |

0 |

0 |

0 |

0 |

1 |

1 |

1 |

1 |

|

X1 |

0 |

0 |

1 |

1 |

0 |

0 |

1 |

1 |

|

X0 |

0 |

1 |

0 |

1 |

0 |

1 |

0 |

1 |

|

Y |

0 |

4 |

2 |

6 |

1 |

3 |

5 |

7 |