- •Методичні вказівки до лабораторних робіт і самостійної роботи з курсу Комп'ютерна схемотехніка

- •Загальні положення

- •Лабораторна робота №1

- •Теоретичні відомості.

- •Відомості про навчальний стенд

- •Порядок виконання завдання 1

- •Лабораторна робота №2

- •Теоретичні відомості.

- •Повний дешифратор

- •Аналітичний підхід у проектуванні повних дешифраторів.

- •Неповні дешифратори

- •Порядок виконання завдання 2.1

- •Порядок виконання завдання 2.2

- •Контрольні запитання

- •Лабораторна робота №3

- •Теоретичні відомості.

- •Контрольні запитання

- •Лабораторна робота №4

- •Теоретичні відомості.

- •Порядок виконання завдання 1

- •Контрольні запитання

- •Лабораторна робота №5

- •Теоретичні відомості.

- •Лабораторна робота №6

- •Теоретичні відомості.

- •Порядок виконання завдання 6.1.1.

- •Порядок виконання завдання 6.1.2.

- •Порядок виконання завдання 6.2.1

- •Порядок виконання завдання 6.2.2.

- •Контрольні запитання

- •Лабораторна робота № 7 Проектування та дослідження лічильників

- •Теоретичні відомості.

- •Порядок виконання завдання 7.1.

- •Порядок виконання завдання 7. 2.

- •Контрольні запитання

- •Лабораторна робота №8

- •Теоретичні відомості.

- •2) Спосіб попереднього запису коду.

- •3) Спосіб збільшення модуля на одиницю (від до).

- •4) Спосіб побудови двійково-кодованого лічильника як цифрового автомату.

- •Порядок виконання завдань 8.1-8.3.

- •Контрольні питання

- •Лабораторна робота №9

- •Теоретичні відомості.

- •Рекомендована література

Контрольні запитання

1. Призначення мультиплексора.

2. Таблиця істинності мультиплексора.

3. Побудова мультиплексора в різних логічних базисах.

4. Використання мультиплексора в якості універсального логічного елемента.

5. Схема збільшення розрядності мультиплексора.

Лабораторна робота №4

Проектування та дослідження суматорів

Мета: вивчення методів проектування суматорів, отримання навиків в розробці однорозрядних та багаторозрядних суматорів.

Теоретичні відомості.

(література: 1, c. 163-178;2, с. 118-125; 4, с. 603-604)

Однорозрядні суматори

Суматор – операційний вузол, що виконує арифметичне додавання операндів.

Найпростішими суматорами є одно розрядні, які діляться на два види: напівсуматори (неповні суматори) та повні суматори.

Напівсуматором називається однорозрядний суматор, що реалізує операцію додавання двох однорозрядних чисел Аі та Ві і на виходах формує два однорозрядних значення: значення суми Sі та значення переносу в старший розряд P.

Таблиця істинності напівсуматора приведена в таблиці 4.1, а графічне зображення - на рисунку 4.1.а.

Повним суматором називається однорозрядний суматор, що реалізує операцію додавання трьох однорозрядних чисел: чисел Аі та Ві, а також значення переносу з молодшого розряду Pi-1. Як і напівсуматор, повний суматор на виходах формує два однорозрядних значення: значення суми Sі та значення переносу в старший розряд Pі.

Таблиця істинності повного суматора приведена в таблиці 4.2, а графічне зображення - на рисунку 4.1.б.

|

Таблиця 4.1. |

|

Таблиця 4.2. | |||||||

|

Аі |

Ві |

Si |

Pi |

Аі |

Ві |

Pi-1 |

Si |

Pi | |

|

0 0 1 1 |

0 1 0 1 |

0 1 1 0 |

0 0 0 1 |

0 0 0 0 1 1 1 1 |

0 0 1 1 0 0 1 1 |

0 1 0 1 0 1 0 1 |

0 1 1 0 1 0 0 1 |

0 0 0 1 0 1 1 1 | |

|

| |||||||||

а б

Рисунок 4.1 – Умовні графічні зображення одно розрядних суматорів: а – напівсуматор; б – повний суматор.

За наведеними в таблицях істинності даними можна вивести функції вихідних сигналів обох видів однорозрядних суматорів.

Для напівсуматора для виходів Si та Pi отримуємо функції:

Si = AiBi,

Pi = AiBi.

Для повного суматора функції вихідних сигналів залежать від трьох вхідних сигналів:

![]() (4.1)

(4.1)

Pi = AiBi+AiPi-1+BiPi-1. (4.2)

Використовуючи функцію додавання по модулю 2 з функцій 4.1 і 4.2 можна отримати наступні функції:

Si = AiBiPi-1; (4.3)

Pi = AiBi+( AiBi)Pi-1. (4.4)

Виконавши елементарні перетворення за законами алгебри логіки можна отримати велику кількість функцій Si та Pi для реалізації суматорів в різних базисах:

![]() (4.5)

(4.5)

![]() (4.6)

(4.6)

![]() (4.7)

(4.7)

![]() (4.8)

(4.8)

![]() (4.9)

(4.9)

![]() (4.10)

(4.10)

![]() (4.11)

(4.11)

![]() (4.12)

(4.12)

![]() (4.13)

(4.13)

![]() (4.14)

(4.14)

![]() (4.15)

(4.15)

![]() (4.16)

(4.16)

![]() (4.17)

(4.17)

![]() (4.18)

(4.18)

![]() (4.19)

(4.19)

![]() ; (4.20)

; (4.20)

![]() ; (4.21)

; (4.21)

![]() ; (4.22)

; (4.22)

Pi = (AiPi-1)Bi+AiPi-1; (4.23)

Pi = Ai(BiPi-1)+BiPi-1; (4.24)

Pi = AiBi+(Ai+Bi)Pi-1; (4.25)

Pi = (Ai+Pi-1)Bi+AiPi-1; (4.26)

Pi = Ai(Bi+Pi-1)+BiPi-1; (4.27)

![]() ; (4.28)

; (4.28)

![]() ; (4.29)

; (4.29)

![]() . (4.30)

. (4.30)

Багаторозрядні суматори

За способом обробки багаторозрядних операндів суматори діляться на паралельні, послідовні та паралельно-послідовні.

В послідовному суматорі додавання починається з молодших розрядів. Додавання двох n-розрядних чисел виконується порозрядно за n циклів із затримкою між циклами, необхідною для гарантованого спрацьовування схеми. Така схема є найпростішою з апаратної точки зору, але забезпечує мінімальну швидкодію і тому не набула розповсюдження. Паралельно-послідовні суматори є комбінованим варіантом, що поєднує в собі принципи будови послідовних і паралельних суматорів, і займає проміжне місце між зазначеними схемами за показниками апаратної складності і швидкодії (див. матеріал лекцій).

Серед багаторозрядних суматорів паралельні суматори є найбільш швидкодіючими, але, одночасно, потребують і найбільших апаратних витрат. В паралельному суматорі всі n розрядів операндів одночасно вступають в операцію додавання, що забезпечується використанням n однорозрядних суматорів.

Найпростішою

є схема побудови паралельного суматора,

в якій секції з’єднуються за ланками

переносів послідовно (рисунок 4.2), тобто,

вихід переносу попередньої секції

(молодшої) з’єднується з входом переносу

наступної секції (старшої). Така схема

організації переносів між секціями

б агаторозрядних

паралельних суматорів отримала назву

послідовної.

агаторозрядних

паралельних суматорів отримала назву

послідовної.

Рисунок 4.2 - Паралельний суматор з послідовним переносом

Така схема може виконати операцію додавання за 1 такт, який дорівнює:

T = ntз.SM ; (4.31)

де n – розрядність паралельного суматора; tз.SM – тривалість затримки розповсюдження сигналу переносу на однорозрядній секції суматора.

Такт роботи такого багаторозрядного суматора повинен бути більшим за час проходження сигналу по всьому ланцюгу переносу.

При великій кількості розрядів тривалість операції додавання буде досить великою. Тому збільшення швидкодії паралельного суматора можна досягнути шляхом використання схеми паралельного (прискореного) переносу. Паралельний суматор з прискореним переносом (рисунок 4.3) не використовує розрядів переносу однорозрядних вентилів.

Перенос формується як функція від вхідних значень.

Р исунок

4.3 - Паралельний суматор з схемою

паралельного переносу

исунок

4.3 - Паралельний суматор з схемою

паралельного переносу

Для виведення функцій переносу та сум введемо змінні:

![]() (4.32)

(4.32)

![]() (4.33)

(4.33)

Звідси

![]() , (4.34)

, (4.34)

![]() (4.35)

(4.35)

За формулою 4.35 можна скласти систему рівнянь, для визначення значень переносів для окремих розрядів паралельного суматора:

(4.36)

(4.36)

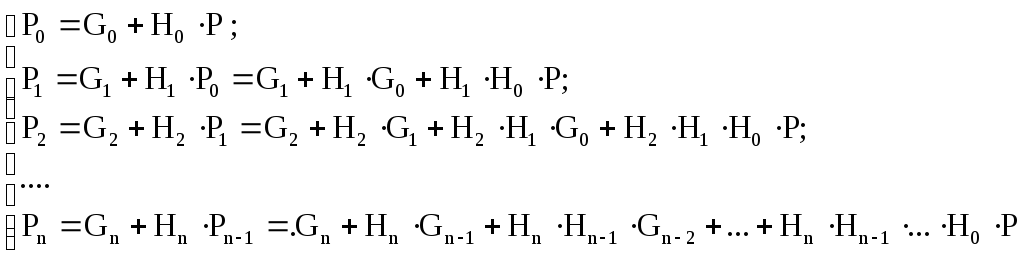

Для зменшення кількості змінних в функціях переносів підставимо до функції Р1 функцію переносу Р0. Отриману функцію Р1, в свою чергу, підставимо до функції Р2 і так далі. Розкривши після підстановки всі дужки, отримаємо систему рівнянь, в якій значення будь якого переносу буде залежати, крім значень Gi і Hi , лише від вхідного переносу Р:

(4.37)

(4.37)

Підставимо

в систему (4.11) значення функцій

![]() і

і![]() (з формул 4.32

і 4.33

відповідно):

(з формул 4.32

і 4.33

відповідно):

(4.38)

(4.38)

Система рівнянь (4.38) описує паралельну схему прискореного переносу. ЇЇ аналіз показує, що тривалість операції формування переносу в старший розряд не залежить від кількості розрядів суматора, а визначається затримкою сигналу в трьох рівнях логічних елементів: рівень елементів додавання за модулем 2, рівень елементів логічного множення і рівень елементів логічного додавання (рисунок 4.4).

Рисунок 4.4 - Схема прискореного формування переносу для сигналу Р0

Складність схеми прискореного переносу швидко зростає із збільшенням розрядності суматора. Тому реальні схеми прискореного переносу будуються для суматорів з розрядністю 2, 4 та 8. Подальше збільшення розрядності швидкісних суматорів досягається шляхом їх секціонування. В середині секції переноси організовуються по паралельній схемі, а міжсекційний перенос – по послідовній або паралельній.

Завдання 4.1.

На базі стандартних елементів мікросхем ТТЛ і ТТЛШ логіки розробити однорозрядний суматор. Вимоги до проектованого пристрою наведено в таблиці 4.1.

Завдання 4.2.

На базі стандартних елементів мікросхем ТТЛ і ТТЛШ логіки розробити багаторозрядний паралельний суматор. Вимоги до проектованого пристрою наведено в таблиці 4.1.

Таблиця 4.1.

|

№ вар. |

Номери формул для побудови однорозрядного суматора |

Розрядність паралельного суматора, спосіб формування переносу | |

|

|

Si |

Pi |

|

|

|

4.1 |

4.4 |

3, послідовний |

|

|

4.5 |

4.23 |

4, паралельний |

|

|

4.6 |

4.24 |

5, послідовний |

|

|

4.7 |

4.25 |

6, паралельний |

|

|

4.9 |

4.27 |

4, послідовний |

|

|

4.10 |

4.28 |

5, паралельний |

|

|

4.11 |

4.29 |

6, послідовний |

|

|

4.12 |

4.30 |

3, паралельний |

|

|

4.13 |

4.2 |

3, послідовний |

|

|

4.14 |

4.4 |

4, паралельний |

|

|

4.17 |

4.25 |

5, послідовний |

|

|

4.18 |

4.26 |

6, паралельний |

|

|

4.19 |

4.27 |

4, послідовний |

|

|

4.20 |

4.28 |

5, паралельний |

|

|

4.21 |

4.29 |

6, послідовний |

|

|

4.22 |

4.30 |

3, паралельний |

|

|

4.3 |

4.2 |

3, послідовний |

|

|

4.5 |

4.4 |

4, паралельний |

|

|

4.6 |

4.23 |

5, послідовний |

|

|

4.7 |

4.24 |

6, паралельний |

|

|

4.9 |

4.26 |

4, послідовний |

|

|

4.10 |

4.27 |

5, паралельний |

|

|

4.11 |

4.28 |

6, послідовний |

|

|

4.12 |

4.29 |

3, паралельний |

|

|

4.13 |

4.30 |

3, послідовний |

|

|

4.14 |

4.2 |

4, паралельний |

|

|

4.17 |

4.24 |

5, послідовний |

|

|

4.18 |

4.25 |

6, паралельний |

|

|

4.19 |

4.26 |

4, послідовний |

|

|

4.20 |

4.27 |

5, паралельний |

|

|

4.21 |

4.28 |

6, послідовний |

|

|

4.22 |

4.29 |

3, паралельний |

|

|

4.3 |

4.30 |

3, послідовний |

|

|

4.5 |

4.2 |

4, паралельний |

|

|

4.6 |

4.4 |

5, послідовний |

|

|

4.7 |

4.23 |

6, паралельний |

|

|

4.9 |

4.25 |

4, послідовний |

|

|

4.10 |

4.26 |

5, паралельний |

|

|

4.11 |

4.27 |

6, послідовний |

|

|

4.12 |

4.28 |

3, паралельний |

|

|

4.13 |

4.29 |

3, послідовний |

|

|

4.14 |

4.30 |

4, паралельний |

|

|

4.17 |

4.23 |

5, послідовний |

|

|

4.18 |

4.24 |

6, паралельний |

|

|

4.19 |

4.25 |

4, послідовний |

|

|

4.20 |

4.26 |

5, паралельний |

|

|

4.21 |

4.27 |

6, послідовний |

|

|

4.22 |

4.28 |

3, паралельний |

|

|

4.3 |

4.29 |

3, послідовний |

|

|

4.5 |

4.30 |

4, паралельний |

|

|

4.6 |

4.2 |

5, послідовний |

|

|

4.7 |

4.4 |

6, паралельний |

|

|

4.9 |

4.24 |

4, послідовний |

|

|

4.10 |

4.25 |

5, паралельний |

|

|

4.11 |

4.26 |

6, послідовний |