- •Методичні вказівки до лабораторних робіт і самостійної роботи з курсу Комп'ютерна схемотехніка

- •Загальні положення

- •Лабораторна робота №1

- •Теоретичні відомості.

- •Відомості про навчальний стенд

- •Порядок виконання завдання 1

- •Лабораторна робота №2

- •Теоретичні відомості.

- •Повний дешифратор

- •Аналітичний підхід у проектуванні повних дешифраторів.

- •Неповні дешифратори

- •Порядок виконання завдання 2.1

- •Порядок виконання завдання 2.2

- •Контрольні запитання

- •Лабораторна робота №3

- •Теоретичні відомості.

- •Контрольні запитання

- •Лабораторна робота №4

- •Теоретичні відомості.

- •Порядок виконання завдання 1

- •Контрольні запитання

- •Лабораторна робота №5

- •Теоретичні відомості.

- •Лабораторна робота №6

- •Теоретичні відомості.

- •Порядок виконання завдання 6.1.1.

- •Порядок виконання завдання 6.1.2.

- •Порядок виконання завдання 6.2.1

- •Порядок виконання завдання 6.2.2.

- •Контрольні запитання

- •Лабораторна робота № 7 Проектування та дослідження лічильників

- •Теоретичні відомості.

- •Порядок виконання завдання 7.1.

- •Порядок виконання завдання 7. 2.

- •Контрольні запитання

- •Лабораторна робота №8

- •Теоретичні відомості.

- •2) Спосіб попереднього запису коду.

- •3) Спосіб збільшення модуля на одиницю (від до).

- •4) Спосіб побудови двійково-кодованого лічильника як цифрового автомату.

- •Порядок виконання завдань 8.1-8.3.

- •Контрольні питання

- •Лабораторна робота №9

- •Теоретичні відомості.

- •Рекомендована література

Лабораторна робота № 7 Проектування та дослідження лічильників

Мета: вивчити методи проектування лічильників, їх призначення та типи, отримати навички в нарощуванні розрядності лічильників.

Теоретичні відомості.

(література: 1, c. 111-120; 2, с. 144-158; 3, с. 186-187; 4, с. 606-608)

Лічильники – складні вузли цифрової автоматики призначені для здійснення мікрооперацій інкременту або декременту, тобто збільшення значення лічильника на 1 або зменшення на 1. крім цього лічильники використовують як дільники частоти; для паралельного запису; попереднього очищення.

Класифікація:

За кількістю станів одного розряду поділяються на двійкові та двійково-десяткові;

За способом перенесення:

з послідовним переносом;

з наскрізним переносом;

з паралельним переносом;

За напрямком лічби:

додаючі;

віднімаючі;

реверсивні;

За способом встановлення початкового стану:

з попередньою установкою;

без попередньої установки.

Основними параметрами лічильника є розрядність та лічильний модуль М. При поданні на вхід лічильника серії імпульсів, лічильник набуває різних станів, але М-ий імпульс переводить лічильник в початковий (або нульовий) стан.

Якщо

![]() ,

деn

– кількість виходів лічильника, то

лічильник двійковий; якщо

,

деn

– кількість виходів лічильника, то

лічильник двійковий; якщо

![]() ,

то лічильник двійково-кодований.

,

то лічильник двійково-кодований.

На

рисунках 7.1, 7.3 і 7.5 відповідно зображені

схеми додаючого, віднімаючого і

реверсивного лічильників з лічильним

модулем

![]() .

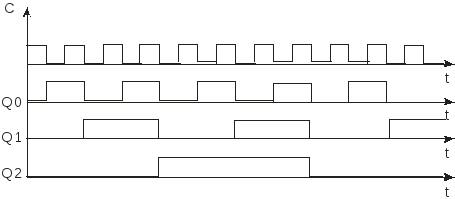

На рисунках 7.2 і 7.4 наведені часові

діаграми додаю чого і віднімаючого

лічильників.

.

На рисунках 7.2 і 7.4 наведені часові

діаграми додаю чого і віднімаючого

лічильників.

Рисунок 7.1 - Схеми додаючого лічильника з послідовною організацією переносів.

Рисунок 7.2 - Часова діаграма роботи додаючого лічильника

Рисунок 7.3 - Схеми віднімаючого лічильника з послідовною організацією переносів.

Рисунок 7.2 - Часова діаграма роботи віднімаючого лічильника

Рисунок 7.5 - Схема реверсивного лічильника з послідовною організацією переносів.

Поряд з простотою побудови послідовні лічильники мають два основних недоліки:

1)

Під час переходу з одного стану в інший

виникає ряд хибних станів, що призводить

до збоїв в роботі. Наприклад, якщо при

додаванні відбувається перехід від

![]() до

до![]() ,

тобто

,

тобто![]() ,

то зміна відбувається протягом певного

часу: а саме

,

то зміна відбувається протягом певного

часу: а саме![]() .

.

2) Максимальна затримка розповсюдження дорівнює сумі затримок всіх розрядів.

В

паралельних лічильниках всі розряди

встановлюються практично одночасно.

На рисунку 7.6 зображена схема додаючого

лічильника з паралельною організацією

переносів з лічильним модулем

![]() .

.

Рисунок 7.6 - Схеми додаючого лічильника з паралельною організацією переносів

Кон’юнктори служать для забезпечення інверсії даного розряду при умові, що всі попередні розряди знаходяться в одиничному стані. На входи Т-тригерів подаються сигнали:

X0=Xвх (тактовий вхід лічильника);

В паралельному лічильнику затримка розповсюдження визначається тільки затримкою кон’юнктора та самого розряду. Недоліком є складність побудови, яка виникає при збільшені розрядності. Адже зростає кількість входів кон’юнктора.

Схема додаючого лічильника із наскрізним переносом зображена на рисунку 7.7.

Рисунок 7.1 - Схема додаючого лічильника з наскрізною організацією переносів.

На входи Т-тригерів подаються сигнали:

Х0=Хвх;

Х1=Х0![]() Q0;

Q0;

X2=X1![]() Q1;

Q1;

…;

Xn=Xn-1![]() Qn-1.

Qn-1.

Час затримки визначається часом проходження імпульсів через коло кон’юнкторів. Цей час більший , ніж в паралельному лічильнику, але менше ніж в послідовному.

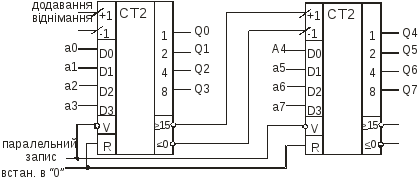

Існує

велика кількість стандартних мікросхем

лічильників. Проте часто виникає потреба

в збільшенні розрядності лічильників.

Розширення розрядності розглянемо на

прикладі : використовуючи мікросхему

4-розрядного паралельного реверсивного

лічильника з можливістю паралельного

запису побудувати 8-розрядний лічильник.

Реалізація даного прикладу зображена

на рисунку 7.8. Лічильний модуль

![]() =256.

=256.

Рисунок 7.8. Схема 8-розрядного реверсивного лічильника на базі 4-розрядних лічильників.

Завдання 7.1.

На базі тригерів ТТЛ і ТТЛШ логіки розробити лічильник на п’ять розрядів. Вимоги до проектованого пристрою наведено в таблиці 6.1.

Примітка: поле “Зміна стану за такт” визначає тип лічильника: “+1” – додаючий; “-1” – віднімаючий.