- •1.2.Информационные процессы, их базовые составляющие.

- •1.3. Язык как средство обмена информацией.

- •1.6.Информационный ресурс

- •1.7Информационные системы

- •1.8.Основные признаки информационного общества

- •2.1.Понятие информации.

- •2.2. 2.3. Свойства(качество) инф :

- •2.4. Классификация инф:

- •2.6. Энтропия

- •2.8.Единицы измерения информации.

- •3.1.Язык как знаковая система.

- •3.2.Кодирование информации

- •3.3Двоичное кодирование инфор-ции в компью

- •3.4Преимущество цифрового представления инф-ции

- •3.5Кодирование текстовой информации

- •3.6.Кодовые таблицы.

- •3.7.Технология создания текстового файла.

- •3.8.Аналоговый и дискретный способы представления информ

- •3.9.Двоичное кодирование графической и звуковой информации

- •3.9.Кодирование графической информации, основные характеристики.

- •3.10. Глубина цвета и система цветов rgb

- •4.1 Представление целых неотрицательных чисел в формате с фиксированной точкой, диапазон чисел такого представления.

- •4.2.Прямой,обратный и дополнительный коды.

- •4.3 Арифметические действия в формате с фиксированной точкой (запятой).

- •4.4.Представление чисел в формате с плавающей запятой.

- •4.5.Экспоненциальная форма записи чисел.

- •4.6.Нормализованная мантисса.

- •4.7.Диапозон представляемых чисел.

- •4.8 Арифметические действия в формате с плавающей запятой и правила их выполнения.

- •5.2.Алфавит, число, цифра.

- •5.3.Наиболее известные системы счисления.

- •5.4.Непозиционные системы счисления, примеры.

- •5.5.Существенные недостатки непозиционных систем счисления.

- •5.6.Позиционные сс.

- •5.7.Алфавит, основание системы счисления.

- •5.8.Формы записи чисел в позиционных системах счисления.

- •5.9.Перевод целых, дробных и смешанных чисел из 1 позиционной сс в другую.

- •5.10.Перевод чисел из 1сСв другую через двоичную сс, правила и примеры.

- •5.11.Арифметические операции в позиционных сс.

- •5.12.Построение таблиц арифметических действий в позиционных системах счисления.

- •6.1.Понятие как форма мышления, его содержание и объем.

- •6.2. Высказывание как форма мышления.

- •6.3. Простые и составные высказывания.

- •6.4.Истинность и ложность высказываний.

- •6.5.Умозаключение как форма мышления.

- •6.6.Алгебра высказываний.

- •6.7.Логические переменные и логические операции.

- •6.8.Приоритеты выполнения логических операций.

- •6.9Логические выражения.

- •6.10.Таблица истинности, алгоритм её построения.

- •6.11Равносильные логические выражения.

- •6.12. Логические функции.

- •6.13. Базовые логические операции.

- •6. 14. Логические законы и правила преобразования логических выражений.

- •6.16. Построение логических схем по логическим функциям.

- •6.17.Полусумматор двоичных чисел, его предназначение и логическая схема.

- •6.18.Полный одноразрядный сумматор двоичных чисел, принципы работы.

- •6.20.Триггер, его назначение, принцип работы и логическая схема.

- •7.1 Общие принципы построения эвм.

- •7.3.Типовые схемы построения эвм.

- •7.4.Поколения эвм.

- •7.5.Магистрально-модульный принцип построения компьютера.

- •7.6.Процессор, его основные характеристики и назначения.

- •7.7.Виды памяти компьютера и их назначение.

- •7.8.Оперативная память, её предназначение и основные характеристики.

- •7.9. Внешняя память компьютера.

- •7.10.Носители информации

- •7.11. Устройства ввода информации.

- •7.12.Устройства вывода информации.

- •8.1.Програмное обеспечение компьютера.

- •8.2.Системное программное обеспечение компьютера.

- •8.3.Операционные системы, их классификация.

- •8.4. Компоненты и функции операционной системы.

- •8.5.Этапы загрузки операционной системы.

- •8.6.Графический интерфейс Windows, его компоненты.

- •8.7.Сервисные программы.

- •8.8.Архиваторы, основные алгоритмы и методы архивации.

- •8.9.Компьютерные вирусы и антивирусные программы

- •9.2.Формирование физической и логической структуры дисков.

- •9.4.Одноуровневая и многоуровневая файловые системы.

- •9.5.Представление файловой системы с помощью графического интерфейса.

- •9.6.Файл, имя, тип, путь доступа к файлу, полное имя файла.

- •9.7.Файловые менеджеры.

- •10.1. Прикладное программное обеспечение

- •10.2. Пакеты прикладных программ, их классификация.

- •10.3. Проблемно-ориентированные ппп.

- •10.4.Текстовые редакторы и настольные издательские системы, их назначение и основные возможности.

- •10.5.Компьютерная графика, области её применения.

- •10.6.Графические редакторы растрового типа, особенности работы в них.

- •10.7.Пакеты программ мультимедиа.

- •10.8. Электронные таблицы, назначение и основные возможности.

- •10.9.Интегрированные пакеты прикладных программ, их разновидности.

- •10.10.Объектно-связные интегрированные пакеты прикладных программ.

7.3.Типовые схемы построения эвм.

7.4.Поколения эвм.

Классификация ЭВМ по поколениям (по элементарной базе): - Первое поколение (50г.): ЭВМ на электронных вакуумных лампах. - Второе поколение (60г.): ЭВМ на дискретных полупроводниковых приборах (транзисторах). - Третье поколение (70г.): ЭВМ на полупроводниковых интегральных схемах с малой степенью интеграции. - Четвертое поколение (80г.): ЭВМ на больших интегральных схемах. - Пятое поколение (90): ЭВМ на сверхбольших интегральных схемах. - Шестое и последующие поколения: оптоэлектронные ЭВМ с массовым параллелизмом и нейронной структурой - с распределенной степенью большого числа несложных микропроцессоров, моделирующих архитектуру нейронных биологических систем. Интегральная схема - электронная схема специального назначения, выполненная в виде единого полупроводникового кристалла, объединяющего большое число диодов и транзисторов.

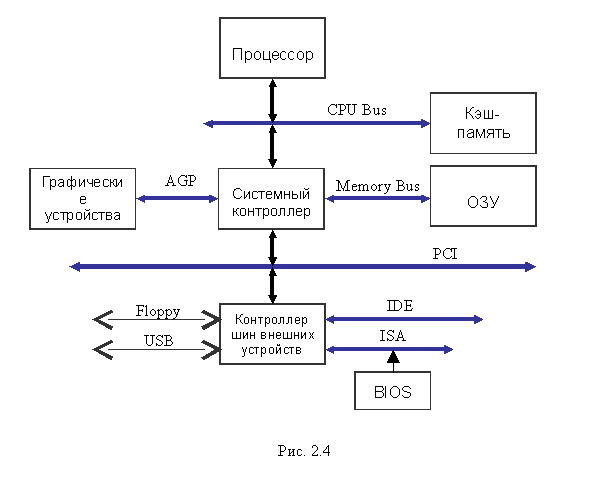

7.5.Магистрально-модульный принцип построения компьютера.

В основу архитектуры современных персональных компьютеров положен магистрально-модульный принцип. Модульный принцип позволяет потребителю самому комплектовать нужную ему конфигурацию компьютера и производить при необходимости ее модернизацию. Модульная организация компьютера опирается на магистральный (шинный) принцип обмена информацией между устройствами.

Магистраль (системная шина) включает в себя три многоразрядные шины: шину данных, шину адреса и шину управления, которые представляют собой многопроводные линии ( рис. 1.1). К магистрали подключаются процессор и оперативная память, а также периферийные устройства ввода, вывода и хранения информации, которые обмениваются информацией на машинном языке (последовательностью нулей и единиц в форме электрических импульсов).

Шина данных. По этой шине данные передаются между различными устройствами. Например, считанные из оперативной памяти данные могут быть переданы процессору для обработки, а затем полученные данные могут быть отправлены обратно в оперативную память для хранения. Таким образом, данные по шине данных могут передаваться от устройства к устройству в любом направлении.

Разрядность шины данных определяется разрядностью процессора, т.е. количеством двоичных разрядов, которые могут обрабатываться или передаваться процессором одновременно. Разрядность процессоров постоянно увеличивается по мере развития компьютерной техники.

Шина адреса. Выбор устройства или ячейки памяти, куда пересылаются или откуда считываются данные по шине данных, производит процессор. Каждое устройство или ячейка оперативной памяти имеет свой адрес. Адрес передается по адресной шине, причем сигналы по ней передаются в одном направлении – от процессора к оперативной памяти и устройствам (однонаправленная шина).

Разрядность шины адреса определяется объемом адресуемой памяти (адресное пространство), т.е. количество однобайтовых ячеек оперативной памяти, которые могут иметь уникальные адреса. Это количество можно рассчитать по формуле:

N = 2I, где I – разрядность шины адреса.

В современных компьютерах разрядность шины адреса составляет 36 бит.

Таким образом, максимально возможное

количество адресуемых ячеек составляет: N = 236 = 68 719 476 736.

Шина управления. По шине управления передаются сигналы, определяющие характер обмена информацией по магистрали. Сигналы управления показывают, какую операцию – считывание или запись информации из памяти – нужно производить, синхронизируют обмен информацией между устройствами и так далее.