- •Конспект лекций

- •190402 – «Автоматика, телемеханика и связь на железнодорожном транспорте»

- •1. Общие сведения

- •1.1. Характеристика дискретных элементов

- •1.2. Контактные и бесконтактные дискретные элементы

- •1.3. Классификация дискретных устройств

- •2. Функции алгебры логики

- •2.1. Определение и задание функций алгебры логики

- •2.2. Функции алгебры логики одной и двух переменных и их реализация

- •2.3. Базис: конъюнкция, дизъюнкция, инверсия

- •2.4. Нормальные формы функций алгебры логики

- •2.5. Минимизация функций алгебры логики. Метод Квайна – Мак-Класки

- •2.6. Геометрический метод минимизация функций алгебры логики

- •2.7. Минимизация функций алгебры логики методом карт Карно

- •3. Анализ и синтез комбинационных устройств

- •3.1. Анализ комбинационных дискретных устройств

- •3.2. Синтез комбинационных дискретных устройств

- •3.3. Примеры синтеза специальных комбинационных схем

- •3.4. Анализ релейных схем на графике

- •4. Структурный синтез дискретных устройств с памятью

- •4.1. Общая структура дискретного устройства с памятью

- •4.2. Виды элементов памяти

- •4.3. Анализ дискретных устройств с памятью

- •4.4. Этапы синтеза дискретного устройства с памятью

- •4.5. Системы счисления. Двоичная система счисления

- •5. Логическое проектирование цифровых схем

- •5.1 Асинхронные и синхронные триггеры

- •5.2. Синтез счетчиков

- •6. Синтез надежных дискретных устройств

- •6.1. Методы повышения надежности дискретных устройств

- •6.2. Резервирование контактных схем

- •6.3. Избыточные устройства с восстанавливающими органами

- •6.4. Надежные комбинационные схемы

- •7. Синтез схем дискретных устройств с исключением опасных отказов

- •7.1. Понятие об опасном отказе

- •7.2. Опасные отказы в комбинационных схемах

- •7.3. Методы построения безопасных комбинационных схем

- •7.4. Логические элементы безопасных систем железнодорожной автоматики и телемеханики

- •7.5. Принципы построения надежных и безопасных дискретных систем

4.2. Виды элементов памяти

В п. 2.3 показано, что для построения любой комбинационной схемы необходимо иметь функционально-полный набор логических элементов (базис), например, {И, ИЛИ, НЕ}. Для построения любой многотактной схемы к функционально-полному набору элементов следует добавить еще элементы памяти: {И, ИЛИ, НЕ, ПАМЯТЬ}.

Элементы памяти (ЭП) можно разделить на два основных вида: ЭП без фиксации воздействия и ЭП с фиксацией воздействия.

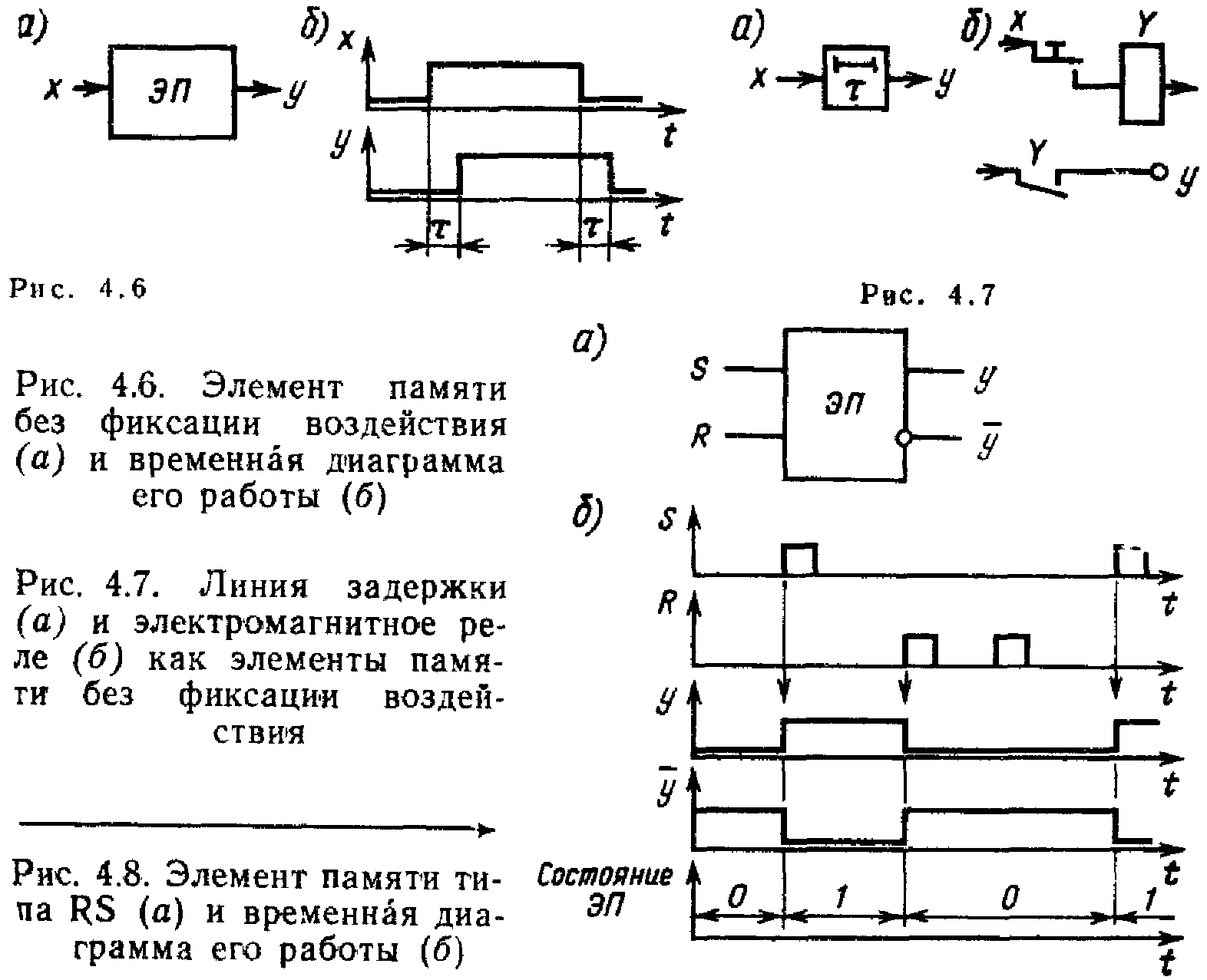

Элементы памяти без фиксации воздействия. Данные ЭП имеют один вход х и один выход у (рис. 4.6). Из диаграммы их работы следует, что изменение сигнала на входе х с некоторой задержкой τ передается на выход у. При этом изменение сигнала запоминается только на время τ. Так работает линия задержки или электромагнитное реле (рис. 4.7). В последнем случае задержка τ определяется инерционностью срабатывания реле при притяжении и отпускании якоря.

Элементы памяти

с фиксацией воздействия.

Из всех видов ЭП с фиксацией воздействия

рассмотрим только один их основной вид

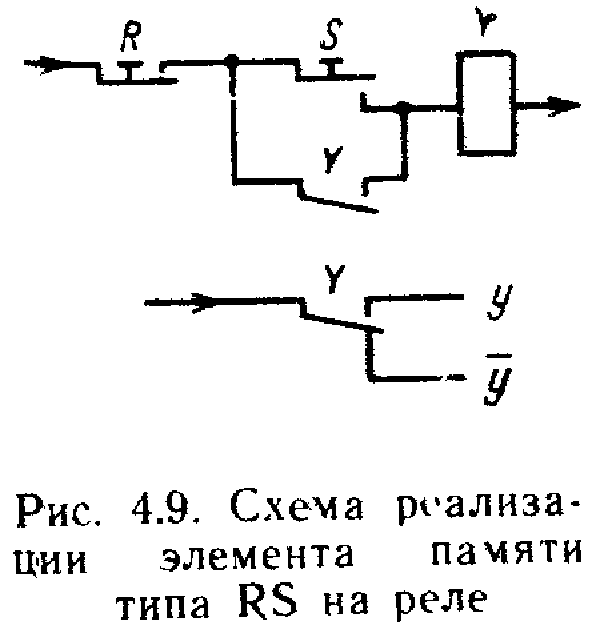

– элемент памяти типа RS (рис. 4.8). Он имеет

два состояния, которые обозначают 0 и

1, два входа S

и R

и два выхода у

и ![]() .

Сигнал логической 1 на входе S

переводит ЭП в состояние 1 (включает

его), на входе R

– в состояние логического 0 (выключает

ЭП). При нахождении ЭП в состоянии 1 на

его выходе у,

называемом прямым, имеется сигнал

логической 1, а на выходе

.

Сигнал логической 1 на входе S

переводит ЭП в состояние 1 (включает

его), на входе R

– в состояние логического 0 (выключает

ЭП). При нахождении ЭП в состоянии 1 на

его выходе у,

называемом прямым, имеется сигнал

логической 1, а на выходе ![]() ,

называемом инверсным, – сигнал логического

0. На инверсном выходе появляется сигнал

логической 1, если ЭП находится в состоянии

0.

,

называемом инверсным, – сигнал логического

0. На инверсном выходе появляется сигнал

логической 1, если ЭП находится в состоянии

0.

Из временной диаграммы работы ЭП RS-типа следует, что в нем происходит фиксация воздействия на входы R и S. Для переключения ЭП в противоположное состояние необходимо воздействие на соответствующий вход.

В ЭП данного типа на реле (рис. 4.9) при нажатии кнопки S срабатывает реле Y и остается под током при отпускании кнопки по цепи, проходящей через собственный фронтовой контакт. Обесточивание реле Y происходит при нажатии кнопки R.

Итак, как уже отмечалось, память в релейно-контактных схемах образуется за счет создания цепи самоблокировки. Непосредственно из рис. 4.9 следует логическая формула памяти

![]() .

.

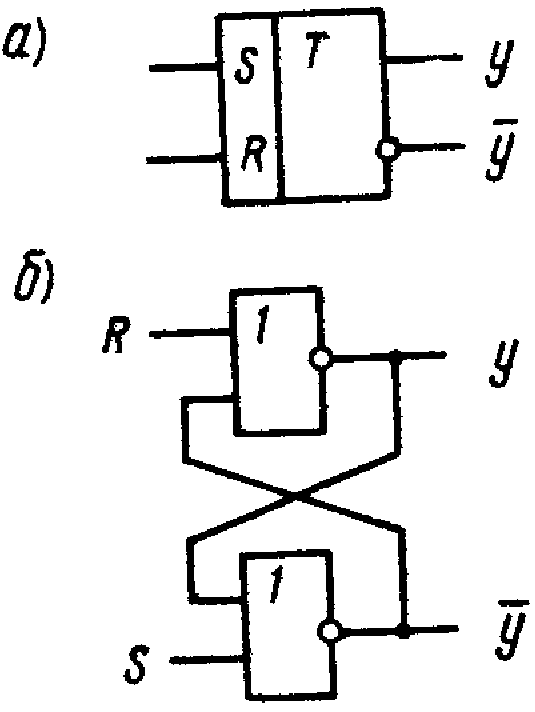

Элемент памяти данного типа на транзисторах называют RS-триггером (рис. 4.10).

Рис. 4.10. Условное обозначение (а) и схема асинхронного RS-триггера (б)

Триггер состоит

из двух элементов, охваченных обратными

связями. Как уже указывалось, память в

функциональных логических схемах

образуется благодаря наличию обратных

связей. Покажем, что функция на выходе

у

описывается той же формулой. Имеем ![]() и

и ![]() .

Подставляя второе равенство в первое,

получаем

.

Подставляя второе равенство в первое,

получаем ![]() .

.

Работа RS-триггера обычно записывается с помощью специальной таблицы — таблицы переходов (табл. 4.3). В ней буквами S n, R n, Y n и Y n+1 обозначены значения логических сигналов S и R и состояние триггера Y в моменты времени t n и t n+1 следующие друг за другом. Из табл. 4.3 видно, что состояние входов S = 1, R = 1 является недопустимым, так как в этом случае состояние RS-триггера не определено (~).

Таблица 4.3

|

t n |

t n+1 | |

|

S n |

R n |

Y n+1 |

|

0 |

0 |

Y n |

|

1 |

0 |

1 |

|

0 |

1 |

0 |

|

1 |

1 |

~ |

Решение задач анализа и синтеза многотактных схем зависит от вида применяемого ЭП. Тем не менее, многие этапы анализа и синтеза являются общими.