- •Конспект лекций

- •190402 – «Автоматика, телемеханика и связь на железнодорожном транспорте»

- •1. Общие сведения

- •1.1. Характеристика дискретных элементов

- •1.2. Контактные и бесконтактные дискретные элементы

- •1.3. Классификация дискретных устройств

- •2. Функции алгебры логики

- •2.1. Определение и задание функций алгебры логики

- •2.2. Функции алгебры логики одной и двух переменных и их реализация

- •2.3. Базис: конъюнкция, дизъюнкция, инверсия

- •2.4. Нормальные формы функций алгебры логики

- •2.5. Минимизация функций алгебры логики. Метод Квайна – Мак-Класки

- •2.6. Геометрический метод минимизация функций алгебры логики

- •2.7. Минимизация функций алгебры логики методом карт Карно

- •3. Анализ и синтез комбинационных устройств

- •3.1. Анализ комбинационных дискретных устройств

- •3.2. Синтез комбинационных дискретных устройств

- •3.3. Примеры синтеза специальных комбинационных схем

- •3.4. Анализ релейных схем на графике

- •4. Структурный синтез дискретных устройств с памятью

- •4.1. Общая структура дискретного устройства с памятью

- •4.2. Виды элементов памяти

- •4.3. Анализ дискретных устройств с памятью

- •4.4. Этапы синтеза дискретного устройства с памятью

- •4.5. Системы счисления. Двоичная система счисления

- •5. Логическое проектирование цифровых схем

- •5.1 Асинхронные и синхронные триггеры

- •5.2. Синтез счетчиков

- •6. Синтез надежных дискретных устройств

- •6.1. Методы повышения надежности дискретных устройств

- •6.2. Резервирование контактных схем

- •6.3. Избыточные устройства с восстанавливающими органами

- •6.4. Надежные комбинационные схемы

- •7. Синтез схем дискретных устройств с исключением опасных отказов

- •7.1. Понятие об опасном отказе

- •7.2. Опасные отказы в комбинационных схемах

- •7.3. Методы построения безопасных комбинационных схем

- •7.4. Логические элементы безопасных систем железнодорожной автоматики и телемеханики

- •7.5. Принципы построения надежных и безопасных дискретных систем

5. Логическое проектирование цифровых схем

5.1 Асинхронные и синхронные триггеры

В современных электронных системах автоматики и вычислительной техники в качестве основного вида элементов памяти применяют триггеры.

Триггер представляет собой устройство с двумя устойчивыми состояниями: 0 и 1. Он удобен для обработки двоичной информации. Двум устойчивым состояниям триггера отвечают различные значения выходного сигнала, каждый из которых соответствует логическим 0 или 1. Записанная в триггере двоичная информация (0 или 1) сохраняется до тех пор, пока состояние триггера не изменится. В случае необходимости входным сигналом триггер переводится из одного устойчивого состояния в другое, тем самым изменяется записанная в нем информация. Триггеры выпускают в интегральном исполнении в виде самостоятельных изделий, из которых собирают другие типовые цифровые устройства, или включают в состав любых дискретных устройств с памятью.

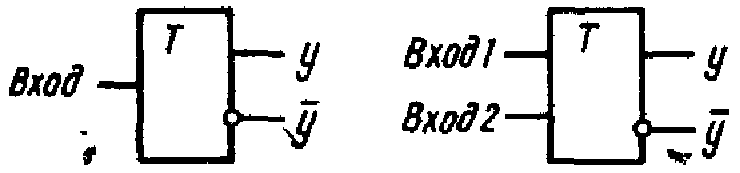

Существует большое число разновидностей триггера. Элементарные триггеры (рис, 5.1) имеют один или два входа и два выхода.

Рис. 5.1. Триггеры

Триггер с одним

входом переключается из одного устойчивого

состояния в другое по этому входу в

различные моменты времени. У триггера

с двумя входами один из них используется

для перевода его в состояние 1, а другой

– в состояние 0. Сигналы на выходах (у и

![]() )

триггера являются взаимно обратными.

На прямом выходе у сигнал логической 1

присутствует тогда, когда триггер

находится в состоянии 1, а на инверсном

выходе – при нахождении его в состоянии

0.

)

триггера являются взаимно обратными.

На прямом выходе у сигнал логической 1

присутствует тогда, когда триггер

находится в состоянии 1, а на инверсном

выходе – при нахождении его в состоянии

0.

Триггеры различаются по логическим условиям работы, которые задаются специальными таблицами переходов. Основными являются D, T, RS, JK, E, R и S-триггеры. D- и Т-триггеры имеют один вход управления, остальные триггеры – два. Таблицы 5.1 и 5.2 являются таблицами переходов указанных триггеров.

В табл. 5.1 входные логические сигналы в момент времени t n обозначены Dn и Тп соответственно для D- и Т-триггеров. Аналогично в табл. 5.2 входные логические сигналы на входах S и R RS, E, R и S-триггеров обозначены Sn и Rn, a JK-триггера – Jn и Кп. Состояния триггера Y в моменты времени t n и t n+1, следующие один за другим, обозначены Yn и Y n+1.

В клетке таблицы переходов указывается состояние, в которое приходит триггер в момент времени t n+1 при поступлении на его входы в момент времени t n сигналов, указанных в строке, где расположена данная клетка. Из табл. 5.2 видно, что по входам S и J соответствующие триггеры переводятся в состояние 1, а по входам R и К – в состояние 0. Работа триггеров с двумя входами отличается только при одном наборе значений входных сигналов, когда S = R =1, причем поведение RS-триггера на этом наборе не определено.

По способу записи входной информации триггеры делят на асинхронные и синхронные (тактируемые). В асинхронном триггере в любой момент времени информация на входах однозначно определяет соответствующее его состояние. При изменении информации на входе после завершения переходных процессов это изменение воспринимается триггером. Синхронные триггеры содержат дополнительный вход для тактовых импульсов, представляющих собой последовательность импульсов с некоторым периодом Т. Входная информация действует на собственно триггер только при поступлении тактовых импульсов.

Следует иметь в виду, что хотя триггер и выступает как бистабильная ячейка памяти, сама логическая схема, соответствующая его внутренней структуре, может иметь большее (чем два) число устойчивых состояний. Одно и то же значение выхода ставится в соответствие нескольким устойчивым состояниям, что имеет место в триггерах со сложной логикой работы. Так как триггеры представляют собой дискретные устройства с памятью, то любой из них может быть синтезирован по рассмотренному в п 4.4 алгоритму 4.2.

Рассмотрим основные триггеры и их свойства.

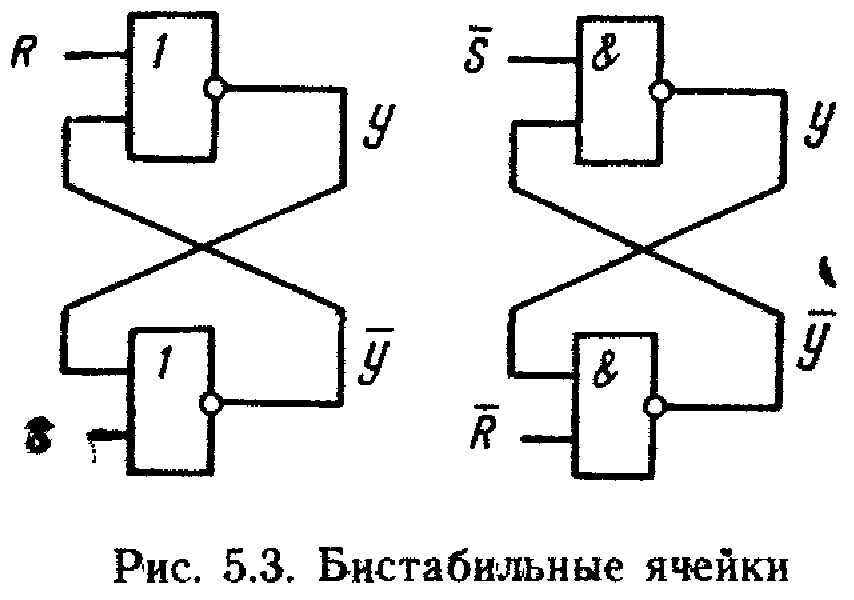

RS-триггеры. Триггеры данного типа являются простейшими триггерными системами. Их широко используют при синтезе дискретных устройств с памятью. Элементарные RS-триггеры, состоящие из двух элементов ИЛИ-НЕ или И-НЕ, называют бистабильными ячейками (рис. 5.2). Они входят в состав других, более сложных триггеров в качестве ячеек памяти.

Рис. 5.2. Бистабильные ячейки

Устройство и работа асинхронного RS-триггера были рассмотрены в п. 4.2 (см. рис. 4.8, 4.10).

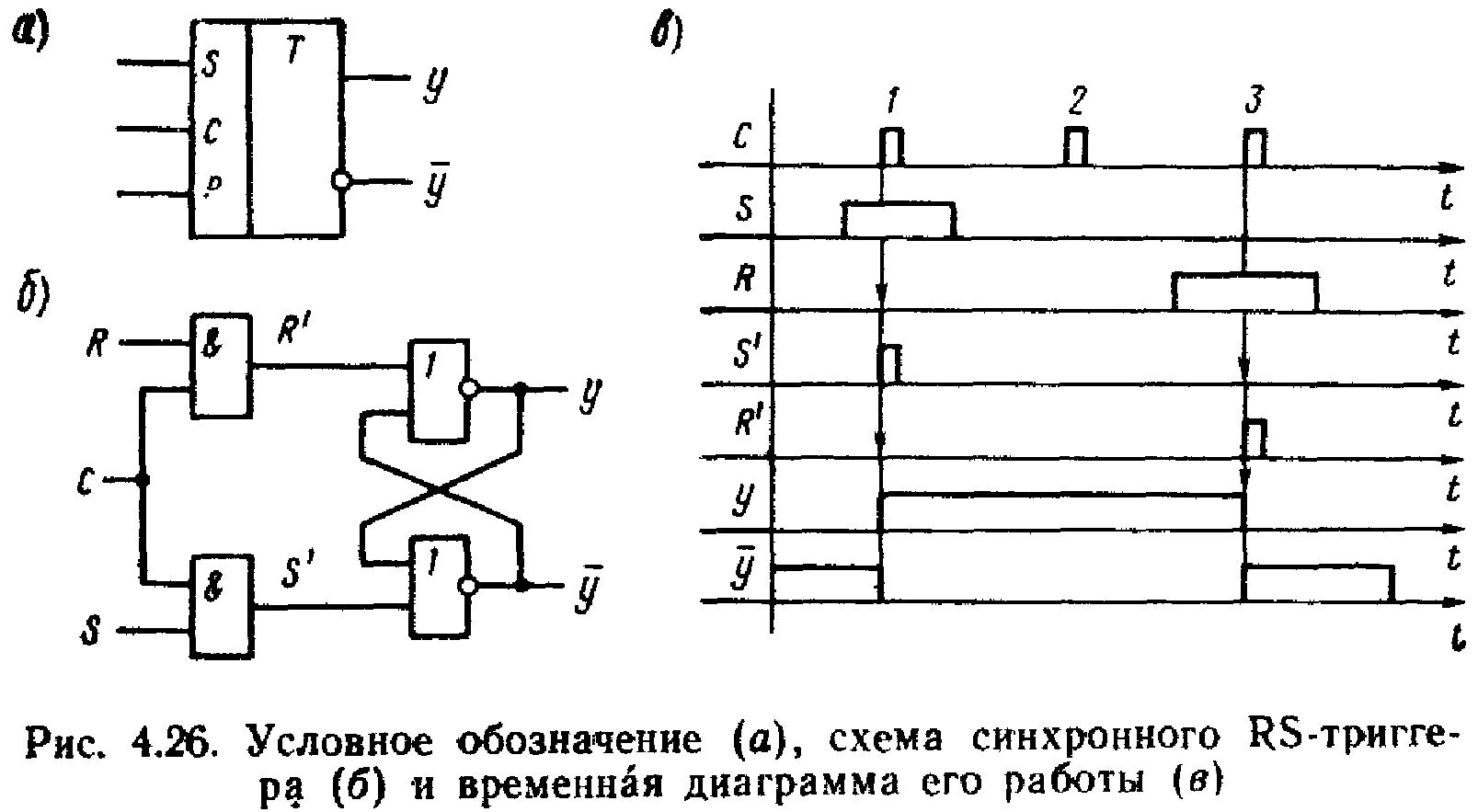

Рассмотрим устройство и работу синхронного RS-триггера.

Для синтеза синхронных дискретных устройств используют синхронные (тактируемые) RS-триггеры, имеющие по сравнению с асинхронными (см. рис. 4.10) еще один вход С, который называют синхронизирующим, или-тактовым (рис. 5.3).

Рис. 5.3. Условное обозначение (а), схема синхронного RS-триггера (б) и временная диаграмма его работы (в)

На вход С

поступают синхроимпульсы. Сигналы на

входы R

и S

могут приходить в любой момент времени,

однако триггер переключается только в

моменты времени, определяемые

синхроимпульсами. Логика работы

синхронного RS-триггера задается

уравнением

![]() .

Рассмотрим временную диаграмму его

функционирования. Пусть в начальный

момент времени триггер находится в

состоянии 0 (значения логических сигналову

= 0,

.

Рассмотрим временную диаграмму его

функционирования. Пусть в начальный

момент времени триггер находится в

состоянии 0 (значения логических сигналову

= 0,

![]() = 1). При поступлении на входS

сигнала логической 1 переключение

триггера не происходит, так как в этот

момент сигналы С

= 0 и S'

=0. Для переключения триггера необходимо,

чтобы S'

= 1, последнее возможно только при S

= 1 и С

= 1.

= 1). При поступлении на входS

сигнала логической 1 переключение

триггера не происходит, так как в этот

момент сигналы С

= 0 и S'

=0. Для переключения триггера необходимо,

чтобы S'

= 1, последнее возможно только при S

= 1 и С

= 1.

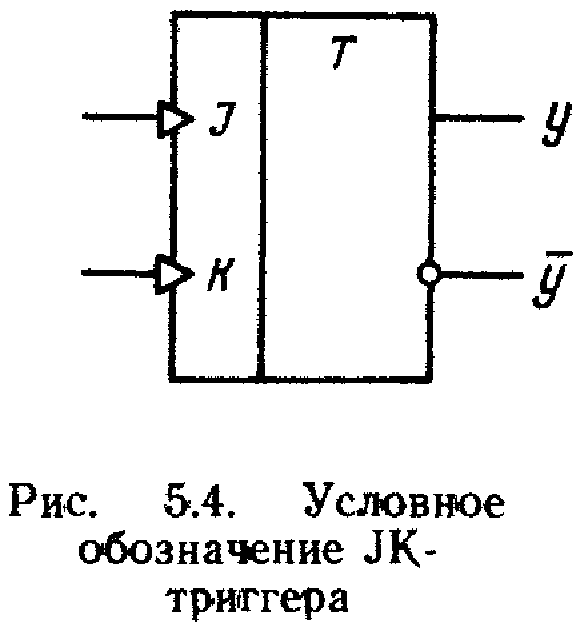

JК-триггеры. У этих триггеров устранена неопределенность, имеющая место в RS-триггерах, когда на обоих его входах одновременно действуют сигналы логической 1. JK-триггер (рис. 5.4) в этом случае переключается в противоположное состояние (см. табл. 5.2).

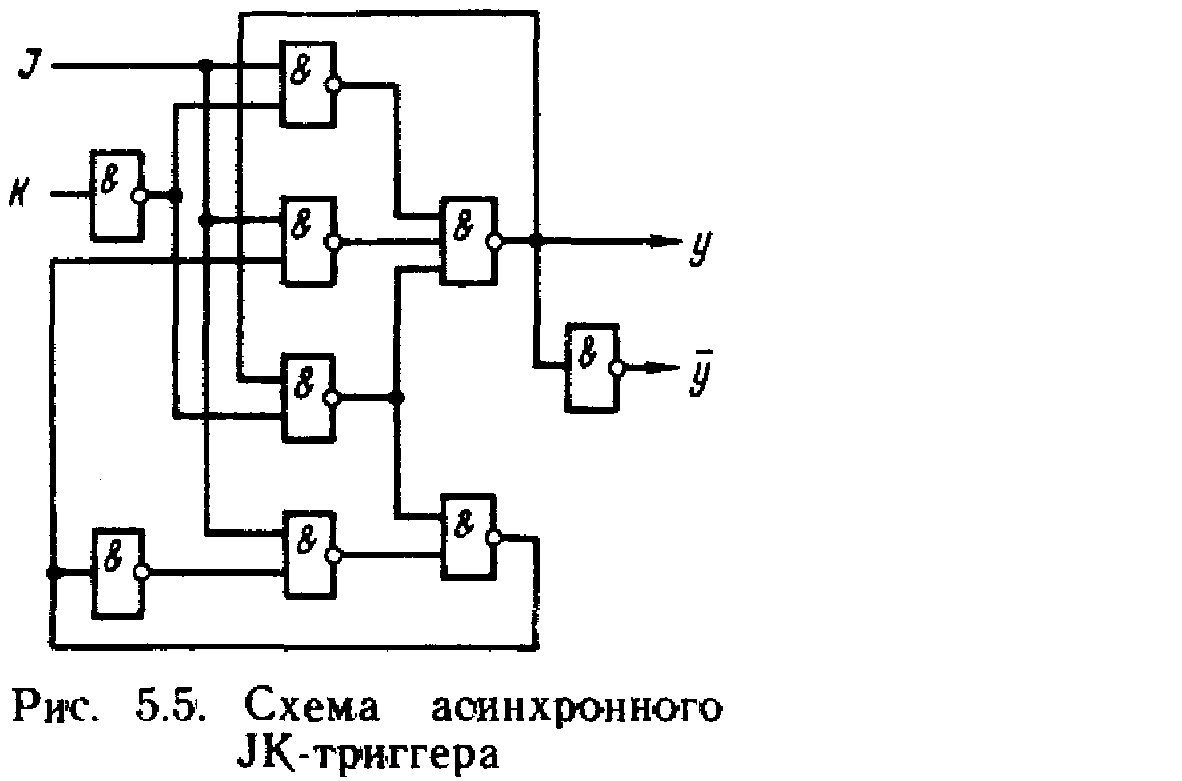

Структура асинхронного JK-триггера представлена на рис. 5.5.

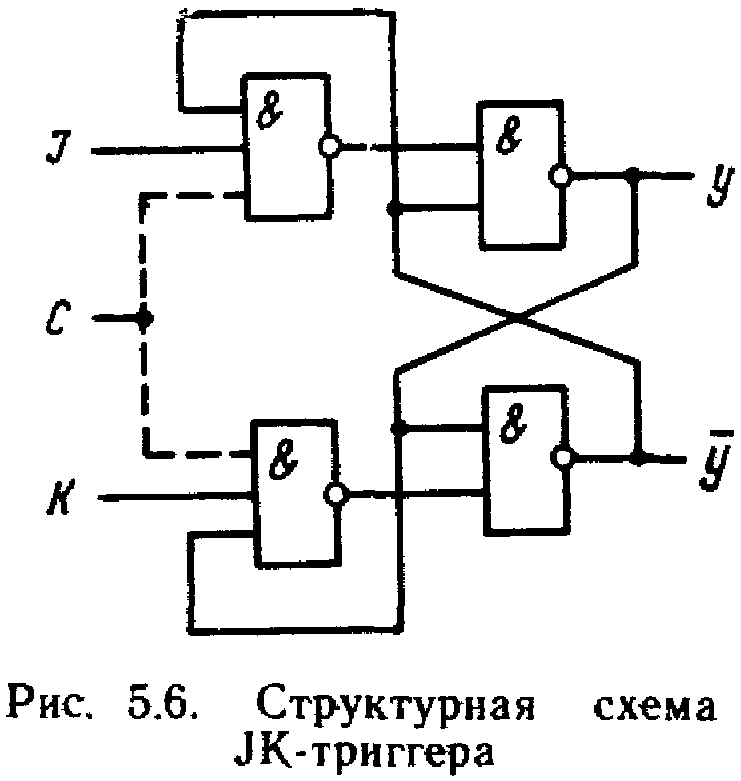

Схему JK-триггера можно получить добавлением к бистабильной ячейке схемы управления, которая наряду с входными логическими сигналами J и К посредством связи выходов с входами воспринимает также сигналы, имеющиеся на выходах триггера (рис. 5.6).

Для нормальной работы триггера длительность управляющих сигналов J и К должна быть меньше времени переключения триггера. В противном случае при J = = K = 1 схема будет непрерывно переходить из одного состояния в другое до тех пор, пока на одном из входов не появится сигнал логического 0. Это является недостатком данной схемы триггера (схема на рис. 5.5 лишена его), однако благодаря простоте она находит широкое применение. Синхронные JK-триггеры получают из асинхронных добавлением входа для тактовых импульсов и схемы управления, в которой блокируются основные входы триггера при отсутствии тактового сигнала. Пример подключения тактового входа показан на рис. 5.6 штриховой линией.

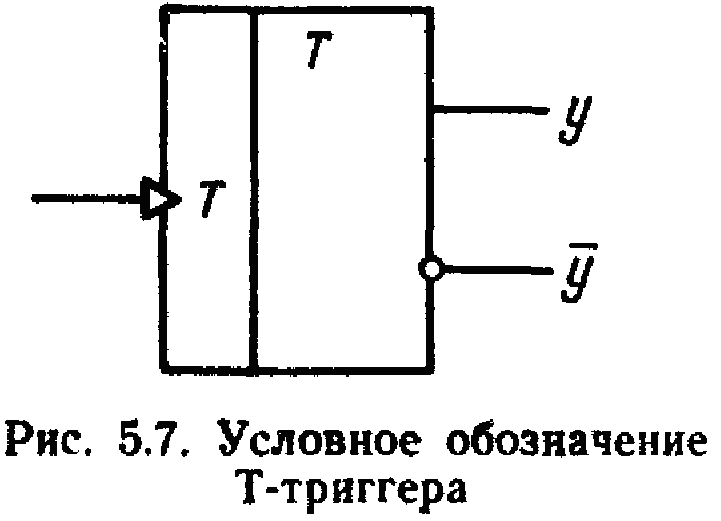

Т-триггеры. Данные триггеры имеют один информационный вход и работают в счетном режиме (рис. 5.7).

Переключение триггера из одного состояния в другое происходит каждый раз, когда на его входе действует сигнал логической 1 (см. табл. 5.1). Поэтому Т-триггер называют также счетным триггером. Структура асинхронного Т-триггера представлена на рис. 5.8.

В интегральном исполнении в виде самостоятельных изделий Т-триггеры не выпускают, так как они могут быть получены простым преобразованием других триггерных схем. Наиболее часто Т-триггер образуют из JK-триггера объединением входов последнего (рис. 5.9).

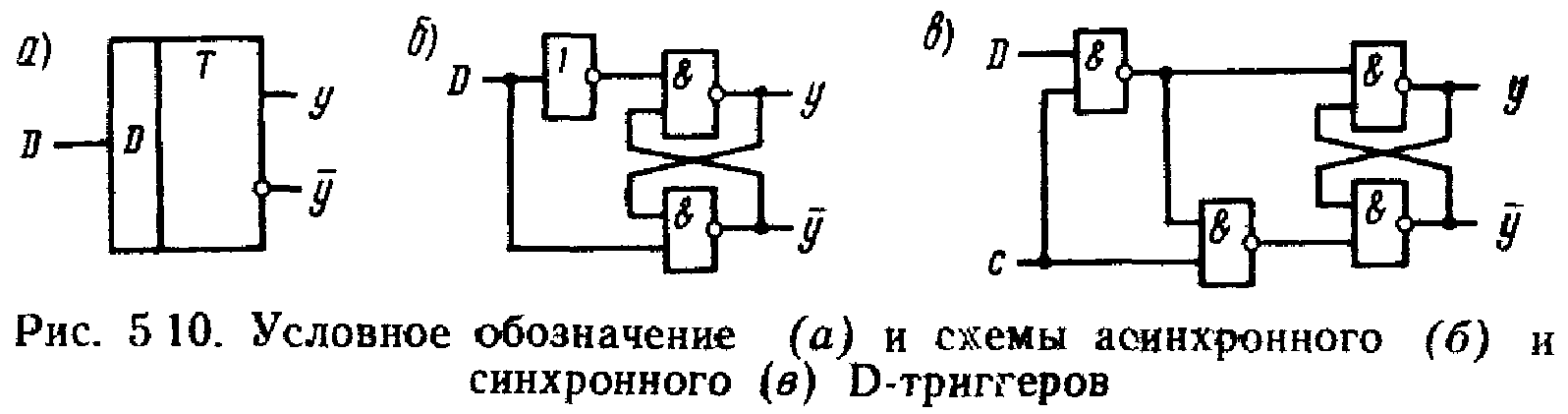

D-триггеры. Эти триггеры (рис. 5.10) представляют собой запоминающие элементы с одним входом и предназначены для задержки логического сигнала.

Из табл. 5.1 следует, что сигнал на выходе D-триггера в такте п + 1 повторяет значение входного сигнала в предыдущем такте п и сохраняет (запоминает) это состояние до следующего такта. Иначе говоря, D-триггер выполняет роль линии задержки и поэтому (единственный среди триггеров) относится к классу элементов памяти без фиксации воздействия. Иногда D-триггер называют триггером-задержкой, или триггером-защелкой.В асинхронном триггере задержка определяется параметрами схемы, а в синхронном триггере – периодом следования тактовых импульсов.

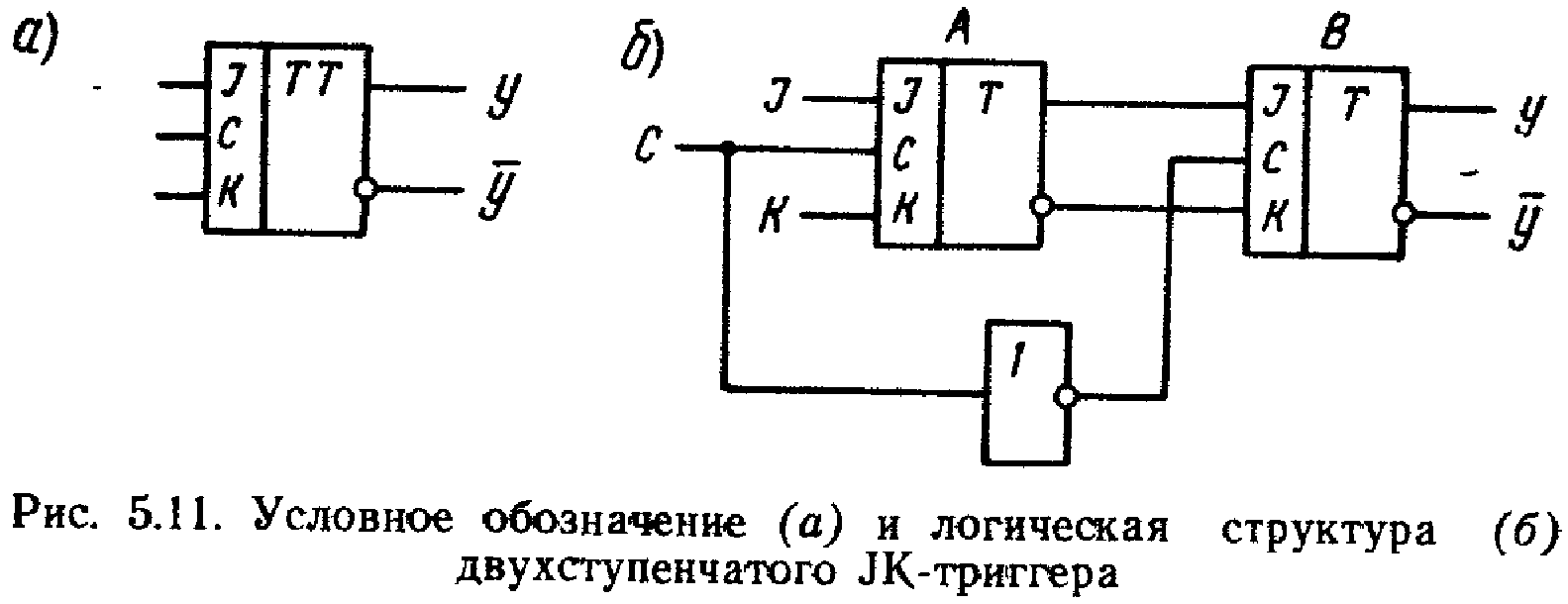

Двухступенчатые тактируемые триггеры. В микроэлектронике широко используют триггеры данного типа (рис. 5.11).

Они содержат две

ячейки памяти, информация в которые

записывается последовательно в разные

моменты времени. Работает триггер так.

Ввод информации в первую ступень триггера

(триггер А)

происходит с поступлением тактового

импульса С.

Выходы у

и

![]() в этом случае не изменяют своих значений,

так как триггерВ

второй ступени в это время заблокирован

сигналом с выхода инвертора, вход

которого подключен к тактовой шине.

После исчезновения тактового импульса

вход триггера первой ступени блокируется,

а триггер второй ступени принимает то

состояние, в котором находится триггер

первой ступени. В это время и происходит

изменение значений выходных сигналов

двухступенчатого триггера. Такие

триггеры также часто используют и в

синхронных системах, имеющих две тактовые

шины С1

и С2.

В этом случае тактовый вход триггера

первой ступени подключается к первой

тактовой шине, а тактовый вход триггера

второй ступени — ко второй.

в этом случае не изменяют своих значений,

так как триггерВ

второй ступени в это время заблокирован

сигналом с выхода инвертора, вход

которого подключен к тактовой шине.

После исчезновения тактового импульса

вход триггера первой ступени блокируется,

а триггер второй ступени принимает то

состояние, в котором находится триггер

первой ступени. В это время и происходит

изменение значений выходных сигналов

двухступенчатого триггера. Такие

триггеры также часто используют и в

синхронных системах, имеющих две тактовые

шины С1

и С2.

В этом случае тактовый вход триггера

первой ступени подключается к первой

тактовой шине, а тактовый вход триггера

второй ступени — ко второй.

На практике наибольшее распространение получили RS, JK и D-триггеры. Е, R и S-триггеры применяют редко. Их структуры можно получить незначительным преобразованием структуры RS-триггера.