- •Конспект лекций

- •190402 – «Автоматика, телемеханика и связь на железнодорожном транспорте»

- •1. Общие сведения

- •1.1. Характеристика дискретных элементов

- •1.2. Контактные и бесконтактные дискретные элементы

- •1.3. Классификация дискретных устройств

- •2. Функции алгебры логики

- •2.1. Определение и задание функций алгебры логики

- •2.2. Функции алгебры логики одной и двух переменных и их реализация

- •2.3. Базис: конъюнкция, дизъюнкция, инверсия

- •2.4. Нормальные формы функций алгебры логики

- •2.5. Минимизация функций алгебры логики. Метод Квайна – Мак-Класки

- •2.6. Геометрический метод минимизация функций алгебры логики

- •2.7. Минимизация функций алгебры логики методом карт Карно

- •3. Анализ и синтез комбинационных устройств

- •3.1. Анализ комбинационных дискретных устройств

- •3.2. Синтез комбинационных дискретных устройств

- •3.3. Примеры синтеза специальных комбинационных схем

- •3.4. Анализ релейных схем на графике

- •4. Структурный синтез дискретных устройств с памятью

- •4.1. Общая структура дискретного устройства с памятью

- •4.2. Виды элементов памяти

- •4.3. Анализ дискретных устройств с памятью

- •4.4. Этапы синтеза дискретного устройства с памятью

- •4.5. Системы счисления. Двоичная система счисления

- •5. Логическое проектирование цифровых схем

- •5.1 Асинхронные и синхронные триггеры

- •5.2. Синтез счетчиков

- •6. Синтез надежных дискретных устройств

- •6.1. Методы повышения надежности дискретных устройств

- •6.2. Резервирование контактных схем

- •6.3. Избыточные устройства с восстанавливающими органами

- •6.4. Надежные комбинационные схемы

- •7. Синтез схем дискретных устройств с исключением опасных отказов

- •7.1. Понятие об опасном отказе

- •7.2. Опасные отказы в комбинационных схемах

- •7.3. Методы построения безопасных комбинационных схем

- •7.4. Логические элементы безопасных систем железнодорожной автоматики и телемеханики

- •7.5. Принципы построения надежных и безопасных дискретных систем

6.4. Надежные комбинационные схемы

Рассмотрим вопросы повышения надежности комбинационных схем, построенных на функциональных логических элементах (ЛЭ). Во внутреннюю структуру ЛЭ входят отдельные детали: транзисторы, диоды, резисторы и т. д. Повреждение какой-либо детали может изменить логическую функцию, реализуемую ЛЭ. Очевидно, что надежность ЛЭ может быть повышена последовательным или параллельным соединением входящих в его структуру деталей.

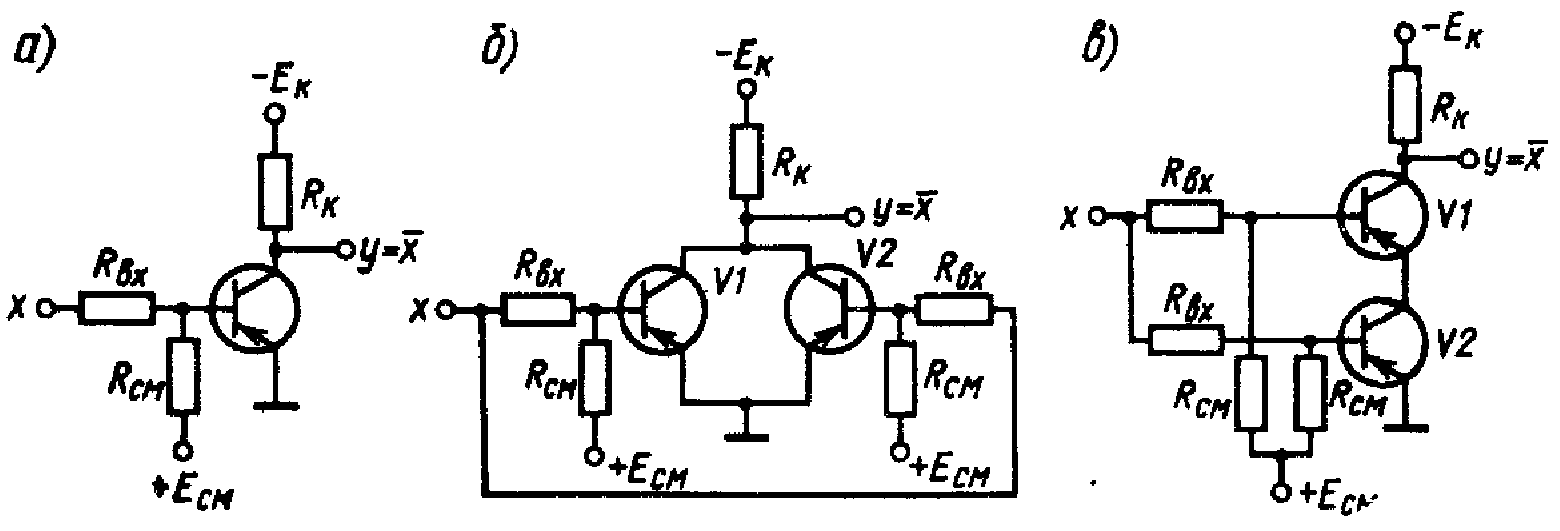

На рис. 6.19 приведены схемы резервирования транзистора в логическом элементе НЕ. При параллельном включении транзисторов элемент работает правильно при обрыве, а при последовательном – при коротком замыкании одного из транзисторов. Поэтому параллельное резервирование транзистора повышает надежность ЛЭ относительно ошибок на выходе типа 0→1, а последовательное – относительно ошибок 1→0.

Рис. 6.19. Схема логического элемента НЕ неизбыточного (а), с параллельным (б) и последовательным (в) включением транзисторов

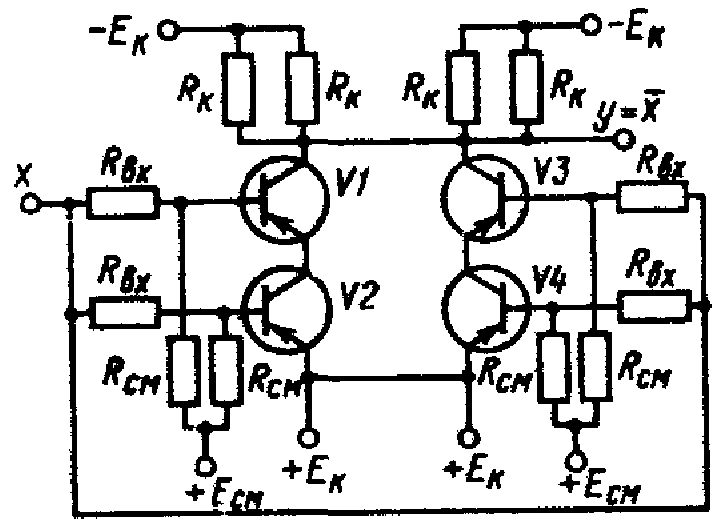

Следовательно, для увеличения надежности ЛЭ относительно ошибок обоих типов необходимо транзисторы соединить последовательно-параллельно (рис. 6.20).

Рис. 6.20. Принципиальная схема резервированного логического элемента НЕ

В этой схеме четыре транзистора V1 – V4 включены попарно, последовательно и параллельно между собой. Входы всех четырех транзисторов объединены. Нагрузка транзисторов выполнена в виде четырех сопротивлений Rк и является общей для обеих параллельных ветвей транзисторов. Питание в схему (+Ек, –Ек, Есм) подается на два разных зажима во избежание выхода из строя элемента при обрыве одного из проводов питания.

Данная схема обеспечивает правильное функционирование элемента при любом повреждении одной детали или одиночном обрыве связи между деталями, за исключением обрывов входа х и выхода у. Например, короткое замыкание V1 не нарушает правильную работу ЛЭ, так как при этом V2 работает нормально. Обрыв V1 исключает из работы левую ветвь (V1 и V2) схемы, но остается работоспособной правая ветвь (V3 и V4) и т. д.

Применение резервированных ЛЭ (аналогичных рассмотренному элементу НЕ) позволяет просто строить надежные логические схемы: достаточно в неизбыточной схеме каждый ЛЭ заменить его резервированной модификацией. В этом случае можно добиться существенного увеличения надежности относительно отказов деталей внутренней структуры ЛЭ, но обрывы соединений между входами и выходами элементов схемы будут приводить к выходу ее из строя. В то же время следует отметить, что вероятность указанных обрывов в современных устройствах остается довольно высокой, так как обрывы связаны с некачественной пайкой и нарушением контакта в механических разъемах. Число же соединений в схемах, как правило, очень велико.

Влияние обрывов на правильную работу схемы исключается в комбинационных схемах с многократными связями. В них каждый ЛЭ выполняет логические операции над тождественными копиями входных сигналов, которые поступают по пучкам входных связей.

Назовем собственными ошибками ЛЭ ошибки на его выходе, вызванные повреждениями деталей внутренней структуры элемента, а входными ошибками – искажения сигналов на входе из-за повреждений деталей в предыдущих каскадах устройства или повреждений соединительных линий. Каждый ЛЭ в избыточной схеме с многократными связями должен обладать свойствами логического элемента для выполнения логических функций и восстанавливающего органа для восстановления правильного сигнала коррекцией входных или собственных ошибок.

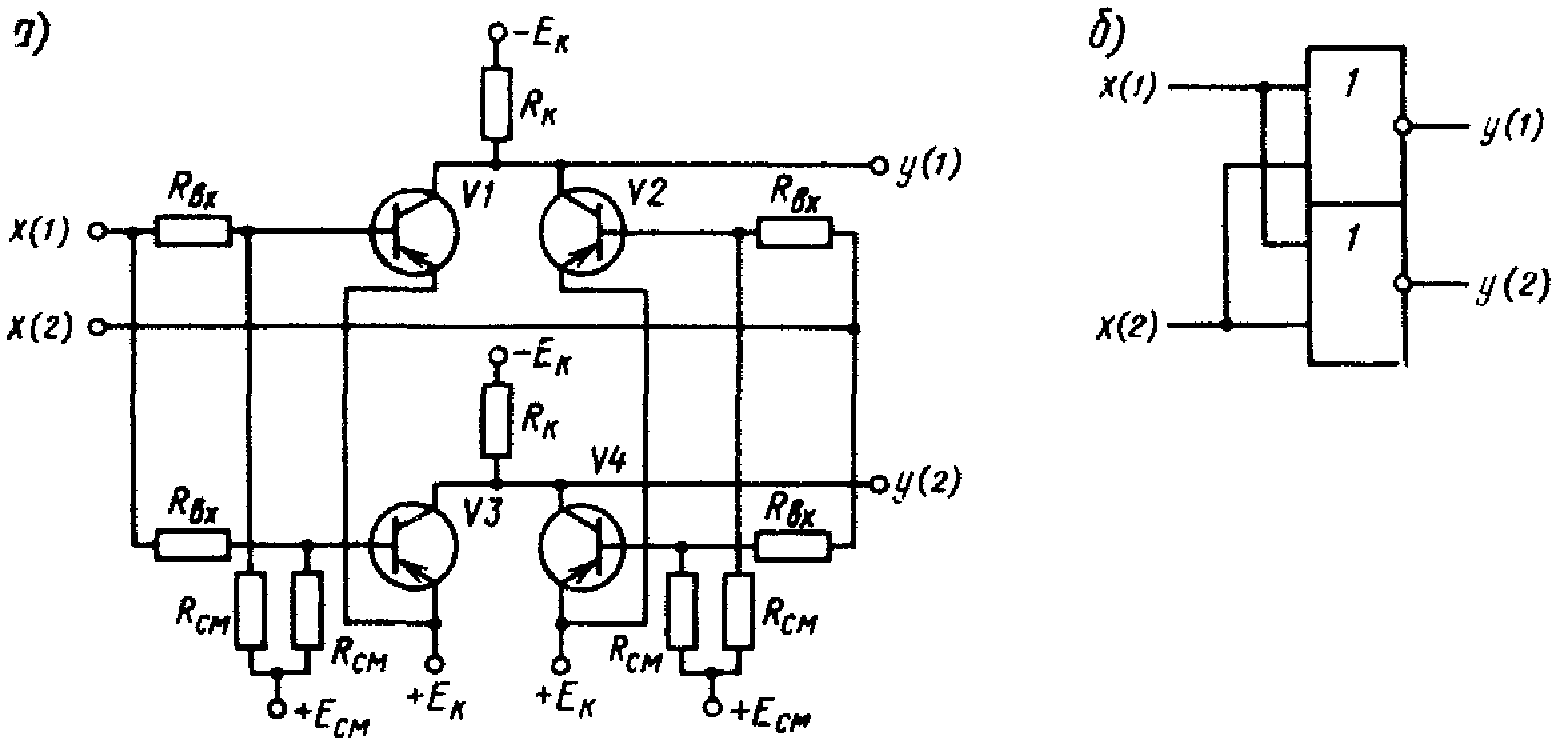

Резервированный элемент НЕ с двойными связями (рис. 6.21) состоит из двух отдельных элементов НЕ, в которых осуществлено параллельное резервирование транзисторов. Входные и выходные сигналы элемента передаются по двум линиям. В исправном состоянии х(1) = х(2) и у(1) = у(2).

Рис. 6.21. Схема (а) и условное обозначение (б) резервированного элемента НЕ с двойными связями

Схема, построенная на соединенных между собой элементах с двойными связями (рис. 6.22) работает правильно при любых одиночных повреждениях деталей ЛЭ и обрыве одной из параллельных линий, связывающих между собой два элемента. Действительно, в самом элементе все одиночные повреждения сводятся к обрыву или короткому замыканию соответствующего транзистора. Благодаря параллельному соединению транзисторов обрыв одного из них не нарушает правильную работу элемента. Так как при обрывах транзисторов на выходе элемента возможна ошибка типа 0→1, то элемент, таким образом, исправляет собственные ошибки такого типа.

Рис. 6.22. Схема последовательного соединения элементов НЕ с двойными связями

При коротком замыкании одного из транзисторов на одном из выходов элемента появляется ложный сигнал логического 0. Рассмотрим работу приведенной на рис. 6.22 схемы в этом случае. Пусть на входах элемента ЛЭ1 действуют сигналы х(1) = х(2) = 0 и при этом происходит короткое замыкание V1 (см. рис. 6.21, а). Тогда выходные сигналы ЛЭ1 (см. рис. 6.22) принимают значения у(1) = 0, у(2) = 1 (так как транзисторы V3 и V4 исправны и закрыты). Данные сигналы подаются соответственно на входы х(1) и х(2) элемента ЛЭ2. Таким образом, на вход х(1) ЛЭ2 поступает ложный сигнал логического 0, а на вход х(2) – правильный сигнал логической 1. Но так как вход х(2) элемента (см. рис. 6.21) связан с входами транзисторов V2 и V4, выходы которых в свою очередь соединены с различными выходами элемента, то на этих выходах будет правильный сигнал логического 0 [у(1) = у(2) = 0]. Следовательно, возникающая на выходе элемента ЛЭ1 ошибка типа 1→0 исправляется элементом последующего каскада ЛЭ2. Очевидно, что так же исправляется ошибка, вызванная обрывом соединения между выходом у(1) ЛЭ1 и входом х(1) ЛЭ2.

Таким образом, описанный элемент наряду с реализацией логической функции НЕ исправляет также собственные ошибки типа 0→1 и входные ошибки типа 1→0. Так как собственные ошибки элемента типа 1→0 исправляются только в последующем каскаде схемы, последний ее каскад следует строить на других элементах, в которых исправляются ошибки обоих типов (например, на элементах, аналогичных показанному на рис. 6.20).

Хорошие результаты

по повышению надежности дают схемы с

тройными связями, в которых для исправления

ошибок используется мажоритарная

функция

![]() (рис. 6.23).

(рис. 6.23).

Рис. 6.23. Схема логической структуры резервированного элемента И

с тройными связями

Сигналы передаются

по пучку из трех линий. На входах элемента

сначала осуществляется исправление

сигналов элементами

![]() ,

а затем реализация логической операции.

Элемент корректирует входные ошибки

обоих типов, собственные одиночные

ошибки исправляются на входах последующего

каскада. Такие элементы строят на

резистивно-транзисторных схемах, в

которых мажоритарная функция реализуется

на входных резисторах элементов.

,

а затем реализация логической операции.

Элемент корректирует входные ошибки

обоих типов, собственные одиночные

ошибки исправляются на входах последующего

каскада. Такие элементы строят на

резистивно-транзисторных схемах, в

которых мажоритарная функция реализуется

на входных резисторах элементов.

В схемах с двойными и тройными связями эффект исправления ошибок достигается благодаря специальным свойствам используемых ЛЭ. Такие свойства получают усложнением внутренней структуры элементов. Однако в распоряжении разработчика могут не всегда быть такие элементы. Поэтому особый интерес представляют схемы с учетверенными связями, в которых никаких особых требований к ЛЭ не предъявляется.

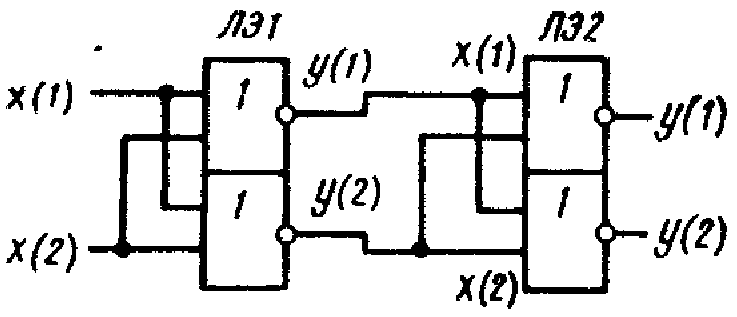

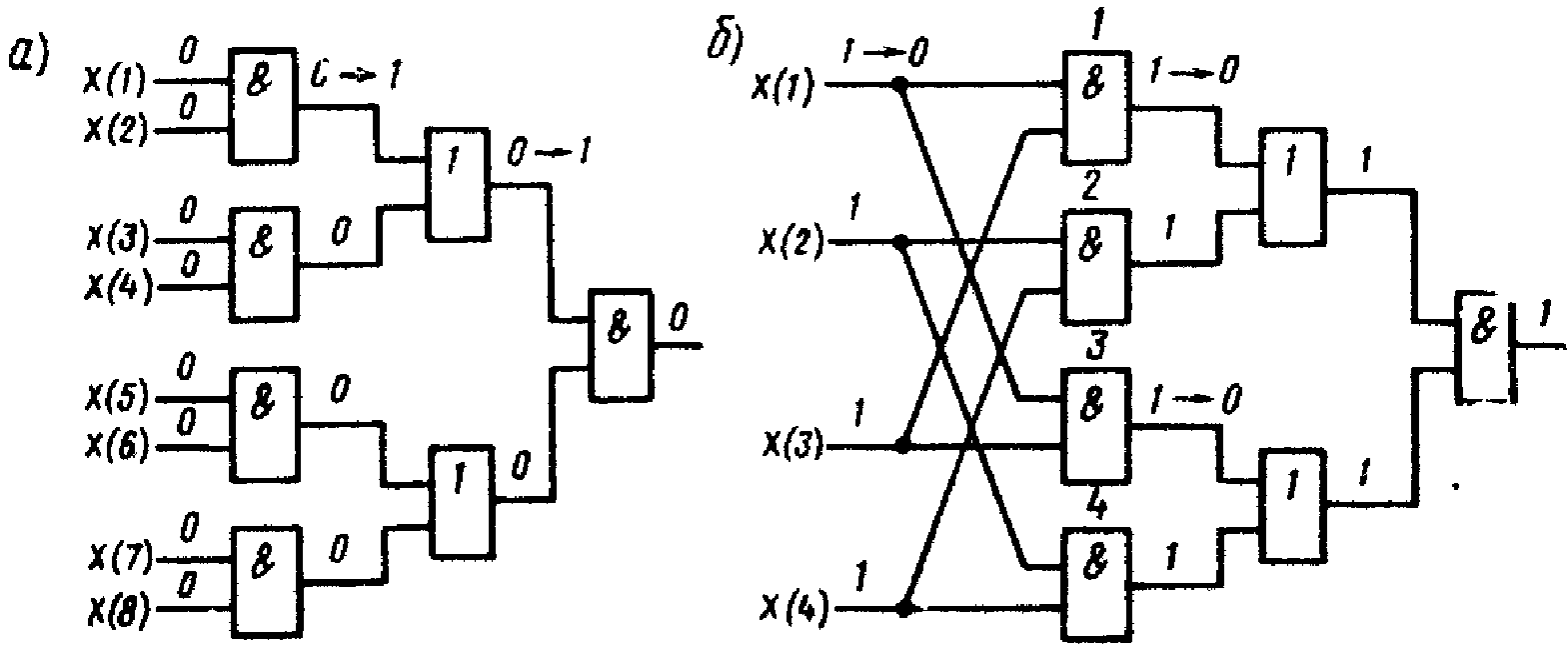

Рассмотрим идею метода учетверения. Он использует естественные исправляющие свойства элементов, на входы которых многократно подан один и тот же сигнал. На рис. 6.24, а показана реакция на ошибки на входах элемента И.

Рис. 6.24. Схемы исправления ошибок логическими элементами

Ошибка типа 1→0 передается на выход, а ошибка типа 0→1 исправляется элементом. Элемент ИЛИ, наоборот, исправляет ошибку типа 1→0 (рис. 6.24, б). Так как элементы И и ИЛИ исправляют ошибки разных типов, то возникает возможность исправления ошибок обоих типов последовательным включением этих элементов. Схема, приведенная на рис. 6.24, в, исправляет ошибки обоих типов на входах элементов И. Ошибки типа 0→1 исправляются самими элементами И, а ошибки типа 1→0 – элементом ИЛИ, который составляет второй каскад схемы. Для того чтобы добиться данного свойства схемы, пришлось установить два элемента И, а число независимых линий, по которым передается входная переменная, увеличить до четырех. В полученной схеме исправляются все ошибки на входах элементов, кроме ошибок типа 0→1 на входах элемента ИЛИ. Для исправления данных ошибок в схему следует ввести еще большую избыточность, а именно третий каскад схемы (рис. 6.25, а). Ошибка типа 0→1 на входе элемента ИЛИ исправляется на выходе элемента И третьего каскада. Число элементов И первого каскада схемы возросло до четырех, число независимых копий входного сигнала – до восьми. Дальнейший рост числа каскадов схемы вызывает увеличение числа элементов в каждом предыдущем каскаде и числа независимых входных сигналов. Однако все ошибки могут быть исправлены схемами с четырьмя одинаковыми элементами в каждом каскаде благодаря специальному соединению между собой входов элементов одного каскада. Схема (рис. 6.25, б) обладает теми же свойствами по исправлению ошибок, что и схема, приведенная на рис. 6.25, а. На этой схеме объединены входы элементов первого каскада. В результате вместо восьми потребовалось четыре независимых входных сигнала.

Рис. 6.25. Схемы логические трехкаскадные

Объединение входов элементов каскада приводит к появлению на выходах каскада двойной ошибки, обусловленной одиночной ошибкой.

Например, ошибка 1→0 на входе х(1) (см. рис. 7.25, б) вызывает такую же ошибку на выходах элементов 1 и 3 первого каскада схемы. Однако обе эти ошибки исправляются следующим каскадом схемы, так как поступают на входы различных его элементов. Очевидно, что если бы обе ошибки поступили на вход одного элемента ИЛИ второго каскада, это вызвало бы появление ошибки на его выходе, а следовательно, и на выходе всей схемы.

Рассмотрим трехкаскадную схему с учетверенными связями (рис. 6.26).

Рис. 6.26. Схема И-ИЛИ-НЕ с учетверенными связями

Элементы И первого каскада имеют по два сдвоенных входа, т. е., помимо задачи исправления ошибок, они в данном случае выполняют и свою основную задачу – реализацию логических функций. Аналогично могут быть включены элементы и других каскадов (соответствующие их входы не показаны для упрощения рисунка). Входы элементов каждого каскада объединены в соответствии с определенной формулой. Для первого каскада имеет место формула [1, 2 – 3, 4] (объединены входы первого и второго, а также третьего и четвертого элементов), для второго каскада – формула [1, 3 – 2, 4] и для третьего каскада – формула [1, 4 – 2, 3].

Необходимым условием исправления ошибок является объединение входов элементов двух соседних каскадов схемы в соответствии с различными формулами. Это обеспечивает невозможность попадания двух ошибок, возникающих на выходе какого-либо каскада в результате одиночной ошибки предыдущего каскада, на входы одного и того же элемента последующего каскада. В этом случае (как было показано на примере схемы рис. 6.25, б) двойные ошибки исправляются. Если в соответствии с логической структурой схемы необходимо соединить последовательно несколько каскадов из одинаковых элементов, их включают по одной и той же формуле. В этом случае ошибки обоих каскадов исправляются первым последующим каскадом из элементов другого типа.

Вернемся к схеме, приведенной на рис. 6,24, в. Включим на выходе элементов И первого каскада инверторы (см. рис. 6.24, г). Инвертор меняет на противоположный тип ошибки, имеющейся на его входе. Поэтому в данной схеме для исправления ошибок на входах элементов первого каскада после инверторов вместо элемента ИЛИ следует установить элемент И. Из этого следует, что схемы (см. рис. 6.24, д), представляющие собой последовательное включение каскадов из элементов И-НЕ (или ИЛИ-НЕ) обладают способностью исправлять одиночные ошибки обоих типов.

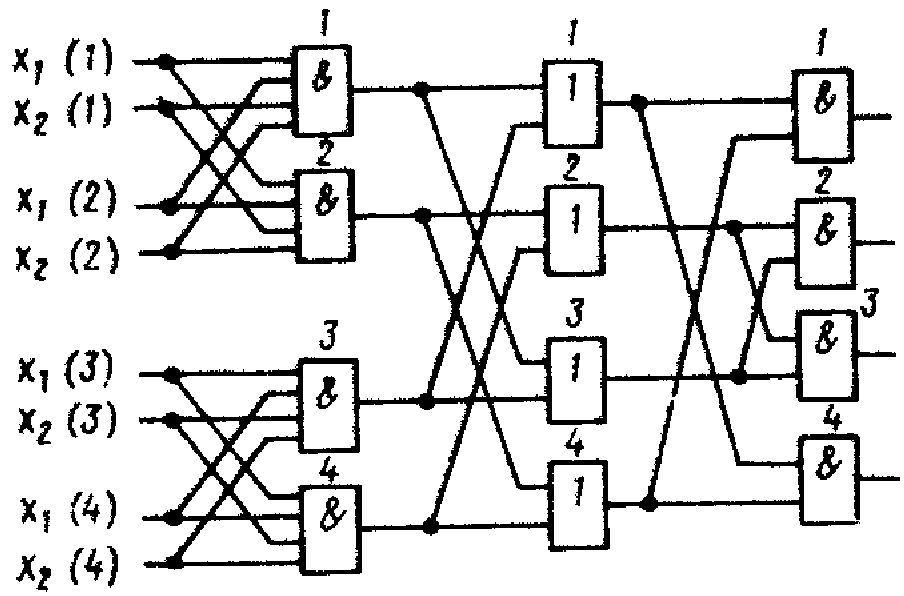

Избыточную комбинационную схему с учетверенными связями (рис. 6.27) строят по структуре неизбыточной схемы заменой каждого ее элемента каскадом из четырех соответствующих элементов со сдвоенными входами.

Рис. 6.27. Схема из двух каскадов элементов ИЛИ-НЕ

с учетверенными связями

Необходимо правильно

чередовать формулы объединения входов

элементов различных каскадов. Элементы

двух последних каскадов схемы должны

исправлять ошибки обоих типов. На рис.

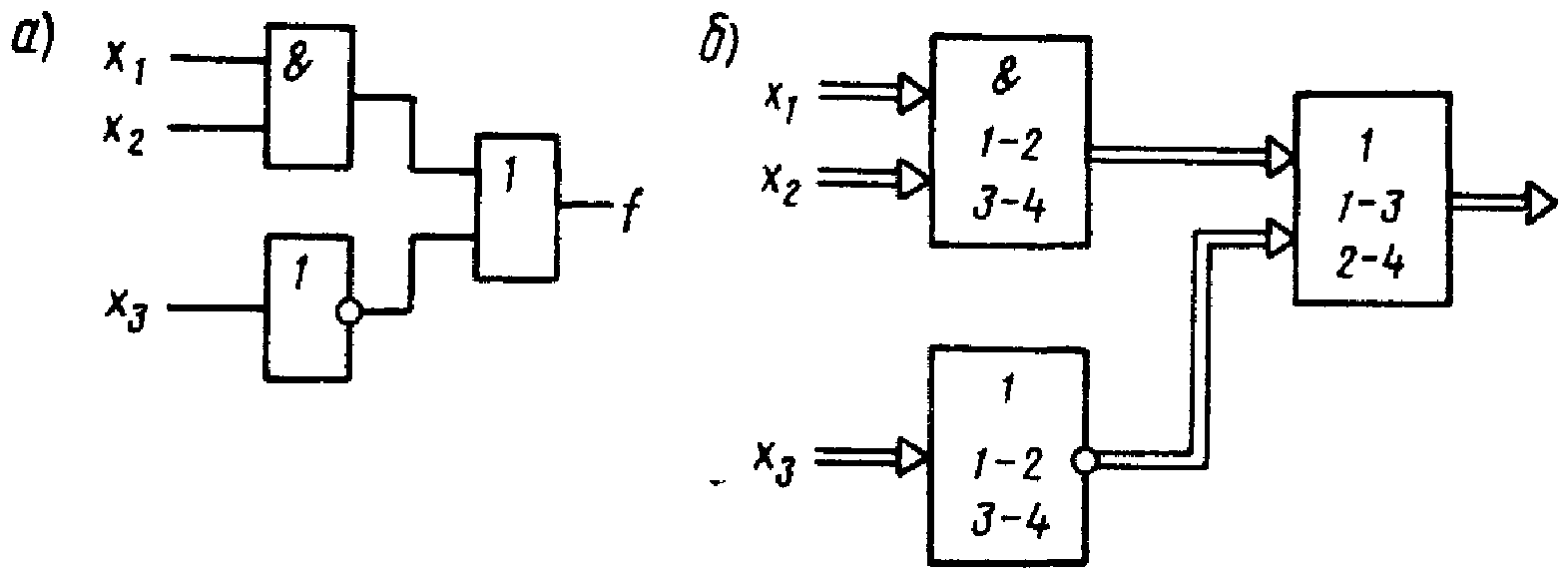

6.28 показан пример построения схемы,

реализующей функцию

![]() .

В ней для каждого элемента с учетверенными

связями указана формула объединения

входов.

.

В ней для каждого элемента с учетверенными

связями указана формула объединения

входов.

Рис. 6.28. Неизбыточный (а) и избыточный (б) варианты избыточной схемы с учетверенными связями