- •Схемотехника эвм

- •Часть 2

- •Содержание

- •8. Регистры

- •8.1. Назначение и классификация регистров

- •8.2. Регистры памяти

- •8.3. Буферы данных

- •8.4. Регистры сдвига

- •Кольцевые счетчики

- •9. Мультиплексоры и демультиплексоры

- •9.1. Общие сведения

- •9.2. Мультиплексоры

- •9.3. Демультиплексоры

- •10. Шифраторы и дешифраторы

- •10.1. Шифраторы

- •10.2. Дешифраторы

- •11. Арифметические устройства

- •11.1. Сумматоры

- •Четвертьсумматор

- •Полусумматор

- •Полный одноразрядный двоичный сумматор

- •Сумматоры с последовательным переносом

- •11.2. Инкрементор

- •11.3. Вычитатели (субтракторы)

- •11.4. Компараторы

- •Основные характеристики компараторов

- •Компараторы аналоговых сигналов

- •Компараторы цифровых сигналов

- •Компаратор на базе сумматора

- •11.5. Арифметико-логические устройства

- •12. Импульсные устройства на имс

- •12.1. Формирователи импульсов

- •12.2. Схемы нормализации импульсов

- •12.3. Схемы укорачивания импульсов

- •12.4. Схемы задержки импульса

- •12.5. Одновибраторы

- •12.6. Генераторы тактовой частоты

- •13. Запоминающие устройства

- •13.1. Общие характеристики устройств

- •13.2. Запоминающие элементы постоянных зу

- •13.3. Оперативные запоминающие устройства

- •13.3.1. Динамические зу

- •13.3.2. Статические зу

- •14. Аналого-цифровые и цифро-аналоговые преобразователи

- •14.1. Общие сведения

- •14.2. Цифро-аналоговые преобразователи

- •14.3. Аналого-цифровые преобразователи

- •14.3.1. Характеристики и параметры ацп

- •14.3.2. Ацп последовательного счета

- •14.3.3. Параллельный ацп

- •14.3.4. Сигма-дельта ацп

- •Заключение

- •Библиографический список

- •Приложение 1 Перечень стандартов

- •Основные стандарты ескд

- •Система технологической документации

- •Стандарты системы информационно-библиографической документации

- •Система стандартов по безопасности труда

- •Разработка и постановка продукции на производство

- •Система стандартов программной документации

- •Основополагающие стандарты гсп

- •Приложение 2

- •Цифровых устройств

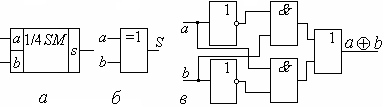

Четвертьсумматор

Простейшим двоичным суммирующим элементом является четвертьсумматор. Происхождение названия этого элемента следует из того, что он имеет в два раза меньше выходов и в два раза меньше строк в таблице истинности по сравнению с полным двоичным одноразрядным сумматором. Наиболее известны для данной схемы названия: элемент "сумма по модулю 2" и элемент "исключающее ИЛИ". Схема (рис. 11.1) имеет два входа а и b для двух слагаемых и один выход S для суммы. Работу ее отражает таблица истинности (табл. 11.1), а соответствующее уравнение имеет вид:

![]()

|

a |

b |

S |

|

0 |

0 |

0 |

|

0 |

1 |

1 |

|

1 |

0 |

1 |

|

1 |

1 |

0 |

аблица

11.1

аблица

11.1Рис. 11.1 Условное обозначение (а, б) и схема реализации четвертьсумматора (в)

На рис. 11.1 представлены условное графическое обозначение элемента и схема реализации в базисе И-ИЛИ-НЕ. Состояния четвертьсумматора при различных значениях входных сигналов представлены в таблице истинности (табл. 11.1). Здесь старшая единица, возникающая при суммировании двух единиц, не учитывается. Данный элемент выпускается в виде интегральных схем типа ЛП5 (серии 133, 155, 530, 531, 533, 555, 1531, 1533); ЛП12 (555); ЛП107 (100, 500, 1500); ЛП2 (561, 564); ЛП14 (1561) и т. п.

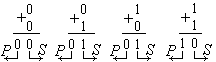

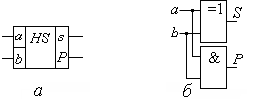

Полусумматор

Полусумматор (рис. 11.2) имеет два входа a и b для двух слагаемых и два выхода: S сумма и CR (или P) – перенос. Обозначением полусумматора служат буквы HS (half sum – полусумма).

Два одноразрядных числа при сложении в двоичной системе дают такие результаты:

Таблица 11.2

|

a |

b |

P |

S |

|

0 |

0 |

0 |

0 |

|

0 |

1 |

0 |

1 |

|

1 |

0 |

0 |

1 |

|

1 |

1 |

1 |

0 |

а

а

b

Эти результаты можно представить в виде таблицы (табл. 11.2). В соответствии с таблицей работу полусумматора можно описать следующими уравнениями:

![]() (2)

(2)

Рис. 11.2. Условное обозначение (а) и схема реализации полусумматора (б)

Уравнения показывают, что выражение для выхода S и столбец таблицы истинности совпадают с уравнениями и таблицей, описывающими работу элемента исключающее ИЛИ, а для выхода Р – с уравнением и таблицей элемента И. Условное графическое обозначение и логическая структура полусумматора представлены на рис. 11.2. Полусумматор используется, обычно, только для суммирования младших разрядов многоразрядных двоичных чисел.

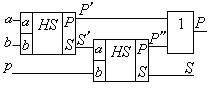

Полный одноразрядный двоичный сумматор

Одноразрядный сумматор имеет три входа: a, b для двух слагаемых и p для входного переноса из предыдущего (более младшего) разряда и два выхода: S сумма и P перенос в следующий (более старший) разряд. Обозначением полного двоичного сумматора служат буквы SM (рис. 11.3). Работу его отражает таблица истинности (табл. 11.3).

Можно отметить два момента. Первый: в табл. 11.2 и 11.3 выходные сигналы P и S не случайно расположены именно в такой последовательности. Это подчеркивает, что PS рассматривается как двухразрядное двоичное число, например, 1 + 1 = 210 = 102 , т. е. P = 1, а S = 0 или 1 + 1 + 1 = 310 = 112, т. е. P = 1 и S = 1. Второй: выходные сигналы P и S полного двоичного сумматора относятся к классу самодвойственных функций алгебры логики. Самодвойственными называют функции, инвертирующие свое значение при инвертировании всех переменных, от которых они зависят. Следует обратить внимание на то, что P и S для четвертьсумматора и полусумматора не являются самодвойственными функциями!

|

Рис. 11.3. Условное обозначение полного одноразрядного сумматора |

Таблица 11.3

|

Преимущества, вытекающие из этого свойства полного двоичного сумматора, можно увидеть при анализе возможностей, например, интегральной схемы типа 155ИМ1 [8, 12].

У![]() равнения,

описывающие работу полного двоичного

сумматора, представленные в совершенной

дизъюнктивной нормальной форме (СДНФ),

имеют вид:

равнения,

описывающие работу полного двоичного

сумматора, представленные в совершенной

дизъюнктивной нормальной форме (СДНФ),

имеют вид:

(3)

(4)

При практическом проектировании сумматора уравнения (3) и (4) могут быть преобразованы к виду, удобному для реализации на заданных логических элементах с некоторыми ограничениями (по числу логических входов и др.) и удовлетворяющему предъявляемым к сумматору требованиям по быстродействию.

Н![]() апример,

преобразуем уравнения (3) и (4) следующим

образом:

апример,

преобразуем уравнения (3) и (4) следующим

образом:

Из выражений (5) и (6) следует, что полный двоичный сумматор может быть реализован на двух полусумматорах и одном двухвходовом элементе ИЛИ. Соответствующая схема приведена на рис. 11.4.

Рис. 11.4. Схема одноразрядного полного сумматора на полусумматорах