- •Схемотехника эвм

- •Часть 2

- •Содержание

- •8. Регистры

- •8.1. Назначение и классификация регистров

- •8.2. Регистры памяти

- •8.3. Буферы данных

- •8.4. Регистры сдвига

- •Кольцевые счетчики

- •9. Мультиплексоры и демультиплексоры

- •9.1. Общие сведения

- •9.2. Мультиплексоры

- •9.3. Демультиплексоры

- •10. Шифраторы и дешифраторы

- •10.1. Шифраторы

- •10.2. Дешифраторы

- •11. Арифметические устройства

- •11.1. Сумматоры

- •Четвертьсумматор

- •Полусумматор

- •Полный одноразрядный двоичный сумматор

- •Сумматоры с последовательным переносом

- •11.2. Инкрементор

- •11.3. Вычитатели (субтракторы)

- •11.4. Компараторы

- •Основные характеристики компараторов

- •Компараторы аналоговых сигналов

- •Компараторы цифровых сигналов

- •Компаратор на базе сумматора

- •11.5. Арифметико-логические устройства

- •12. Импульсные устройства на имс

- •12.1. Формирователи импульсов

- •12.2. Схемы нормализации импульсов

- •12.3. Схемы укорачивания импульсов

- •12.4. Схемы задержки импульса

- •12.5. Одновибраторы

- •12.6. Генераторы тактовой частоты

- •13. Запоминающие устройства

- •13.1. Общие характеристики устройств

- •13.2. Запоминающие элементы постоянных зу

- •13.3. Оперативные запоминающие устройства

- •13.3.1. Динамические зу

- •13.3.2. Статические зу

- •14. Аналого-цифровые и цифро-аналоговые преобразователи

- •14.1. Общие сведения

- •14.2. Цифро-аналоговые преобразователи

- •14.3. Аналого-цифровые преобразователи

- •14.3.1. Характеристики и параметры ацп

- •14.3.2. Ацп последовательного счета

- •14.3.3. Параллельный ацп

- •14.3.4. Сигма-дельта ацп

- •Заключение

- •Библиографический список

- •Приложение 1 Перечень стандартов

- •Основные стандарты ескд

- •Система технологической документации

- •Стандарты системы информационно-библиографической документации

- •Система стандартов по безопасности труда

- •Разработка и постановка продукции на производство

- •Система стандартов программной документации

- •Основополагающие стандарты гсп

- •Приложение 2

- •Цифровых устройств

10. Шифраторы и дешифраторы

10.1. Шифраторы

Шифратором называется комбинационное устройство, преобразующее унитарный код, подаваемый на входные шины, в соответствующий код на выходах устройства.

Задача шифратора – сформировать код. На вход шифратора могут подаваться различные сигналы: логический 0 или логическая 1 через контакты кнопок клавиатуры управления (кодируется состояние переключателей) или сигналы с других устройств, но во всех случаях происходит преобразование одного сигнала в n-разрядный код (преобразуется унитарный код в позиционный). В таблице истинности шифратора (табл. 10.1) позиционный код представлен двоичным кодом. На рис. 10.1 представлена схема шифратора на диодах.

Таблица 10.1

-

Унитарный код

Двоичный код

SB1

SB2

SB3

SB4

SB5

SB6

SB7

SB8

Q4

Q3

Q2

Q1

1

0

0

0

0

0

0

0

0

0

0

1

0

1

0

0

0

0

0

0

0

0

1

0

0

0

1

0

0

0

0

0

0

0

1

1

0

0

0

1

0

0

0

0

0

1

0

0

0

0

0

0

1

0

0

0

0

1

0

1

0

0

0

0

0

1

0

0

0

1

1

0

0

0

0

0

0

0

1

0

0

1

1

1

0

0

0

0

0

0

0

1

1

0

0

0

Рис. 10.1. Шифратор на диодах

В исходном состоянии, когда ни одна из кнопок не нажата, на всех выводах Q1–Q4 нулевой потенциал. После нажатия на одну из кнопок, например SB3, положительное напряжение, возникшее на делителях R1, R4 и R1, R5, через диоды VD3, VD4 поступает на шины Q1 и Q2. На выходе получается код 0011 – это код нажатой кнопки SB3.

Рассмотрим подробнее структуру микросхемы шифратора. Классический шифратор имеет m входов и n выходов, и при подаче сигналов на один из входов (обязательно на один и не более) на выходе узла появляется двоичный код номера возбужденного входа.

Число входов и выходов такого шифратора связано соотношением m = 2n.

Для построения шифратора можно использовать схемы ИЛИ – по одной на каждый выход. При этом схема разбивается на n простых фрагментов. К входу элементов ИЛИ каждого выходного разряда должны быть подключены те входы шифратора, в двоичном представлении номера которых есть единица в данном разряде. Так, к элементу ИЛИ младшего разряда формируемого выходного кода должны быть подключены все нечетные входы, поскольку у всех нечетных номеров и только у них в младшем разряде содержится единица. Функциональная схема такого шифратора представлена на рис. 10.2. Эту схему можно преобразовать по формулам де Моргана. В новом варианте вместо схем ИЛИ будут схемы И-НЕ.

Рис. 10.2. Функциональная схема шифратора

Выше рассмотрен случай использования унитарного кода, при подаче которого на шифратор возбуждается всегда только один его вход. Между тем, в реальных ситуациях возможны случаи, когда одновременно будут возбуждены два и более входа шифратора. Например, в случае ошибочного нажатия одновременно двух и более кнопок (клавиш) произойдёт наложение двух и более унитарных кодов. Для устранения неопределённости, шифратор должен выбрать и преобразовать код только одной кнопки (клавиши). Это достигается использованием схем выбора старшей единицы. В этом случае для преобразования будет выбран код кнопки, в котором 1 стоит на самой старшей позиции. Такая схема вместе с шифратором может входить в состав кодирующего узла.

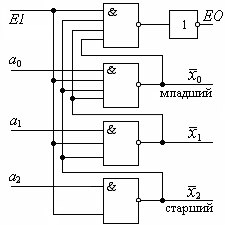

Схема выделения старшей единицы преобразует m-разрядное слово следующим образом: все старшие нули и самая старшая единица входного кода пропускаются на выход без изменения; все разряды более младшие, чем старшая единица, заменяются нулями. На схеме (рис. 10.3) на входы а0, а1, а2 поступает преобразуемое слово (а0 – младший разряд, а2 – старший разряд), на вход EI (от enable in) – входной сигнал разрешения. При EI = 1 схема работает следующим образом: любое число старших нулей порождает на выходах своих разрядов единицы и никак не влияет на работу элементов И-НЕ более младших разрядов. Любая самая старшая единица порождает на соответствующем выходе нуль (активный низкий уровень выхода) и запирает все более младшие элементы И-НЕ, устанавливая на их выходах не активный высокий уровень. При этом низкий уровень появляется и на выходе EO (от enable out) – выходе разрешения.

Рис. 10.3. Схема выделения старшей единицы

Если разрядность обрабатываемого слова (число входных сигналов) превышает разрядность схемы, то слово разбивается на группы и выход EO более старшей группы подается на вход EI более младшей. При таком включении единица, поступившая на любой вход любой группы, запрет не только все более младшие разряды своей группы, но по цепи EO–EI и все более младшие группы. На выходах всей схемы останется только самая старшая единица входного слова, представленная активным низким уровнем.

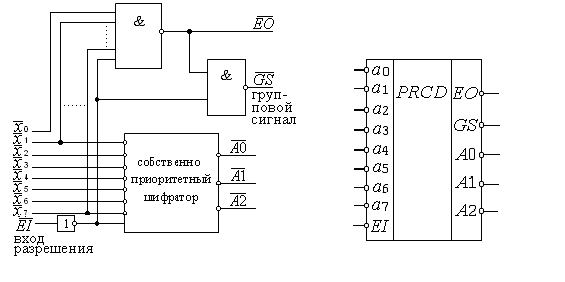

Если к выходу схемы выделения старшей единицы подключить шифратор, то в сумме получится функциональный узел приоритетного шифратора (priority encoder), формирующий в двоичном коде номер самой старшей единицы из всех, присутствующих во входном слове.

С выходами рассмотренной схемы хорошо стыкуются входы шифратора, двойственного по отношению к рассмотренному ранее (т. е. на элементах И-НЕ): инверсным выходам одной схемы (блока выделения старшей единицы) будут соответствовать инверсные входы другой. Весь приоритетный шифратор будет построен на технологичных элементах без лишних инверторов.

Если во входном слове присутствует только одна единица, то приоритетный шифратор будет выполнять функцию обычного шифратора. Поэтому микросхемы обычных шифраторов не встречаются почти ни в одной серии, а приоритетные шифраторы – в составе многих серий. Упрощенная структура микросхемы 155ИВ1 и ее обозначение представлены на рис. 10.4.

Работу

приоритетного шифратора 155ИВ1 отражает

таблица истинности (табл. 10.2). Здесь Х –

безразличное состояние входа (0 или 1).

Из таблицы следует, что вход EI

позволяет сделать все входы неактивными

(а0-а7)

при

![]() = 1, т. е. напряжение высокого уровня на

этом входе – это напряжение запрета.

При этом и на всех выходах присутствует

высокий (неактивный) уровень.

= 1, т. е. напряжение высокого уровня на

этом входе – это напряжение запрета.

При этом и на всех выходах присутствует

высокий (неактивный) уровень.

На выходе GS низкий уровень, если хотя бы на одном входе уровень низкий,

![]()

Рис. 10.4. Упрощенная структура приоритетного шифратора и его обозначение

т. е. хотя бы один из входов активный (кроме а0, при этом сигналы А0, А1, А2 и EO высокие). На выходе EO будет низкий уровень, если на всех входах высокие уровни (отсутствуют активные сигналы).

Таким образом, выходные сигналы EO и GS характеризуют состояния входов шифратора и используются для каскадирования шифраторов или управления другими логическими схемами:

![]() –

выходной

сигнал, низкий уровень которого

свидетельствует об отсутствии хотя бы

одного активного сигнала на входах;

–

выходной

сигнал, низкий уровень которого

свидетельствует об отсутствии хотя бы

одного активного сигнала на входах;

![]() –выходной

сигнал, низкий уровень которого

свидетельствует о наличии хотя бы одного

активного сигнала на входах.

–выходной

сигнал, низкий уровень которого

свидетельствует о наличии хотя бы одного

активного сигнала на входах.

Каскадирование применяют для увеличения числа входов шифратора, объединяя несколько микросхем шифраторов в один логический узел.

Таблица10.2

|

ВХОД |

ВЫХОД | ||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

1 |

X |

X |

X |

X |

X |

X |

X |

X |

1 |

1 |

1 |

1 |

1 |

|

0 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

0 |

|

0 |

X |

X |

X |

X |

X |

X |

X |

0 |

0 |

0 |

0 |

0 |

1 |

|

0 |

X |

X |

X |

X |

X |

X |

0 |

1 |

0 |

1 |

0 |

0 |

1 |

|

0 |

X |

X |

X |

X |

X |

0 |

1 |

1 |

0 |

0 |

1 |

0 |

1 |

|

0 |

X |

X |

X |

X |

0 |

1 |

1 |

1 |

0 |

1 |

1 |

0 |

1 |

|

0 |

X |

X |

X |

0 |

1 |

1 |

1 |

1 |

0 |

0 |

0 |

1 |

1 |

|

0 |

X |

X |

0 |

1 |

1 |

1 |

1 |

1 |

0 |

1 |

0 |

1 |

1 |

|

0 |

X |

0 |

1 |

1 |

1 |

1 |

1 |

1 |

0 |

0 |

1 |

1 |

1 |

|

0 |

0 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

0 |

1 |

1 |

1 |

1 |

В случае построения шифратора на 16 входов можно объединить два приоритетных шифратора (рис. 10.5). Разряды 8–15 старшего байта входного слова поступают на первый (нижний по схеме) шифратор, а разряды 0–7 младшего байта подаются на второй шифратор (верхний). Информационные выходы обоих шифраторов объединяются с помощью логических элементов. Значение старшего разряда А′3 обеспечивается непосредственно сигналом GS шифратора старшего байта.

Для десятичной клавиатуры или декадных переключателей схема может быть реализована с использованием одного восьмивходового шифратора и нескольких дополнительных логических элементов (рис. 10.6).

Рис. 10.5. Шифратор 16:4 Рис. 10.6. Шифратор 10:4

Промышленностью выпускаются микросхемы шифраторов К155ИВ1, 555ИВ1, 555ИВ3 и др.