- •Схемотехника эвм

- •Часть 2

- •Содержание

- •8. Регистры

- •8.1. Назначение и классификация регистров

- •8.2. Регистры памяти

- •8.3. Буферы данных

- •8.4. Регистры сдвига

- •Кольцевые счетчики

- •9. Мультиплексоры и демультиплексоры

- •9.1. Общие сведения

- •9.2. Мультиплексоры

- •9.3. Демультиплексоры

- •10. Шифраторы и дешифраторы

- •10.1. Шифраторы

- •10.2. Дешифраторы

- •11. Арифметические устройства

- •11.1. Сумматоры

- •Четвертьсумматор

- •Полусумматор

- •Полный одноразрядный двоичный сумматор

- •Сумматоры с последовательным переносом

- •11.2. Инкрементор

- •11.3. Вычитатели (субтракторы)

- •11.4. Компараторы

- •Основные характеристики компараторов

- •Компараторы аналоговых сигналов

- •Компараторы цифровых сигналов

- •Компаратор на базе сумматора

- •11.5. Арифметико-логические устройства

- •12. Импульсные устройства на имс

- •12.1. Формирователи импульсов

- •12.2. Схемы нормализации импульсов

- •12.3. Схемы укорачивания импульсов

- •12.4. Схемы задержки импульса

- •12.5. Одновибраторы

- •12.6. Генераторы тактовой частоты

- •13. Запоминающие устройства

- •13.1. Общие характеристики устройств

- •13.2. Запоминающие элементы постоянных зу

- •13.3. Оперативные запоминающие устройства

- •13.3.1. Динамические зу

- •13.3.2. Статические зу

- •14. Аналого-цифровые и цифро-аналоговые преобразователи

- •14.1. Общие сведения

- •14.2. Цифро-аналоговые преобразователи

- •14.3. Аналого-цифровые преобразователи

- •14.3.1. Характеристики и параметры ацп

- •14.3.2. Ацп последовательного счета

- •14.3.3. Параллельный ацп

- •14.3.4. Сигма-дельта ацп

- •Заключение

- •Библиографический список

- •Приложение 1 Перечень стандартов

- •Основные стандарты ескд

- •Система технологической документации

- •Стандарты системы информационно-библиографической документации

- •Система стандартов по безопасности труда

- •Разработка и постановка продукции на производство

- •Система стандартов программной документации

- •Основополагающие стандарты гсп

- •Приложение 2

- •Цифровых устройств

Компаратор на базе сумматора

Построить компаратор можно на основе сумматора, выполнив в нем операцию вычитания А – В и проанализировав результат. Для этого на сумматор нужно число В подать в инверсном коде, число А в прямом, а на вход переноса cr сумматора подать единицу. Тогда выходной перенос CR будет равен нулю лишь в том случае, когда число А строго меньше В. Равенство суммы нулю будет признаком того, что А = В. Единица переноса при ненулевой сумме говорит о том, что А строго больше В.

Примеры:

А > В А = В А < В

Схема, реализующая описанный алгоритм, представлена на рис. 11.17.

Рис. 11.17. Схема компаратора на базе сумматора

Возможны и другие схемы построения компараторов, являющихся наиболее оптимальными в конкретных технических приложениях.

11.5. Арифметико-логические устройства

Арифметико-логическим

устройством (АЛУ) называется функциональный

узел ЭВМ, предназначенный для выполнения

арифметических и логических операций

по обработке двоичной информации.

П о

сравнению с приборами, работающими по

жесткой, наперед заданной программе,

арифметико-логические устройства

представляют собой устройства более

высокого класса. В микропроцессорной

технике АЛУ являются базовыми элементами.

Они используются в сочетании с регистрами

сдвига, ОЗУ и другими устройствами. АЛУ

дороже простых микросхем, но благодаря

универсальным свойствам применение их

в аппаратуре во многих случаях оказывается

оправданным.

о

сравнению с приборами, работающими по

жесткой, наперед заданной программе,

арифметико-логические устройства

представляют собой устройства более

высокого класса. В микропроцессорной

технике АЛУ являются базовыми элементами.

Они используются в сочетании с регистрами

сдвига, ОЗУ и другими устройствами. АЛУ

дороже простых микросхем, но благодаря

универсальным свойствам применение их

в аппаратуре во многих случаях оказывается

оправданным.

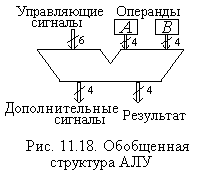

Основой АЛУ служит сумматор, схема которого дополнена логикой, расширяющей функциональные возможности и обеспечивающей перестройку АЛУ с одной операции на другую, набором регистров и управляющим устройством. Упрощенно схема АЛУ представлена на рис. 11.18. АЛУ имеет входы операндов А и В, входы выбора операций (управляющие сигналы Si и М), вход переноса С. Выходами АЛУ являются результат операции над операндами Fi, сигнал переноса С4, дополнительные выходы образования и распространения ускоренного переноса.

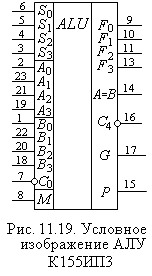

Микросхемы

АЛУ, принадлежащие к разным видам логик

(ТТЛ – 155ИП3; КМОП – 564ИП3), функционально

во многом совпадают, в том числе и по

разводке выводов. На рис. 11.19 приведено

условное изображение микросхемы АЛУ

К155ИП3. Эта микросхема выполняет действия

с четырехразрядными двоичными с ловами:

А = А3А2А1А0

и В = В3В2В1В0.

Вид операций задается пятиразрядным

кодом установки значений на входах М и

S3S2S1S0.

Всего это АЛУ способно выполнить 32

операции (25

= 32). К ним относятся: 16 логических операций

(И, И-НЕ, ИЛИ, ИЛИ-НЕ, исключающее ИЛИ и

др.) и 16 арифметических или

арифметико-логических операций (сложение,

вычитание, удвоение, сравнение и ряд

других). Операции проводятся с ускоренным

переносом. Микросхема имеет вход приема

сигнала переноса С0

(активный сигнал низкого уровня).

ловами:

А = А3А2А1А0

и В = В3В2В1В0.

Вид операций задается пятиразрядным

кодом установки значений на входах М и

S3S2S1S0.

Всего это АЛУ способно выполнить 32

операции (25

= 32). К ним относятся: 16 логических операций

(И, И-НЕ, ИЛИ, ИЛИ-НЕ, исключающее ИЛИ и

др.) и 16 арифметических или

арифметико-логических операций (сложение,

вычитание, удвоение, сравнение и ряд

других). Операции проводятся с ускоренным

переносом. Микросхема имеет вход приема

сигнала переноса С0

(активный сигнал низкого уровня).

На выходах F0, F1, F2, F3 формируются результаты арифметико-логических преобразований. На выходе С4 образуется сигнал старшего (пятого) разряда при выполнении арифметических операций (сигнал переноса). Дополни- тельные выходы – образование ускоренного переноса G и распространение ускоренного переноса Р – используются только при организации многоразрядных АЛУ в сочетании с микросхемами ускоренного переноса К155ИП4.

Слова А и В, подлежащие обработке, могут быть представлены как в положительной, так и в отрицательной логике. В [9, 15] приведены таблицы функциональной зависимости выходов микросхемы К155ИП3 от состояния входов. Таблицы истинности для каждого варианта логики различны.

Старший разряд кода выбора операции (М-вход) определяет характер действий, выполняемых АЛУ. Если М = 1 – АЛУ выполняет логические операции. Если М = 0 – выполняются арифметические и арифметико-логические операции.

Рассмотрим более подробно некоторые операции в положительной логике. При М = 1 выполняются логические функции. Если на входах S3S2S1S0 код 0000, то в этом случае выполняется логическая функция инвертирования операнда А – данные со входов А передаются на выходы F с инверсией.

Код 0001 – (А V В) с инверсией – поразрядная операция ИЛИ с инверсией над операндами А и В.

Код 0010 – операция И инвертированного операнда А и операнда В.

Код 0011 – нет операции – логический ноль.

Код 0100 – (А Х В) с инверсией – операция И с инверсией.

Код 0101 – инверсия операнда В.

Код 0110 – операция Исключающее ИЛИ.

Код 0111 – операция И над операндами А и инверсией В.

При М = 0 выполняются арифметические операции. Результаты арифметических операций выражены в дополнительном коде. Числа в дополнительном и обратном коде связаны соотношением Nдоп = Nобр + 1.

Код 0000 – передача на выход операнда А.

Код 0001 – А + В – операция суммирования без учета переноса.

Код

0010 – (А

+

![]() )

– операция суммирования операндаА

с инверсией операнда В

без учета переноса.

)

– операция суммирования операндаА

с инверсией операнда В

без учета переноса.

Код 0011 – минус 1 (результат арифметической операции представлен в обратном коде).

Код

0100 – (А

+ А![]() )

– операция суммирования операнда А

с конъюнкцией операнда А

и инвертированного В.

)

– операция суммирования операнда А

с конъюнкцией операнда А

и инвертированного В.

Например,

последнему рассмотренному коду МS3S2S1S0

= LLHLL

(00100) для положительной логики отвечает

операция А

+ А![]() ,

где А

,

где А![]() – логическое умножение двух слов. Так,

если А

= 0010, В

= 1101, то А

– логическое умножение двух слов. Так,

если А

= 0010, В

= 1101, то А![]() = 0010 и, следовательно,

0010 + 0010 = 0100.

= 0010 и, следовательно,

0010 + 0010 = 0100.

Режим компаратора обеспечивается при М = L и S3S2S1S0 = LHHL (0110). Когда числа А и В равны, на выходе А = В (вывод 14) формируется сигнал высокого уровня. Если числа не равны, то сигнал на выходе С4 характеризует соотношение между числами (в положительной логике табл. 11.7).

Таблица 11.7

-

Состояние входов

Состояние выхода С4

С0

А и В

Н

А < B

1

L

A < B

1

H

A > B

0

L

A > B

0

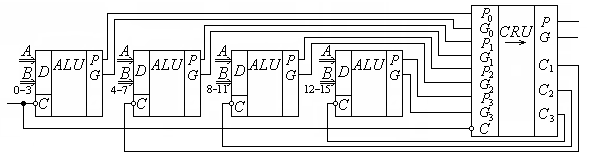

При операциях над словами большой размерности АЛУ соединяются друг с другом с организацией последовательных или параллельных переносов. При последовательном переносе выход С4 предыдущей микросхемы соединяют с входом С0 последующей. При организации параллельного переноса микросхемы 155ИП3 объединяют в сочетании с блоком ускоренного переноса 155ИП4 по схеме, представленной на рис. 11.20.

Рис. 11.20. Увеличение разрядности АЛУ применением

блока ускоренного переноса К155ИП4

Выходы С1, С2 и С3 блока ускоренного переноса – сигналы образования и распространения переноса с учетом переносов соответствующих АЛУ. Если при выполнении арифметических операций к быстродействию не предъявляется высоких требований, то при каскадировании АЛУ схемы ускоренного переноса не применяют.