- •Схемотехника эвм

- •Часть 2

- •Содержание

- •8. Регистры

- •8.1. Назначение и классификация регистров

- •8.2. Регистры памяти

- •8.3. Буферы данных

- •8.4. Регистры сдвига

- •Кольцевые счетчики

- •9. Мультиплексоры и демультиплексоры

- •9.1. Общие сведения

- •9.2. Мультиплексоры

- •9.3. Демультиплексоры

- •10. Шифраторы и дешифраторы

- •10.1. Шифраторы

- •10.2. Дешифраторы

- •11. Арифметические устройства

- •11.1. Сумматоры

- •Четвертьсумматор

- •Полусумматор

- •Полный одноразрядный двоичный сумматор

- •Сумматоры с последовательным переносом

- •11.2. Инкрементор

- •11.3. Вычитатели (субтракторы)

- •11.4. Компараторы

- •Основные характеристики компараторов

- •Компараторы аналоговых сигналов

- •Компараторы цифровых сигналов

- •Компаратор на базе сумматора

- •11.5. Арифметико-логические устройства

- •12. Импульсные устройства на имс

- •12.1. Формирователи импульсов

- •12.2. Схемы нормализации импульсов

- •12.3. Схемы укорачивания импульсов

- •12.4. Схемы задержки импульса

- •12.5. Одновибраторы

- •12.6. Генераторы тактовой частоты

- •13. Запоминающие устройства

- •13.1. Общие характеристики устройств

- •13.2. Запоминающие элементы постоянных зу

- •13.3. Оперативные запоминающие устройства

- •13.3.1. Динамические зу

- •13.3.2. Статические зу

- •14. Аналого-цифровые и цифро-аналоговые преобразователи

- •14.1. Общие сведения

- •14.2. Цифро-аналоговые преобразователи

- •14.3. Аналого-цифровые преобразователи

- •14.3.1. Характеристики и параметры ацп

- •14.3.2. Ацп последовательного счета

- •14.3.3. Параллельный ацп

- •14.3.4. Сигма-дельта ацп

- •Заключение

- •Библиографический список

- •Приложение 1 Перечень стандартов

- •Основные стандарты ескд

- •Система технологической документации

- •Стандарты системы информационно-библиографической документации

- •Система стандартов по безопасности труда

- •Разработка и постановка продукции на производство

- •Система стандартов программной документации

- •Основополагающие стандарты гсп

- •Приложение 2

- •Цифровых устройств

8.4. Регистры сдвига

В рассмотренных регистрах не предусмотрена возможность сдвига информации, поэтому ввод и вывод “слова” в них осуществляется только в параллельном коде. Необходимо отметить также, что при выводе информации состояние триггеров не меняется. Следовательно, считывание слова из регистра может производиться многократно без разрушения информации.

Чтобы иметь возможность осуществлять сдвиг информации, применяют сдвигающие регистры. Схема сдвигающего регистра на D-триггерах приведена на рис. 8.10.

а б

Рис. 8.10. Функциональная схема (а) и условное обозначение

(б) сдвигового регистра

Регистр состоит из цепочки триггеров. Пусть ТТ0 – триггер младшего разряда, ТТ3 – триггер старшего. D-вход каждого триггера (кроме ТТ0) подключен к выходу соседнего (младшего) триггера. Когда на все объединенные С-входы триггеров поступает активный отрицательный фронт (спад) сигнала “сдвиг”, выход каждого триггера принимает состояние своего младшего соседа. Таким образом, информация, содержащаяся в регистре, сдвигается на один разряд в сторону старших триггеров, вправо. Выход D триггера ТТ0 принимает при этом состояние последовательного входа DS. Регистр загружается данными, последовательно поступающими по этому входу. Считывать данные, хранимые в RG, можно как в последовательном коде с выхода последнего разряда, так и в параллельном, сразу со всех разрядов.

Сдвиг может производиться как влево, так и вправо.

Далее рассмотрим кольцевые счетчики, которые строятся на базе сдвигающих регистров, а затем вернемся к конкретным сдвигающим регистрам.

Кольцевые счетчики

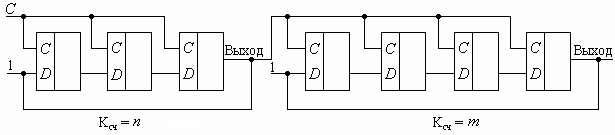

В качестве счетчика может быть использован сдвигающий регистр, замкнутый в кольцо цепью обратной связи (рис. 8.11).

Рис . 8.11. Схема кольцевого счетчика на базе сдвигающего регистра

В этом регистре продвигается одна единица, которая при подаче очередного продвигающего импульса передается в следующую по порядку ячейку. Дойдя до конца регистра, единица записывается в первую ячейку и счет повторяется. Входной импульс с (тактирующий) в этом счетчике выполняет функции продвигающего. Число поступивших на вход импульсов фиксируется позицией единицы в регистре в данный момент времени. В таких счетчиках отсутствует последовательная передача сигнала переноса от ячейки к ячейке и поэтому задержка выходного импульса относительно входного оказывается незначительной. Количество двоичных ячеек должно быть равно коэффициенту счета (деления), при больших коэффициентах такой счетчик неэкономичен. Для существенного увеличения коэффициента счета при малых аппаратурных затратах счетчики соединяют последовательно (рис. 8.12). Если у одного счетчика коэффициент счета равен n, а у другого – m, то общий коэффициент счета будет равен произведению

N = n * m.

Рис. 8.12. Последовательное соединение счетчиков

Продолжим далее рассмотрение сдвиговых регистров. В качестве первого примера сдвигового регистра рассмотрим микросхему К155ИР1 – четырехразрядный регистр сдвига с последовательным или параллельным вводом и параллельным выводом информации. Он может быть использован в качестве буферной памяти, элемента задержки на несколько тактов, преобразователя последовательного кода в параллельный и наоборот, делителя частоты, кольцевого распределителя импульсов, элемента арифметических устройств и т. п. Условное изображение приводится на рис. 8.13.

Рис. 8.13. Реверсивный сдвиговый регистр

С1, С2 – тактовые входы; V2 – выбор режима; V1 – для ввода информации в последовательном коде; D1-D4 для записи информации в параллельном коде; Q1-Q4 – четыре разряда выхода. Входы С1 и С2 для синхронизации от одного или двух генераторов. Срабатывание триггера по перепаду 1,0 импульсов на одном из входов С.

Если на входе сигнал V2 = 0 – ввод последовательным кодом через V1 и сдвиг вправо, а тактовые импульсы подаются на С1. Сдвиг вправо при каждом перепаде 1,0 тактовых импульсов. Через 4 тактовых импульса информацию можно считать в параллельном коде.

Ввод параллельным кодом производится при V2 = 1 по спаду импульса на входе С2. Входы V1 и С1 при этом блокированы и роли не играют.

В этом же режиме V2 и С2 производится преобразование последовательного кода в параллельный со сдвигом влево. В этом случае информация идет от 4-го триггера к 3-му, от 3-го ко 2-му и т. д. Для этого выходы Q4, Q3, Q2 соединяют со входами D3, D2, D1 соответственно. Информация в последовательном коде поступает через вход D4 при каждом перепаде С2 с 0 на 1. Таблица состояний регистра 155ИР1 приведена ниже.

|

Таблица 8.1

| |||

|

Состояние входов |

Режим | ||

|

V2 |

С1 |

С2 | |

|

1 |

× |

|

Запись параллельным кодом, сдвиг влево |

|

0 |

|

× |

Запись последов. кодом, сдвиг вправо |

Во избежание сбоев смена состояний V2 должна происходить только при С1 = С2 = 0. Последовательным соединением n микросхем можно получить 4-n разрядный регистр с преобразованием параллельного кода в последовательный и наоборот.

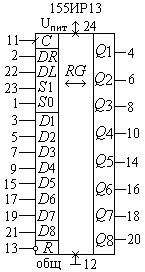

Микросхема К155ИР13 – универсальный 8-ми разрядный регистр сдвига с большими функциональными возможностями – представлена на рис. 8.14.

Регистр может работать в следующих режимах (табл. 8.2):

– последовательный ввод информации со сдвигом вправо;

последовательный ввод со сдвигом влево;

параллельный ввод;

хранение;

установка нулей (сброс).

Рис. 8.14. Универсальный восьмиразрядный сдвиговый регистр

Информационные входы последовательного ввода: DR – при сдвиге вправо; DL – при сдвиге влево; D1¸D8 – параллельный ввод; С – тактовый вход; S1, S0 – для выбора режима; R – для установки триггера в 0; Q1¸Q8 – выходы.

|

Таблица 8.2

| ||||||||

|

Входы |

Выходы |

Режим | ||||||

|

R |

C |

S1 |

S0 |

DR |

DL |

Di |

Q1,Q2…Q8 | |

|

1 |

|

1 |

1 |

1 |

× |

Din |

D1n…D8n |

Параллельный ввод |

|

1 |

0 |

0 |

× |

× |

× |

Q1n…Q8n |

Хранение | |

|

1 |

1 |

0 |

× |

0 |

× |

Q2n…Q8n, 0 |

Сдвиг влево | |

|

1 |

1 |

0 |

× |

1 |

× |

Q2n…Q8n,1 | ||

|

1 |

0 |

1 |

0 |

× |

× |

0, Q1n…Q7n |

Сдвиг вправо | |

|

1 |

0 |

1 |

1 |

× |

× |

1, Q1n…Q7n | ||

|

0 |

× |

× |

× |

× |

× |

× |

0…0 |

Сброс |

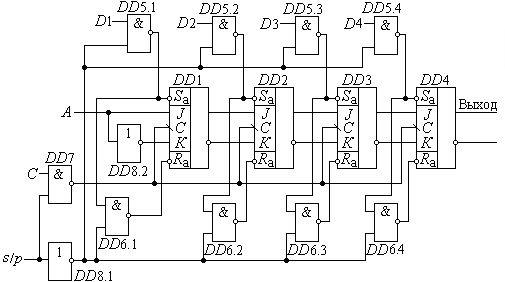

Далее приведена схема регистра сдвига с параллельным и последовательным вводом информации и последовательным ее выводом (рис. 8.15).

Режим работы регистра определяется сигналом на входе s/p (последовательно–параллельно). Допустим, сигнал на этом входе имеет уровень 1. На выходе инвертора DD8 будет 0, который закроет логические элементы DD5.1–DD5.4 и DD6.1–DD6.4 и создаст тем самым на асинхронных входах триггеров Sa и Ra уровни 1, разрешающие синхронное действие. Входы D1–D4 для параллельного ввода информации при этом заблокированы. Тактовые импульсы на входе обеспечат синхронный ввод информации в последовательном коде (со входа А) и также сдвиг ее вправо. За счет инверсии тактовых импульсов элементом DD7 тактирование происходит по фронту 0,1 (а не по срезу).

Рис. 8.15. Схема реверсивного регистра

Когда на входе s/p 0 элемент DD7 заперт, тактирование триггеров прекращается. Сигнал на общих входах элементов DD5.1–DD5.4 и DD6.1–DD6.4 становится 1, вследствие чего каждый из этих элементов для сигналов на шинах параллельного ввода D1–D4 служит инвертором. Под воздействием входных сигналов параллельного ввода выходы соответствующих триггеров примут те же состояния – Qi = Di.

С появлением на входе s/p 1 (разрешение тактирования) информация, введенная в параллельном коде, с каждым тактовым импульсом будет сдвигаться на один разряд и выдаваться в последовательной форме, т. е. произойдет преобразование информации параллельного вида в последовательный.

Если в такой схеме сделать выводы с выхода каждого JK-триггера, то можно будет вводить и выводить информацию в параллельном и в последовательном коде и преобразовывать из последовательного кода в параллельный, и наоборот.