- •Схемотехника эвм

- •Часть 2

- •Содержание

- •8. Регистры

- •8.1. Назначение и классификация регистров

- •8.2. Регистры памяти

- •8.3. Буферы данных

- •8.4. Регистры сдвига

- •Кольцевые счетчики

- •9. Мультиплексоры и демультиплексоры

- •9.1. Общие сведения

- •9.2. Мультиплексоры

- •9.3. Демультиплексоры

- •10. Шифраторы и дешифраторы

- •10.1. Шифраторы

- •10.2. Дешифраторы

- •11. Арифметические устройства

- •11.1. Сумматоры

- •Четвертьсумматор

- •Полусумматор

- •Полный одноразрядный двоичный сумматор

- •Сумматоры с последовательным переносом

- •11.2. Инкрементор

- •11.3. Вычитатели (субтракторы)

- •11.4. Компараторы

- •Основные характеристики компараторов

- •Компараторы аналоговых сигналов

- •Компараторы цифровых сигналов

- •Компаратор на базе сумматора

- •11.5. Арифметико-логические устройства

- •12. Импульсные устройства на имс

- •12.1. Формирователи импульсов

- •12.2. Схемы нормализации импульсов

- •12.3. Схемы укорачивания импульсов

- •12.4. Схемы задержки импульса

- •12.5. Одновибраторы

- •12.6. Генераторы тактовой частоты

- •13. Запоминающие устройства

- •13.1. Общие характеристики устройств

- •13.2. Запоминающие элементы постоянных зу

- •13.3. Оперативные запоминающие устройства

- •13.3.1. Динамические зу

- •13.3.2. Статические зу

- •14. Аналого-цифровые и цифро-аналоговые преобразователи

- •14.1. Общие сведения

- •14.2. Цифро-аналоговые преобразователи

- •14.3. Аналого-цифровые преобразователи

- •14.3.1. Характеристики и параметры ацп

- •14.3.2. Ацп последовательного счета

- •14.3.3. Параллельный ацп

- •14.3.4. Сигма-дельта ацп

- •Заключение

- •Библиографический список

- •Приложение 1 Перечень стандартов

- •Основные стандарты ескд

- •Система технологической документации

- •Стандарты системы информационно-библиографической документации

- •Система стандартов по безопасности труда

- •Разработка и постановка продукции на производство

- •Система стандартов программной документации

- •Основополагающие стандарты гсп

- •Приложение 2

- •Цифровых устройств

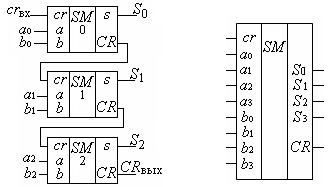

Сумматоры с последовательным переносом

Простейший способ построения n-разрядного сумматора – это последовательное включение n одноразрядных сумматоров, складывающих одноименные разряды слагаемых (рис. 11.5).

На схеме выход переноса CR каждого разряда подключен к входу переноса cr соседнего старшего разряда.

а б

Рис. 11.5. Структурная схема (а) и условное обозначение сумматора (б)

Входной перенос всего n-разрядного сумматора подается на вход cr самого младшего разряда. Выходной перенос CR самого старшего разряда является выхо-дом переноса всего n-разрядного сумматора. Таким образом, задача построения сумматора с последовательным переносом сводится к построению схемы одноразрядного сумматора. Это наиболее простые схемы сумматоров.

Между тем, в сумматорах с последовательным переносом задержка TcrCR суммируется по всем разрядам, вследствие чего они обладают сравнительно низким быстродействием. Именно поэтому сумматоры с последовательным переносом выпускаются, обычно, разрядностью не более четырех.

Проблему быстродействия решают использованием схем сквозного и параллельного переноса, подобно тому, как это делается в счётчиках (смотри п.п. 7.2). В этом случае входной перенос каждого разряда вырабатывается независимо от переноса соседнего младшего разряда. Он формируется как функция только слагаемых и входного переноса crвх всего n-разрядного сумматора.

Однако диапазон разрядности, в пределах которого сумматор с параллельным переносом эффективен, невелик. С увеличением разрядности быстро растет число входов элементов И. Поэтому разрядность параллельного сумматора редко превышает 8. Четырехразрядный ИМ6 имеет вдвое меньшую задержку TcrCR по сравнению с ИМ3 тоже четырехразрядным, но с последовательным переносом.

Наиболее распространёнными микросхемами сумматоров являются К155ИМ1… К155ИМ3, К555ИМ6 К555ИМ7 и др.

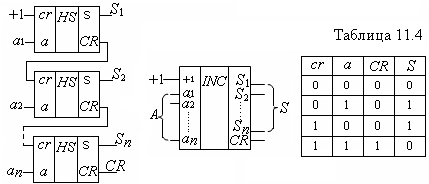

11.2. Инкрементор

Полусумматоры, соединенные по тракту переноса цепочкой, образуют схему инкрементора (рис. 11.6). При уровне 0 на входе +1 инкрементор пропускает поданное на входы аi n-разрядное число А без изменений. При уровне 1 на входе +1 к А добавляется 1, т. е. А + 1 = S.

а б в

Рис. 11.6. Структурная схема (а), условное обозначение (б)

и таблица истинности для одного разряда инкрементора (в)

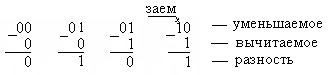

11.3. Вычитатели (субтракторы)

Операция вычитания обратна операции сложения. Вычитание одного двоичного числа из другого в двоичной системе подобно вычитанию в десятичной системе:

Последний столбец характеризуется вычитанием с займом: для вычитания единицы из нуля из соседнего старшего разряда занимается единица. Эта занимаемая единица старшего разряда равна двум единицам соседнего младшего разряда.

Заем производится для тех разрядов, где вычитаемое больше уменьшаемого. Пример:

Стрелками здесь показан заем из соседнего разряда.

Для вычитания двух чисел могут быть собраны полувычитатели и вычитатели (полусубтракторы и субтракторы). Полувычитатель по принципу действия имеет два входа ─ для уменьшаемого и для вычитаемого и поэтому может быть использован только в высшем разряде многоразрядного вычитателя. В остальных разрядах должны быть полные вычитатели, которые имеют третий вход для приема сигнала займа. В виде самостоятельных изделий вычитатели не производятся. При необходимости вычитатель можно спроектировать подобно сумматору. Пример логической структуры полусубтрактора и его таблица истинности представлены на рис. 11.7.

Таблица

11.5

Таблица

11.5

|

Умень-шаемое |

Вычи-таемое |

Раз-ность |

Заем |

|

0 |

0 |

0 |

0 |

|

0 |

1 |

1 |

1 |

|

1 |

0 |

1 |

0 |

|

1 |

1 |

0 |

0 |

Рис. 11.7. Структура полусубтрактора и его таблица истинности