- •Схемотехника эвм

- •Часть 2

- •Содержание

- •8. Регистры

- •8.1. Назначение и классификация регистров

- •8.2. Регистры памяти

- •8.3. Буферы данных

- •8.4. Регистры сдвига

- •Кольцевые счетчики

- •9. Мультиплексоры и демультиплексоры

- •9.1. Общие сведения

- •9.2. Мультиплексоры

- •9.3. Демультиплексоры

- •10. Шифраторы и дешифраторы

- •10.1. Шифраторы

- •10.2. Дешифраторы

- •11. Арифметические устройства

- •11.1. Сумматоры

- •Четвертьсумматор

- •Полусумматор

- •Полный одноразрядный двоичный сумматор

- •Сумматоры с последовательным переносом

- •11.2. Инкрементор

- •11.3. Вычитатели (субтракторы)

- •11.4. Компараторы

- •Основные характеристики компараторов

- •Компараторы аналоговых сигналов

- •Компараторы цифровых сигналов

- •Компаратор на базе сумматора

- •11.5. Арифметико-логические устройства

- •12. Импульсные устройства на имс

- •12.1. Формирователи импульсов

- •12.2. Схемы нормализации импульсов

- •12.3. Схемы укорачивания импульсов

- •12.4. Схемы задержки импульса

- •12.5. Одновибраторы

- •12.6. Генераторы тактовой частоты

- •13. Запоминающие устройства

- •13.1. Общие характеристики устройств

- •13.2. Запоминающие элементы постоянных зу

- •13.3. Оперативные запоминающие устройства

- •13.3.1. Динамические зу

- •13.3.2. Статические зу

- •14. Аналого-цифровые и цифро-аналоговые преобразователи

- •14.1. Общие сведения

- •14.2. Цифро-аналоговые преобразователи

- •14.3. Аналого-цифровые преобразователи

- •14.3.1. Характеристики и параметры ацп

- •14.3.2. Ацп последовательного счета

- •14.3.3. Параллельный ацп

- •14.3.4. Сигма-дельта ацп

- •Заключение

- •Библиографический список

- •Приложение 1 Перечень стандартов

- •Основные стандарты ескд

- •Система технологической документации

- •Стандарты системы информационно-библиографической документации

- •Система стандартов по безопасности труда

- •Разработка и постановка продукции на производство

- •Система стандартов программной документации

- •Основополагающие стандарты гсп

- •Приложение 2

- •Цифровых устройств

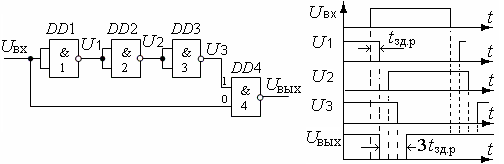

12.4. Схемы задержки импульса

Схемы задержки цифровых сигналов требуются для временного согласования распространения сигналов по различным путям цифрового устройства. Временные рассогласования прохождения сигналами заданных путей могут привести к критическим временным состязаниям, нарушающим работу устройств. На время прохождения влияют параметры элементов, через которые передаются цифровые сигналы. Изменяя эти параметры, можно изменять время распространения сигналов. Для изменения времени задержки используют электромагнитные линии задержки, цепочки логических элементов, RC-цепочки. Используя такие элементы, можно получить сужение, расширение сигналов, сужение со сдвигом относительно фронта входного импульса и т. д.

Д ля

изменения длительности и смещения

импульса относительно фронта часто

используют естественную инерционность

логических элементов. Одна из схем,

использующих инерционные свойства

логических элементов, представлена на

рис. 12.8. (Подобная схема приводилась на

рис.3.25 в п.п. 3.2.3)

ля

изменения длительности и смещения

импульса относительно фронта часто

используют естественную инерционность

логических элементов. Одна из схем,

использующих инерционные свойства

логических элементов, представлена на

рис. 12.8. (Подобная схема приводилась на

рис.3.25 в п.п. 3.2.3)

а б

Рис. 12.8. Формирователь короткого импульса с задержкой относительно переднего фронта (а) и временная диаграмма (б)

Каждый логический элемент создает временную задержку, поэтому при появлении входного сигнала изменение уровня выходного сигнала после первого логического элемента U1 происходит через время tзд.р. Аналогично, через интервал временной задержки изменяются выходные сигналы других инверторов (U2,U3). Изменение состояния четвертого элемента нужно анализировать с учетом того, что здесь входы раздельные. До поступления входного сигнала на верхнем входе логического элемента DD4 была логическая 1, а на нижнем входе – логический 0. Поэтому в установившемся состоянии на выходе схемы был высокий потенциал (логическая 1).

После появления входного сигнала на нижнем входе элемента DD4 устанавливается логическая единица, на верхнем также пока еще действует 1. Поэтому на выходе схемы через время tзд.р установится логический 0. Пройдя через три логических элемента, входной сигнал изменит значение U3 c 1 на 0 (это верхний вход элемента DD4). Выходное напряжение схемы с учетом tзд.р в элементе DD4 снова станет равно 1. Следовательно, схема формирует из переднего фронта входного сигнала короткий импульс длительностью 3tзд.р со сдвигом относительно переднего фронта на tзд.р. Задний фронт входного сигнала изменения состояния схемы на выходе не вызывает, поскольку к моменту появления 1 на верхнем входе элемента DD4 на нижнем уже существует 0. Поэтому 1 на выходе сохраняется до появления следующего входного импульса. Происходящие процессы без учета длительности фронтов импульсов представлены на временной диаграмме (рис. 12.8, б). Формируемый схемой сигнал имеет низкий уровень.

Если конъюнктор DD4 в схеме (рис. 12.8, а) заменить на дизъюнктор, а число инверторов сделать четным, то схема будет расширять входные импульсы на временной интервал, равный ntзд.р, где n – число инверторов в цепи задержки. Схема расширителя импульсов и временная диаграмма его работы представлены на рис. 12.9.

а б

Рис. 12.9. Схема расширителя импульсов (а) и временная диаграмма (б)

Из временной диаграммы видно, что длительность выходного импульса больше длительности входного на 4tзд.р.

Рассмотрены кратко лишь несколько схем последовательных формирователей импульсов. Дополнительные сведения можно найти в [1, 9,15].