- •Схемотехника эвм

- •Часть 2

- •Содержание

- •8. Регистры

- •8.1. Назначение и классификация регистров

- •8.2. Регистры памяти

- •8.3. Буферы данных

- •8.4. Регистры сдвига

- •Кольцевые счетчики

- •9. Мультиплексоры и демультиплексоры

- •9.1. Общие сведения

- •9.2. Мультиплексоры

- •9.3. Демультиплексоры

- •10. Шифраторы и дешифраторы

- •10.1. Шифраторы

- •10.2. Дешифраторы

- •11. Арифметические устройства

- •11.1. Сумматоры

- •Четвертьсумматор

- •Полусумматор

- •Полный одноразрядный двоичный сумматор

- •Сумматоры с последовательным переносом

- •11.2. Инкрементор

- •11.3. Вычитатели (субтракторы)

- •11.4. Компараторы

- •Основные характеристики компараторов

- •Компараторы аналоговых сигналов

- •Компараторы цифровых сигналов

- •Компаратор на базе сумматора

- •11.5. Арифметико-логические устройства

- •12. Импульсные устройства на имс

- •12.1. Формирователи импульсов

- •12.2. Схемы нормализации импульсов

- •12.3. Схемы укорачивания импульсов

- •12.4. Схемы задержки импульса

- •12.5. Одновибраторы

- •12.6. Генераторы тактовой частоты

- •13. Запоминающие устройства

- •13.1. Общие характеристики устройств

- •13.2. Запоминающие элементы постоянных зу

- •13.3. Оперативные запоминающие устройства

- •13.3.1. Динамические зу

- •13.3.2. Статические зу

- •14. Аналого-цифровые и цифро-аналоговые преобразователи

- •14.1. Общие сведения

- •14.2. Цифро-аналоговые преобразователи

- •14.3. Аналого-цифровые преобразователи

- •14.3.1. Характеристики и параметры ацп

- •14.3.2. Ацп последовательного счета

- •14.3.3. Параллельный ацп

- •14.3.4. Сигма-дельта ацп

- •Заключение

- •Библиографический список

- •Приложение 1 Перечень стандартов

- •Основные стандарты ескд

- •Система технологической документации

- •Стандарты системы информационно-библиографической документации

- •Система стандартов по безопасности труда

- •Разработка и постановка продукции на производство

- •Система стандартов программной документации

- •Основополагающие стандарты гсп

- •Приложение 2

- •Цифровых устройств

13.3.2. Статические зу

Основой статических ОЗУ (SRAM) является RS-триггер или регистры. Примерами статических ОЗУ являются микросхемы 133, 155, 531, 565 серий РУ1, РУ3, РУ5, РУ6 и другие. Статические ОЗУ в несколько раз дороже динамических и приблизительно во столько же раз меньше по информационной емкости. Главное применение микросхем оперативной памяти – это временное хранение цифровой информации, которая в любой момент времени может быть считана или изменена. Важную роль играет и время доступа (записи и чтения). В зависимости от того, в каком порядке может записываться или читаться информация, существуют две разновидности статических ОЗУ:

ОЗУ с параллельным или произвольным доступом (адресные);

ОЗУ с последовательным доступом (безадресные или стеки).

При параллельном или произвольном доступе (адресные ОЗУ) записывать информацию можно в любой адрес ЗУ и читать информацию из любого адреса в произвольном порядке. Для этого нужно сформировать код адреса ячейки, управляющие сигналы (выбор кристалла, разрешение записи/чтения), и после этого записать данные или считать. ЗУ подобного типа, реализованное на регистрах, рассмотрено ранее (см. рис. 8.5).

При последовательном доступе (безадресные ОЗУ или стеки) предполагается более простой порядок обмена. В этом случае не надо задавать код адреса ячейки, в которую должна записываться информация или откуда должна считываться. При последовательном доступе для записи информации нужно сформировать код данных и подать его в ЗУ совместно с сигналом разрешения записи. Для чтения информации нужно подать только сигнал разрешения чтения. Задание адреса в этих случаях формируется автоматически специальными счетчиками.

При последовательной записи данные в ЗУ образуют некоторую очередь. Считывание информации из очереди происходит слово за словом либо в порядке записи, либо в обратном. Прямой порядок считывания имеет место в буферах (стеках) FIFO – “первый пришел – первый вышел”. Устройство с такой структурой рассмотрено в главе 8 (рис. 8.7). Примером микросхемы с рассмотренной структурой является микросхема 531РУ10, в которой может храниться до 16 пятиразрядных слов.

Запоминающие устройства, в которых считывание информации производится в обратном порядке по отношению к записи – “последний пришел – первый вышел”, называют буферами (стеками) LIFO или “магазин”. Структура типа LIFO, как и структура FIFO, основана на применении регистров, поэтому она также рассмотрена в главе 8 настоящего учебного пособия (рис. 8.8).

Разновидностью оперативной памяти является память типа NV-SRAM, которая способна сохранять информацию при отключении питания. Это свойство обеспечивается добавлением к ОЗУ перепрограммируемого запоминающего устройства с электрическим стиранием, которое обеспечивает сохранение информации в ППЗУ при снижении питающего напряжения ниже некоторого уровня. После восстановления питания информация автоматически передается обратно в ОЗУ. Такая комбинация двух типов памяти обеспечивает улучшение скоростных характеристик ОЗУ.

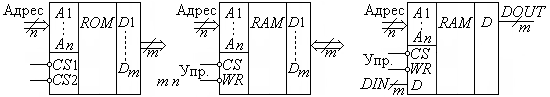

На рис. 13.5 показаны варианты условного графического обозначения микросхем памяти на функциональных схемах цифровых устройств.

а б в

Рис. 13.5. Условное графическое обозначение микросхем памяти: ПЗУ (а), ОЗУ с двунаправленной шиной данных (б), ОЗУ с раздельными шинами данных (в)

Следует отметить, что в настоящей главе не рассматриваются вопросы объединения ЗЭ в запоминающие массивы типа 2D, 3D, 2DM и т. д. Эти вопросы будут рассмотрены в курсе «организация ЭВМ и систем». Здесь рассмотрены лишь некоторые ЗЭ наиболее распространенных микросхем памяти. Дополнительные сведения и описание различных вариантов применения можно найти в [3, 4, 11, 15].