- •Схемотехника эвм

- •Часть 2

- •Содержание

- •8. Регистры

- •8.1. Назначение и классификация регистров

- •8.2. Регистры памяти

- •8.3. Буферы данных

- •8.4. Регистры сдвига

- •Кольцевые счетчики

- •9. Мультиплексоры и демультиплексоры

- •9.1. Общие сведения

- •9.2. Мультиплексоры

- •9.3. Демультиплексоры

- •10. Шифраторы и дешифраторы

- •10.1. Шифраторы

- •10.2. Дешифраторы

- •11. Арифметические устройства

- •11.1. Сумматоры

- •Четвертьсумматор

- •Полусумматор

- •Полный одноразрядный двоичный сумматор

- •Сумматоры с последовательным переносом

- •11.2. Инкрементор

- •11.3. Вычитатели (субтракторы)

- •11.4. Компараторы

- •Основные характеристики компараторов

- •Компараторы аналоговых сигналов

- •Компараторы цифровых сигналов

- •Компаратор на базе сумматора

- •11.5. Арифметико-логические устройства

- •12. Импульсные устройства на имс

- •12.1. Формирователи импульсов

- •12.2. Схемы нормализации импульсов

- •12.3. Схемы укорачивания импульсов

- •12.4. Схемы задержки импульса

- •12.5. Одновибраторы

- •12.6. Генераторы тактовой частоты

- •13. Запоминающие устройства

- •13.1. Общие характеристики устройств

- •13.2. Запоминающие элементы постоянных зу

- •13.3. Оперативные запоминающие устройства

- •13.3.1. Динамические зу

- •13.3.2. Статические зу

- •14. Аналого-цифровые и цифро-аналоговые преобразователи

- •14.1. Общие сведения

- •14.2. Цифро-аналоговые преобразователи

- •14.3. Аналого-цифровые преобразователи

- •14.3.1. Характеристики и параметры ацп

- •14.3.2. Ацп последовательного счета

- •14.3.3. Параллельный ацп

- •14.3.4. Сигма-дельта ацп

- •Заключение

- •Библиографический список

- •Приложение 1 Перечень стандартов

- •Основные стандарты ескд

- •Система технологической документации

- •Стандарты системы информационно-библиографической документации

- •Система стандартов по безопасности труда

- •Разработка и постановка продукции на производство

- •Система стандартов программной документации

- •Основополагающие стандарты гсп

- •Приложение 2

- •Цифровых устройств

12.3. Схемы укорачивания импульсов

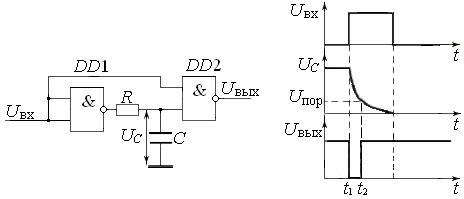

Схема 1. Создание импульса короче входного можно осуществить по схеме, представленной на рис. 12.2. Схема содержит два логических элемента И-НЕ и интегрирующую цепочку. Здесь RC-цепочка «заваливает» фронт на выходе элемента DD1 (напряжение UС). Логический элемент DD2 работает по прямому назначению: на один вход поступает входное напряжение Uвх непосредственно, а на другой – через интегрирующую RC-цепь. Только в интервале от t1 до t2 напряжение на конденсаторе UС превышает Uпор и совпадает с положительным напряжением на другом входе элемента DD2, вследствие чего на выходе DD2 возникает импульс низкого уровня. При построении временных диаграмм не учитывается длительность фронтов импульсов.

а б

б

Рис. 12.2. Схема укорачивания импульса на двух логических

элементах (а) и временная диаграмма (б)

Описанный процесс возможен для схем ТТЛ при R < 500 Ом. Если R > 5000 Ом, то на нижнем входе элемента DD2 будет постоянно присутствовать логическая единица. Схема будет выполнять функцию простого инвертора.

При 500 < R < 5000 Ом характер работы схемы будет определяться параметрами логических элементов.

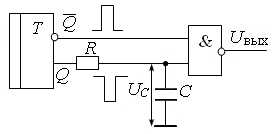

Схема

2.

Когда

для получения укороченного импульса

применяют выходной сигнал триггера

(рис. 12.3), элемент DD1

становится не нужным. В таком случае

обычно используют оба выхода триггера

Q

и

![]() ,

сигналы на которых взаимно инверсные.

Временные диаграммы имеют вид, как и в

предыдущем случае.

,

сигналы на которых взаимно инверсные.

Временные диаграммы имеют вид, как и в

предыдущем случае.

П ри

анализе работы схемы здесь также следует

учитывать величину сопротивленияR.

ри

анализе работы схемы здесь также следует

учитывать величину сопротивленияR.

Рис. 12.3. Схема укорачивания импульса с использованием триггера

Схема 3. В следующей схеме (рис. 12.4, а) используется тот же принцип, что и в первой схеме, но сигнал Uвх подается прямо на RC-цепочку. Временные диаграммы представлены на рис. 12.4, б, в.

Не трудно заметить, что в зависимости от уровня входного импульса Uвх совпадение сигналов высокого уровня на входах элемента DD2 обеспечивает укороченный импульс на выходе, совпадающий либо с передним фронтом входного сигнала низкого уровня (рис. 12.4, б), либо с задним фронтом положительного входного импульса (рис. 12.4, в).

а б

в

б

в

Рис 12.4. Схема формирования короткого импульса из переднего или заднего фронта (а) и временные диаграммы (б) и (в)

Выводы:

Укорочение импульса достигается за счет подачи на входы логического элемента взаимно инверсных сигналов, один из которых проходит через интегрирующую RC-цепь.

Длительность полученного импульса зависит от номинальных значений R и C. Допускается R £ 500 Ом и C = 1¸3 нф.

Точность длительности импульсов невелика.

Схема 4. Укорочение импульсов посредством одного логического элемента и дифференцирующей цепочки для Uвх высокого уровня (рис. 12.5, а).

При анализе работы схемы следует учитывать величину сопротивления в дифференцирующей цепочке. Схема позволяет вырабатывать укороченные импульсы по переднему или заднему фронту входного сигнала высокого уровня.

а б

Рис. 12.5. Схема формирования короткого импульса с одним

логическим элементом

Если R < 500 Ом, то в результате дифференцирования RC-цепочкой на входе ЛЭ образуются два остроконечных импульса положительной и отрицательной полярности, соответствующие фронту и спаду входного импульса. Обратное сопротивление диода VD гораздо больше сопротивления резистора R и на положительный остроконечный импульс не влияет. Для отрицательного остроконечного импульса в точке А определяющим является прямое сопротивление диода, которое гораздо меньше R. Поэтому дифференцированный сигнал имеет вид, как на рис.12.5 б, т.е. не имеет отрицательного выброса. Только в интервале t1–t2 потенциал UA превышает Uпор и действует как 1, тогда Uвых – низкого уровня. Здесь 100 < R < 500 Ом.

Для анализа работы устройства при R > 5000 Ом можно заменить его схему эквивалентной (рис. 12.6). Здесь входной сигнал представлен источником US, эмиттерный переход входного каскада логического элемента ТТЛ заменен резистором Rэп [6].

Рис. 12.6. Эквивалентная схема формирователя короткого импульса

В исходном состоянии (ключ S в положении 1) левая обкладка конденсатора соединена с общим проводом. Конденсатор заряжен до напряжения

UС = UА = Uп – UR1– Uэп ,

г деUп

– напряжение источника питания

устройства; UR1

– падение напряжения на резисторе R1

в базовой цепи многоэмиттерного

транзистора (см. схему базового элемента

ТТЛ); Uэп

– падение напряжения на эмиттерном

переходе многоэмиттерного транзистора.

При подключении входного сигнала US

(перевод ключа

S

в положение 2) на резисторе R

возникнет импульсное падение напряжения,

повышающее потенциал в точке А. Для

защиты входной цепи логического элемента

в этом случае следует подключить

параллельно диоду стабилитрон или вход

логического элемента соединить через

диод с плюсом источника питания.

Возникающий в результате дифференцирования

переднего фронта входного сигнала

положительный импульс напряжения не

изменит состояния логического элемента

(рис. 12.7), но перезарядит конденсатор.

деUп

– напряжение источника питания

устройства; UR1

– падение напряжения на резисторе R1

в базовой цепи многоэмиттерного

транзистора (см. схему базового элемента

ТТЛ); Uэп

– падение напряжения на эмиттерном

переходе многоэмиттерного транзистора.

При подключении входного сигнала US

(перевод ключа

S

в положение 2) на резисторе R

возникнет импульсное падение напряжения,

повышающее потенциал в точке А. Для

защиты входной цепи логического элемента

в этом случае следует подключить

параллельно диоду стабилитрон или вход

логического элемента соединить через

диод с плюсом источника питания.

Возникающий в результате дифференцирования

переднего фронта входного сигнала

положительный импульс напряжения не

изменит состояния логического элемента

(рис. 12.7), но перезарядит конденсатор.

Перевод ключа S в положение 1 аналогичен отключению входного сигнала (задний фронт импульса) и замыканию заряженного конденсатора на резистор R. Поскольку знак напряжения на обкладках конденсатора сменился, ток разряда конденсатора в первый момент снизит потенциал в точке А до нуля (рис. 12.7), а затем потенциал снова вернется к начальному значению:

UС = UА = Uп – UR1– Uэп.

При этом в течение интервала t1–t2 потенциал на входе логического элемента будет ниже Uпор, что вызовет появление на выходе схемы короткого импульса высокого уровня. Картина протекания процессов представлена на рис. 12.7.