- •Схемотехника эвм

- •Часть 2

- •Содержание

- •8. Регистры

- •8.1. Назначение и классификация регистров

- •8.2. Регистры памяти

- •8.3. Буферы данных

- •8.4. Регистры сдвига

- •Кольцевые счетчики

- •9. Мультиплексоры и демультиплексоры

- •9.1. Общие сведения

- •9.2. Мультиплексоры

- •9.3. Демультиплексоры

- •10. Шифраторы и дешифраторы

- •10.1. Шифраторы

- •10.2. Дешифраторы

- •11. Арифметические устройства

- •11.1. Сумматоры

- •Четвертьсумматор

- •Полусумматор

- •Полный одноразрядный двоичный сумматор

- •Сумматоры с последовательным переносом

- •11.2. Инкрементор

- •11.3. Вычитатели (субтракторы)

- •11.4. Компараторы

- •Основные характеристики компараторов

- •Компараторы аналоговых сигналов

- •Компараторы цифровых сигналов

- •Компаратор на базе сумматора

- •11.5. Арифметико-логические устройства

- •12. Импульсные устройства на имс

- •12.1. Формирователи импульсов

- •12.2. Схемы нормализации импульсов

- •12.3. Схемы укорачивания импульсов

- •12.4. Схемы задержки импульса

- •12.5. Одновибраторы

- •12.6. Генераторы тактовой частоты

- •13. Запоминающие устройства

- •13.1. Общие характеристики устройств

- •13.2. Запоминающие элементы постоянных зу

- •13.3. Оперативные запоминающие устройства

- •13.3.1. Динамические зу

- •13.3.2. Статические зу

- •14. Аналого-цифровые и цифро-аналоговые преобразователи

- •14.1. Общие сведения

- •14.2. Цифро-аналоговые преобразователи

- •14.3. Аналого-цифровые преобразователи

- •14.3.1. Характеристики и параметры ацп

- •14.3.2. Ацп последовательного счета

- •14.3.3. Параллельный ацп

- •14.3.4. Сигма-дельта ацп

- •Заключение

- •Библиографический список

- •Приложение 1 Перечень стандартов

- •Основные стандарты ескд

- •Система технологической документации

- •Стандарты системы информационно-библиографической документации

- •Система стандартов по безопасности труда

- •Разработка и постановка продукции на производство

- •Система стандартов программной документации

- •Основополагающие стандарты гсп

- •Приложение 2

- •Цифровых устройств

10.2. Дешифраторы

Дешифратор (декодер) – это комбинационное устройство с несколькими входами и выходами, у которого определенным комбинациям входных сигналов соответствует активное состояние одного из выходов. Дешифраторы преобразуют двоичный или двоично-десятичный код в унитарный код. Если декодер имеет n входов, m выходов и использует все возможные наборы входных переменных, то m = 2n. Такой декодер называют полным. Если используется лишь часть наборов, то такой декодер называют неполным. Дешифраторы используют, когда нужно обращаться к различным цифровым устройствам, и при этом номер устройства (его адрес) представлен двоичным кодом. Входы декодера (адресные входы) часто номеруют не порядковыми номерами, а в соответствии с весами двоичных разрядов, т. е. не 1, 2, 3, 4, а 1, 2, 4, 8.

Формально описать работу дешифратора можно, задав список функций, отрабатываемых каждым из его выходов Yi. Так, для дешифратора 3–8:

Yo

=

![]() ;Y1

=

;Y1

=

![]() ;Y2

=

;Y2

=

![]() ;

Y3

=

;

Y3

=![]() ;

... Y7

=a4a2a1.

;

... Y7

=a4a2a1.

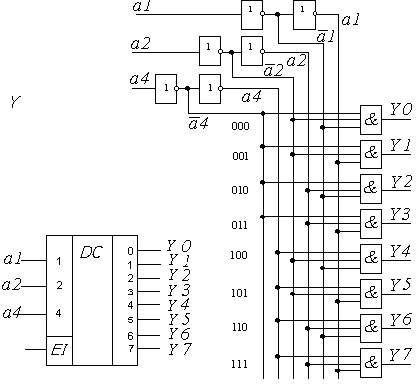

Число входов и выходов декодера указывают следующим образом: декодер 3–8 (читается “три в восемь”); 4–16; 4–10 (это неполный дешифратор). Реализация указанных восьми выражений с помощью восьми трехвходовых элементов И (рис. 10.7) дает наиболее простой по структуре дешифратор, называемый линейным.

а б

Рис. 10.7. Дешифратор 3-8: а – условное обозначение; б – структура

Основной объем его оборудования в общем случае m n-входовых элементов И. Кроме того, к оборудованию обычно относят n инверторов входных переменных и n буферных входных усилителей, сводящих к единице кратность нагрузки источника сигнала.

Дешифраторы часто имеют разрешающий вход EI. При EI = 1 дешифратор работает как обычно, а при EI = 0 на всех выходах устанавливаются не активные уровни.

Вход EI воздействует на все элементы И. В схеме (рис. 10.8) воздействие оказывается через прямой и инверсный входы одного из разрядов входного кода (через дополнительные элементы И). При этом число входов элементов И не изменяется, но в работу дешифратора вносится дополнительная задержка. В схеме (рис. 10.9) задержка не вносится, но здесь элементы И имеют большее число входов.

Разрешающий вход EI часто выполняется инверсным. Дешифратор, имеющий разрешающий вход, иногда называют декодер–демультиплексор и вместо обозначения DC используют обозначение DX. Это связано с тем, что вход EI иногда используют в качестве информационного (как в демультиплексорах).

Рис. 10.8. Разрешение через прямой и Рис. 10.9. Разрешение через

инверсный входы одного из разрядов дополнительные входы элементов И

Вход EI используется при построении древовидных (каскадных) схем дешифраторов с целью расширения адресного пространства. При этом все адресное пространство разбивается на группы. Старшие разряды адреса подаются на дешифратор старших разрядов, выходы которого по входам EI управляют дешифраторами второго каскада. На рис. 10.10 представлена схема двухкаскадного дешифратора 5–32 (пять в тридцать два).

Рис. 10.10. Двухкаскадный дешифратор 5–32

Два старших разряда адреса а16 и а8 расшифровываются дешифратором 2–4 DC4, который по входам ЕI управляет четырьмя дешифраторами второго каскада. Младшие разряды адреса а4, а2, а1 поступают на все дешифраторы второго каскада, но открытым по входу EI оказывается лишь один из них. Ему и будет принадлежать единственный из всех 32 возбужденный выход. Например, входной код 01111 у дешифратора DC4 делает активным выход 1. Этим сигналом и откроется дешифратор второй ступени DC1, а DC0, DC2, DC3 закрыты. У дешифратора DC1 сигнал появится на выводе 7, что соответствует 15 выходу всего дешифратора. Такой принцип используется при построении дешифратора на много выходов из микросхем дешифраторов с меньшим числом выходов.

В рассмотренном случае 5-разрядный адрес был разбит на две группы в 2 и 3 разряда. Это и определило структуру дешифратора. В общем случае многоразрядный адрес можно разбить на группы различными способами и каждому будет соответствовать свой вариант схемы. Варианты будут различаться задержкой и аппаратными затратами. Таким образом, можно ставить задачу выбора оптимальной, в заданной серии элементов, структуры.

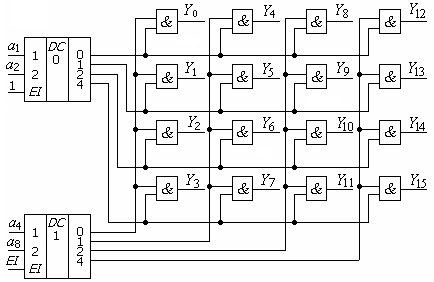

На рис. 10.11 показан двухкаскадный дешифратор 4–16, второй каскад которого собран по схеме прямоугольного дешифратора. Разряды адреса разбиты на две группы, каждая из которых независимо от другой расшифровывается своим дешифратором первого каскада DC0 и DC1. При любой комбинации значений входных переменных оказываются выбранными одна строка и один столбец сетки, в узлах которой расположены элементы И второй ступени (второго каскада). В результате каждый входной набор возбуждает выход единственного соответствующего ему элемента И. Такую сетку из элементов И называют прямоугольным или матричным дешифратором.

Рис. 10.11. Матричный дешифратор

Делить разряды адреса между DC1 и DC2 нужно по возможности поровну. Чем ближе прямоугольник второго каскада к квадрату, тем, при том же числе выходных элементов И, меньше сумма его строк и столбцов, т. е. меньше число выходов дешифраторов первого каскада. Из этого следует, что использование во втором каскаде квадратной матрицы, позволяет применить в первом каскаде наиболее простые дешифраторы и тем самым минимизировать общую задержку в работе всего дешифратора.

В качестве входа EI (Е) всего двухкаскадного дешифратора удобно использовать разрешающий вход только одного из дешифраторов первого каскада. При этом запираются или все строки или все столбцы.

Следует отметить, что при большом числе выходов (сотни и более) прямоугольный дешифратор самый экономичный по оборудованию, чем и объясняется его применение в БИС памяти. При малом числе выходов наиболее экономичным является линейный дешифратор.

Дешифраторы, выпускаемые в виде микросхем, имеют буквенное обозначение ИД, например, 155ИД3, 155ИД4. В сериях ТТЛ дешифраторы имеют обычно инверсные выходы, т. е. активным является низкий уровень. В КМОП-сериях выходные сигналы чаще имеют активный высокий уровень.

Часто в микросхемах дешифраторов делают несколько разрешающих входов, а разрешающей комбинацией является их конъюнкция. При этом удобно наращивать дешифраторы, используя каскадный принцип и строя первый каскад дешифрации не на отдельном специальном дешифраторе, а собирая его из конъюнкторов разрешающих входов. На рис. 10.12 представлен дешифратор 5–32 из 4 дешифраторов 3–8. Каждая микросхема имеет два инверсных разрешающих входа. Символ & над символом ЕI обозначает, что разрешение существует лишь при совпадении всех сигналов группы входов, помеченных знаком &. На рисунке символы инверсии указывают на совпадение двух низких уровней на входах разрешения.

Дешифратор первого каскада распределен по конъюнкторам 4 микросхем. Такое решение – иметь несколько разрешающих входов, связанных операцией И, чтобы собирать на этих входах фрагменты дешифраторов, вообще типично для современных микросхем [4, 9, 12, 15].

Рис. 10.12. Дешифрация адресов с использованием в первом каскаде разрешающих входов

Если использовать только два дешифратора DC0 и DC1, то можно получить дешифратор на 16 выходов. При этом адресный вход а16 будет отсутствовать, а нижние (по схеме) разрешающие входы дешифраторов DC0 и DC1 должны быть заземлены.

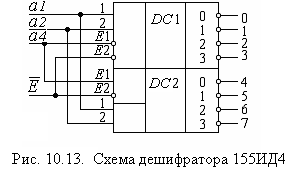

Схема дешифратора 155ИД4 представлена на рис. 10.13. В нее входят два дешифратора 2–4. Каждый дешифратор имеет пару разрешающих входов. Один разрешающий вход одной из секций инвертирован. Это позволяет, объединив его с неинвертированным разрешающим входом другой секции и подав на эту пару третью переменную а4, использовать ту же самую схему как дешифратор 3–8 с разрешающим входом Е. Кроме того, эта микросхема может быть использована как два демультиплексора с 1 входа на 4 выхода и как демультиплексор с одной линии на 8 выходов.

Рис. 10.13. Схема дешифратора 155ИД4.

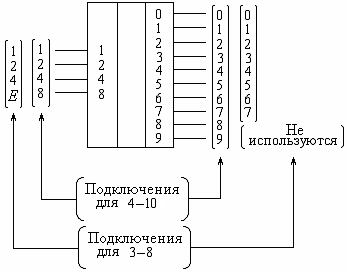

Рис. 10.14. Варианты подключения дешифратора 155ИД1

На рис. 10.14 показана возможность использования микросхемы 155ИД1 в качеств дешифратора 4–10 или 3–8. В представленной схеме при использовании всех четырех входов в качестве адресных микросхема представляет дешифратор 4–10. Если вход 8 использовать в качестве разрешающего входа, тогда микросхема будет служить дешифратором 3–8. Выходы 8 и 9 при этом не используются.

Дешифраторы могут применяться в качестве демультиплексора входных сигналов, а совместно с шифратором находят применение при построении преобразователей кодов, селектировании заданных входных кодов и др. [11]. Для реализации подобных устройств могут быть использованы программируемые логические матрицы или программируемые логические интегральные схемы (ПЛМ или ПЛИС) [15].