- •Псковский политехнический институт

- •Псковский политехнический институт

- •Варианты заданий к лабораторной работе

- •3. Содержание отчета.

- •130 Содержание

- •Порядок проведения лабораторной работы.

- •20__ Год

- •Описание лабораторной установки.

- •Краткие теоретические сведения.

- •Описание лабораторной установки.

- •Варианты заданий к лабораторной работе "Исследование мультиплексора".

- •Краткие теоретические сведения.

- •К раткие теоретические сведения.

- •3. Содержание отчета.

- •Варианты заданий к лабораторной работе "Исследование оперативного запоминающего устройства".

- •Порядок проведения лабораторной работы.

- •Описание лабораторной установки.

- •Описание лабораторной установки.

- •Краткие теоретические сведения.

- •Варианты заданий к лабораторной работе "Исследование синхронного счетчика".

- •Порядок проведения лабораторной работы.

- •3. Содержание отчета.

- •3. Содержание отчёта.

- •Порядок проведения лабораторной работы.

- •Варианты заданий к лабораторной работе "Исследование сумматора".

- •Описание лабораторной установки.

- •Краткие теоретические сведения.

- •Описание лабораторной установки.

- •Порядок проведения лабораторной работы.

- •Краткие теоретические сведения.

- •3. Содержание отчёта.

- •Варианты заданий к лабораторной работе "Исследование счетчика Джонсона"

- •Варианты заданий к лабораторной работе "Исследование матричного умножителя".

- •Краткие теоретические сведения.

- •Порядок проведения лабораторной работы.

- •Описание лабораторной установки.

- •Описание лабораторной установки.

- •Порядок проведения лабораторной работы.

- •Краткие теоретические сведения.

- •Варианты заданий к лабораторной работе "Исследование кольцевого счетчика".

- •3. Содержание отчета.

- •Варианты заданий к лабораторной работе "Исследование алу".

- •Краткие теоретические сведения.

- •Порядок проведения лабораторной работы

- •Описание лабораторной установки.

Описание лабораторной установки.

Лабораторная установка для проведения работы № 7 "Исследование синхронного счетчика на К-триггерах" состоит из лабораторного стенда, коммутатора цифровых сигналов и осциллографа. Внешний вид панелей лабораторного стенда и коммутатора приведен на рис. 7.8 и рис. 7.9.

Лабораторный стенд содержит все необходимые элементы для исследования работы синхронных суммирующих и вычитающих счетчиков с коэффициентами пересчета, указанными в вариантах задания.

Сборка макета счетчика осуществляется путем соединения требуемых гнезд проводниками со стандартными одиночными штеккерами. Для реализации разветвленных связей в комплекте со стендом имеются специальные соединители с увеличенным количеством штеккеров.

Коммутатор цифровых сигналов используется для одновременного наблюдения до восьми процессов на экране однолучевого осциллографа. Стенд коммутатора содержит ряд дополнительных элементов, которые могут использоваться для расширения функциональных возможностей лабораторной установки.

98

ЛАБОРАТОРНАЯ РАБОТА № 3.

"ИССЛЕДОВАНИЕ МАТРИЧНОГО УМНОЖИТЕЛЯ".

ЦЕЛЬЮ работы является ознакомление с принципами построения и функционирования матричных умножителей двоичных кодов чисел.

Краткие теоретические сведения.

Умножение, наряду со сложением, является одной из наиболее часто встречающихся арифметических операций, выполняемых цифровыми вычислительными машинами при обработке числовых данных. Однако, если сложение двух N-разрядных двоичных чисел в арифметическом устройстве такой же разрядности может быть выполнено за один такт, то для их умножения потребуется в общем случае гораздо больше времени. Это связано с необходимостью реализации N-1 операции сдвига, N операций сложения, а также операций запоминания промежуточных результатов и пересылок их в арифметическое устройство.

Ниже условно представлен один из вариантов процедуры перемножения двух четырехразрядных чисел 1101 и 1011, разбитый на элементарные операции (такты).

1. Умножить множимое 1101 на младший разряд множителя 1101·1=1101

2. Запомнить результат -1101.

3. Сдвинуть множимое на один разряд влево -11010.

4. Умножить на второй разряд множителя 11010·1=11010

5. Сложить с предыдущим результатом умножения

11010 + 1101=100111.

6. Запомнить результат -100111.

7. Сдвинуть множимое на два разряда влево -110100

8. Умножить на третий разряд множителя 110100·0=000000

9. Сложить с предыдущим результатом умножения 100111+000000=100111

З

35

апомнить результат -100111.

11. Сдвинуть множимое на три разряда влево 1101000.

12. Умножить на старший разряд множителя 1101000·1=1101000

13. Сложить с предыдущим результатом умножения 1101000+100111=10001111

Окончательный результат равен 10001111.

В реальных вычислительных устройствах процесс умножения оптимизируется, но, тем не менее, занимает достаточно длительное время. Наиболее существенным это обстоятельство является при построении специализированных цифровых процессоров, от которых требуется выполнение многих миллионов операций сложения и умножения в секунду.

М

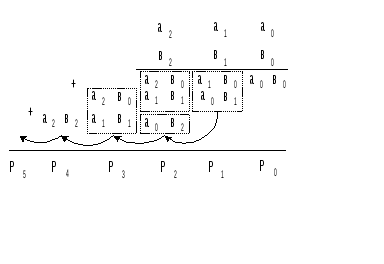

Рис. 3.1

Р

36

![]() и

и![]() .

Здесь индексы 0 - 2 указывают на номер

разряда, а символы

.

Здесь индексы 0 - 2 указывают на номер

разряда, а символы![]() и

и![]() являются его значением, которое может

быть нулём или едини-

являются его значением, которое может

быть нулём или едини-

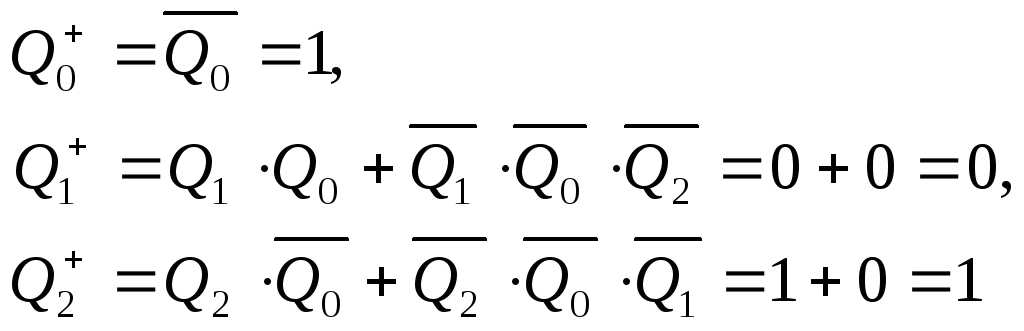

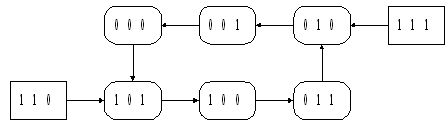

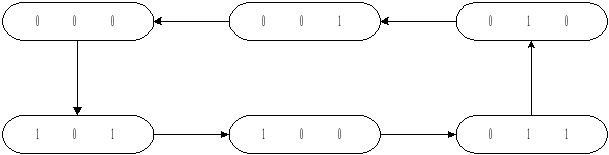

Следующим этапом проектирования счетчика является проверка его на самовосстановление после сбоев. Как уже отмечалось, сбоем считается самопроизвольное появление на выходах счетчика одной из исключаемых комбинаций. В рассматриваемом случае таких комбинаций две - 110 и 111. Проверка производится путем подстановки значений сигналов, соответствующих сбою в полученные ранее соотношения, и анализа получаемых результатов. В нашем случае наличие комбинации 110 вызовет переход счетчика в следующем такте в состояние 101, т. к.

Э

Здесь в прямоугольники заключены исключаемые состояния, соответствующие сбоям.

Анализ

поступившего на счетчик количества

импульсов производится по совокупности

сигналов на его выходах, иными словами

по его выходному коду, представленному

соответствующей комбинацией нулей и

единиц. Как уже отмечалось, каждому

разряду кода приписывается определенный

вес, обычно равный

![]() ,

гдеi

- номер разряда. В этом случае любое

состояние n-разрядного счетчика может

быть описано некоторым

числом S,

которое, в свою очередь, представляется

в одной из систем счисления: восьмеричной,

десятичной, шестнадцатеричной или

других.

,

гдеi

- номер разряда. В этом случае любое

состояние n-разрядного счетчика может

быть описано некоторым

числом S,

которое, в свою очередь, представляется

в одной из систем счисления: восьмеричной,

десятичной, шестнадцатеричной или

других.

97

При

единичных сигналах входы

![]() и

и![]() не влияют на работу триггера и его

переключение происходит по отрицательному

фронту синхроимпульса в зависимости

от комбинаций сигналов на входахJ

и К.

Если в реальных схемах не требуется

выполнения операции «И» по J

и К

входам, то незадействованные входы

соответствующих элементов И объединяются

между собой, либо на них подается сигнал

логической единицы.

не влияют на работу триггера и его

переключение происходит по отрицательному

фронту синхроимпульса в зависимости

от комбинаций сигналов на входахJ

и К.

Если в реальных схемах не требуется

выполнения операции «И» по J

и К

входам, то незадействованные входы

соответствующих элементов И объединяются

между собой, либо на них подается сигнал

логической единицы.

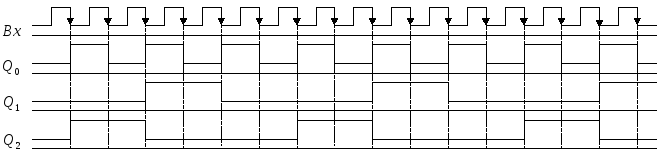

На рис. 7.6 приведена схема спроектированного синхронного вычитающего счетчика с модулем 6 на универсальных JK-триггерах, а на рис. 7.7 - временные диаграммы его работы, которые могут быть построены на основе графа переходов с учетом особенностей реальных триггеров. В данном случае такой особенностью является срабатывание триггера по отрицательному фронту входного сигнала.

Рис. 7.6

Рис. 7.7

96

цей. На рис. 3.1 представлен алгоритм перемножения. Символами Рi обозначены разряды произведения, количество которых в общем случае равно сумме разрядов сомножителей.

Из

представленного алгоритма следует, что

произведение получается путём суммирования

компонент вида

![]() ,

представляющих собой результат операции

логического умножения (операции И) над

соответствующими разрядами операндов.

Это возможно, вследствие идентичности

таблицы умножения чисел, принимающих

значения 0,1 и таблицы, определяющей

логическую функцию «И» над двумя

логическими переменными.

,

представляющих собой результат операции

логического умножения (операции И) над

соответствующими разрядами операндов.

Это возможно, вследствие идентичности

таблицы умножения чисел, принимающих

значения 0,1 и таблицы, определяющей

логическую функцию «И» над двумя

логическими переменными.

Так

как разряды сомножителей обычно поступают

в устройство умножения одновременно

(параллельно), то можно сразу сформировать

все частичные произведения

![]() и, сложив их, получить результат умножения.

Таким образом, здесь не требуется

выполнения операций сдвига и хранения

промежуточных данных. Однако, при

формировании некоторых разрядов

произведения (например P2)

понадобятся сумматоры для сложения

более чем двух одноразрядных операндов.

Такие сумматоры могут быть построены

путём соединения по определенной схеме

обычных одноразрядных и многоразрядных

сумматоров.

и, сложив их, получить результат умножения.

Таким образом, здесь не требуется

выполнения операций сдвига и хранения

промежуточных данных. Однако, при

формировании некоторых разрядов

произведения (например P2)

понадобятся сумматоры для сложения

более чем двух одноразрядных операндов.

Такие сумматоры могут быть построены

путём соединения по определенной схеме

обычных одноразрядных и многоразрядных

сумматоров.

Рис. 3.2

37

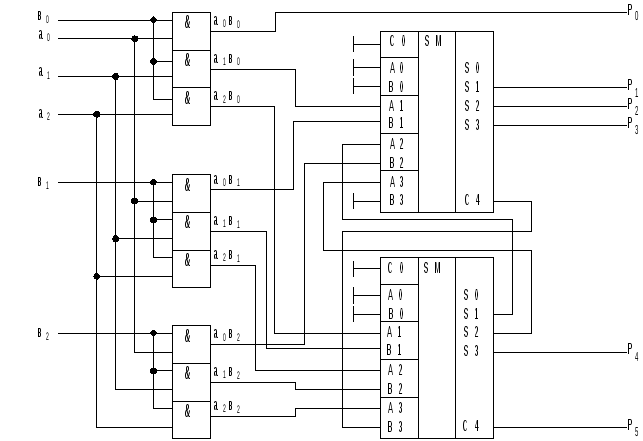

При разработке принципиальной схемы матричного умножителя удобно пользоваться следующей методикой. Представим полный одноразрядный сумматор в символическом виде, как показано на рис. 3.2. Его входными сигналами будут слагаемые А, В и перенос из предыдущего разряда С0, а выходными - сумма S и перенос С в следующий, более старший разряд. Структурная схема матричного умножителя трехразрядных двоичных чисел на основе таких сумматоров представлена на том же рис. 3.2.

На входы переноса верхнего ряда сумматоров, формирующих разряды Р1 и Р2 произведения подаются сигналы логического нуля. Для формирования разряда Р3 потребуется два сумматора, так как в общем случае может возникнуть два сигнала переноса при формировании первой и второй частичных сумм.

Из структуры умножителя вытекает, что по диагоналям одноразрядные сумматоры соединяются последовательно по сигналам переноса, образуя обычный многоразрядный сумматор. В рассматриваемом случае для построения матричного умножителя потребуется два трехразрядных сумматора и 9 логических схем типа 2И.

Промышленностью

выпускаются в интегральном исполнении

четырехразрядные сумматоры двоичных

чисел (К155ИМЗ, К555ИМ6), которые можно

использовать в рассматриваемом

умножителе. Для этого на младшие разряды

сумматоров

![]() и

и![]() подаются сигналы логического нуля и

эти разряды не участвуют в формировании

произведения. Принципиальная схема

быстрого умножителя на основе таких

сумматоров приведена на рис. 3.3.

подаются сигналы логического нуля и

эти разряды не участвуют в формировании

произведения. Принципиальная схема

быстрого умножителя на основе таких

сумматоров приведена на рис. 3.3.

38

Из полученных выражений следует, что для реализации счетчика кроме триггеров потребуются дополнительные схемы, выполняющие операцию логического умножения. Однако промышленностью выпускаются, так называемые универсальные JК-триггера, содержащие на входах J и K встроенные схемы И, а также имеющие ряд дополнительных входов управления.

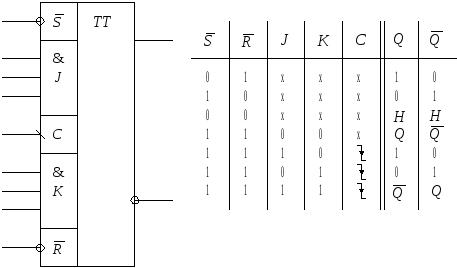

Функциональное

обозначение и таблица состояний одного

из таких триггеров - К155ТВ1 приведены на

рис. 7.5. Триггер имеет вход синхронизации

С, входы установки нуля -

![]() и единицы -

и единицы -![]() .

На входах J и К установлены элементы

«3И».

.

На входах J и К установлены элементы

«3И».

Рис. 7.5

При

определенной комбинации управляющих

сигналов на входах

![]() и

и![]() обеспечивается принудительная, независимо

от состояния других входов, установка

нулевого или единичного состояния

триггера. Одновременная подача логических

нулей на

обеспечивается принудительная, независимо

от состояния других входов, установка

нулевого или единичного состояния

триггера. Одновременная подача логических

нулей на![]() и

и![]() входы недопустима, так как после снятия

этой комбинации, триггер может перейти

в любое, заранее неизвестное - неопределенное

состояние.

входы недопустима, так как после снятия

этой комбинации, триггер может перейти

в любое, заранее неизвестное - неопределенное

состояние.

95

Если

теперь полученные соотношения сравнить

с функциями возбуждения соответствующих

триггеров, то будем иметь

![]() ,

,![]() .

Таким образом, функции

.

Таким образом, функции

![]() и

и

![]() описывают структуру связей входов

описывают структуру связей входов![]() и

и![]() с выходами остальных триггеров,

обеспечивающую получение требуемого

коэффициента пересчета.

с выходами остальных триггеров,

обеспечивающую получение требуемого

коэффициента пересчета.

Для установления и минимизации представления искомых функциональных связей, удобно воcпользоваться картами Карно, которые для рассматриваемого примера представлены на рис. 7.4.

Рис. 7.4

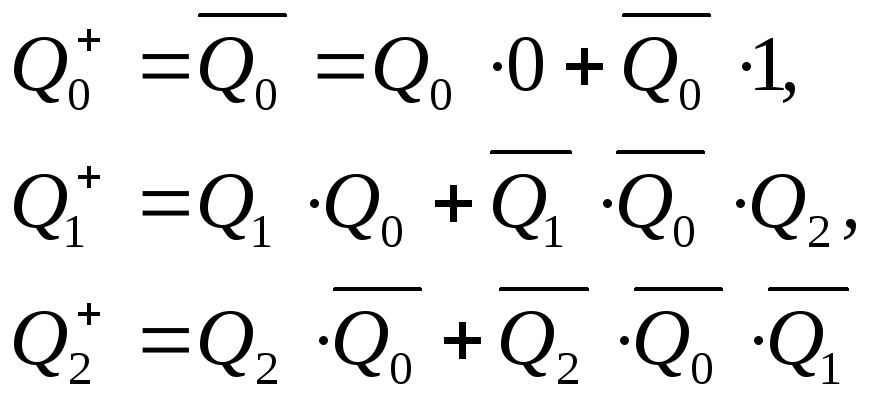

Крестиками отмечены неопределенные, произвольные состояния соответствующих функций. Воспользовавшись правилами минимизации, получим следующие соотношения с учетом требуемой формы представления функций:

О

94

Рис. 3.3

Рассмотренная структура умножителя часто называется матричной, так как для её реализации требуется совокупность (матрица) одноразрядных сумматоров. Время выполнения операции умножения в таких схемах определяется задержками в элементах «И» и многоразрядных сумматорах. В данной конкретной схеме при использовании микросхем серии К155, оно не превышает 80-100 нС.

В настоящее время промышленностью выпускаются специальные множительно-суммирующие блоки, реализующие операцию Р=А·В+С+D. Объединяя эти блоки по определенному алгоритму, можно строить многоразрядные умножители без дополнительных логических элементов. Примером такого блока является микросхема К555ИП8 (умножитель четырехразрядного числа на двухразрядное - умножитель 4х2). Кроме этого разработаны и выпускаются полностью законченные быстрые умножители восьмиразрядных чисел - К1802ВРЗ, двенадцатиразрядных - К1802ВР4 и шестнадцатиразрядных - К1802ВР5.

39

Они позволяют перемножать и знакопеременные числа (в дополнительном коде). Время выполнения операция умножения в этих микросхемах не превышает 100 - 130 нС.

|

Десятичное число |

Двоичный код |

Шестнадцатеричный код |

|

0 |

0 0 0 0 |

0 |

|

1 |

0 0 0 1 |

1 |

|

2 |

0 0 1 0 |

2 |

|

3 |

0 0 1 1 |

3 |

|

4 |

0 1 0 0 |

4 |

|

5 |

0 1 0 1 |

5 |

|

6 |

0 1 1 0 |

6 |

|

7 |

0 1 1 1 |

7 |

|

8 |

1 0 0 0 |

8 |

|

9 |

1 0 0 1 |

9 |

|

10 |

1 0 1 0 |

A |

|

11 |

1 0 1 1 |

B |

|

12 |

1 1 0 0 |

C |

|

13 |

1 1 0 1 |

D |

|

14 |

1 1 1 0 |

E |

|

15 |

1 1 1 1 |

F |

|

Рис. 3.4 | ||

|

Веса разр. |

|

|

| ||

|

дес. код |

|

|

дес. код | ||

|

5 |

1 0 1 |

1 0 0 |

4 | ||

|

4 |

1 0 0 |

0 1 1 |

3 | ||

|

3 |

0 1 1 |

0 1 0 |

2 | ||

|

2 |

0 1 0 |

0 0 1 |

1 | ||

|

1 |

0 0 1 |

0 0 0 |

0 | ||

|

0 |

0 0 0 |

1 0 1 |

5 | ||

|

Рис. 7.3 | |||||

П

40

93

Из приведенной выше формулы следует, что для реализации требуемого модуля счета потребуется три триггера. Так как двоичный счетчик на трех триггерах имеет восемь состояний, то для получения модуля счета 6, два из них нужно исключить. Пусть это будут состояния 111 и 110. Таким образом, граф переходов синтезируемого счетчика будет иметь вид (рис. 7.2).

Рис. 7.2

Далее составляется таблица переходов (рис. 7.3), в левой части которой описываются состояния разрядов счетчика до, а в правой после каждого переключения.

На следующем этапе

синтеза находятся функциональные

зависимости

![]() отражающие связи состояний триггеров

до и после переключения счетчика, которые

целесообразно представлять в таком

виде, гдеFиФ- некоторые

логические функции.

отражающие связи состояний триггеров

до и после переключения счетчика, которые

целесообразно представлять в таком

виде, гдеFиФ- некоторые

логические функции.

счетчика,

минимальное число разрядов которого

определяется соотношением

![]() .

.

Функция

ent

означает взятие целой части ее аргумента.

Исключать состояния у двоичного счетчика

в принципе можно, произвольным образом,

поэтому количество разновидностей

счетчиков с модулем L,

получаемых из исходного двоичного

счетчика с модулем

![]() будет равно

будет равно![]() .

.

В реальных схемах, исключенные при синтезе недвоичных счетчиков состояния, могут самопроизвольно возникать из-за различного рода помех и наводок. Это приводит к сбоям в работе, связанных со счетчиком, устройств. Ряд вариантов недвоичных счетчиков могут через определенное число тактов после сбоя вернуться в рабочее состояние, но некоторые будут сколь угодно долго оставаться в состоянии сбоя (зацикливаться).

В связи с этим при разработке недвоичных счетчиков обязательной является проверка на самовосстановление после любого варианта сбоя. Если же возвращения к нормальной работе не происходит, то требуется создание специальных устройств, обеспечивающих надежную работу счетчиков.

Синтез синхронного счетчика с произвольным модулем счета производится следующим образом: выбирается тип триггеров, которые будут использоваться в счетчике, определяется их количество для обеспечения требуемого модуля счета, устанавливается структура связей между триггерами и проводится анализ полученного счетчика на помехоустойчивость.

Рассмотрим

пример синтеза синхронного вычитающего

счетчика с модулем 6. Обычно в качестве

разрядов счетчика используются триггера

JK типа. Их функция возбуждения описывается

следующим выражением

![]() ,

где

,

где![]() - состояние выхода триггера после

переключения.

- состояние выхода триггера после

переключения.

92

(основания системы счисления). Например,

![]() .

.

Умножение

чисел в шестнадцатеричном коде

производится по тем же правилам, что в

двоичном и десятичном. Однако таблица

умножения будет содержать

![]() элементов. На рис. 3.5 приведены таблицы

умножения чисел от 0 до 9 в десятичной

системе счисления и фрагмент таблицы

умножения таких же чисел в шестнадцатеричной

системе.

элементов. На рис. 3.5 приведены таблицы

умножения чисел от 0 до 9 в десятичной

системе счисления и фрагмент таблицы

умножения таких же чисел в шестнадцатеричной

системе.

|

в |

0 |

1 |

2 |

3 |

4 |

5 |

6 |

7 |

8 |

9 |

|

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

|

1 |

0 |

1 |

2 |

3 |

4 |

5 |

6 |

7 |

8 |

9 |

|

2 |

0 |

2 |

4 |

6 |

8 |

10 |

12 |

14 |

16 |

18 |

|

3 |

0 |

3 |

6 |

9 |

12 |

15 |

18 |

21 |

24 |

27 |

|

4 |

0 |

4 |

8 |

12 |

16 |

20 |

24 |

28 |

32 |

36 |

|

5 |

0 |

5 |

10 |

15 |

20 |

25 |

30 |

35 |

40 |

45 |

|

6 |

0 |

6 |

12 |

18 |

24 |

30 |

36 |

42 |

48 |

54 |

|

7 |

0 |

7 |

14 |

21 |

28 |

35 |

42 |

49 |

56 |

63 |

|

8 |

0 |

8 |

16 |

24 |

32 |

40 |

48 |

56 |

64 |

72 |

|

9 |

0 |

9 |

18 |

27 |

36 |

45 |

54 |

63 |

72 |

81 |

Рис. 3.5 а

|

в |

0 |

1 |

2 |

3 |

4 |

5 |

6 |

7 |

8 |

9 |

|

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

|

1 |

0 |

1 |

2 |

3 |

4 |

5 |

6 |

7 |

8 |

9 |

|

2 |

0 |

2 |

4 |

6 |

8 |

А |

С |

Е |

10 |

12 |

|

3 |

0 |

3 |

6 |

9 |

С |

F |

12 |

15 |

18 |

1C |

|

4 |

0 |

4 |

8 |

C |

10 |

14 |

18 |

1C |

20 |

24 |

|

5 |

0 |

5 |

A |

F |

14 |

19 |

1E |

23 |

28 |

2D |

|

6 |

0 |

6 |

C |

12 |

18 |

1E |

24 |

2A |

30 |

36 |

|

7 |

0 |

7 |

E |

15 |

1C |

23 |

2A |

31 |

38 |

3F |

|

8 |

0 |

8 |

10 |

18 |

20 |

28 |

30 |

38 |

40 |

48 |

|

9 |

0 |

9 |

12 |

1C |

24 |

2D |

36 |

3F |

48 |

51 |

Рис.3.5 б

41

а

а а

а