- •Псковский политехнический институт

- •Псковский политехнический институт

- •Варианты заданий к лабораторной работе

- •3. Содержание отчета.

- •130 Содержание

- •Порядок проведения лабораторной работы.

- •20__ Год

- •Описание лабораторной установки.

- •Краткие теоретические сведения.

- •Описание лабораторной установки.

- •Варианты заданий к лабораторной работе "Исследование мультиплексора".

- •Краткие теоретические сведения.

- •К раткие теоретические сведения.

- •3. Содержание отчета.

- •Варианты заданий к лабораторной работе "Исследование оперативного запоминающего устройства".

- •Порядок проведения лабораторной работы.

- •Описание лабораторной установки.

- •Описание лабораторной установки.

- •Краткие теоретические сведения.

- •Варианты заданий к лабораторной работе "Исследование синхронного счетчика".

- •Порядок проведения лабораторной работы.

- •3. Содержание отчета.

- •3. Содержание отчёта.

- •Порядок проведения лабораторной работы.

- •Варианты заданий к лабораторной работе "Исследование сумматора".

- •Описание лабораторной установки.

- •Краткие теоретические сведения.

- •Описание лабораторной установки.

- •Порядок проведения лабораторной работы.

- •Краткие теоретические сведения.

- •3. Содержание отчёта.

- •Варианты заданий к лабораторной работе "Исследование счетчика Джонсона"

- •Варианты заданий к лабораторной работе "Исследование матричного умножителя".

- •Краткие теоретические сведения.

- •Порядок проведения лабораторной работы.

- •Описание лабораторной установки.

- •Описание лабораторной установки.

- •Порядок проведения лабораторной работы.

- •Краткие теоретические сведения.

- •Варианты заданий к лабораторной работе "Исследование кольцевого счетчика".

- •3. Содержание отчета.

- •Варианты заданий к лабораторной работе "Исследование алу".

- •Краткие теоретические сведения.

- •Порядок проведения лабораторной работы

- •Описание лабораторной установки.

Варианты заданий к лабораторной работе "Исследование мультиплексора".

|

Вариант |

Логическая функция |

Отношение чисел |

|

1 |

|

у=1 при А=В |

|

2 |

|

у=1

при А |

|

3 |

|

у=1 при А>В |

|

4 |

|

у=1 при А<В |

|

5 |

|

у=1

при А |

|

6 |

|

у=1

при А |

|

7 |

|

у=1 при А=В |

|

8 |

|

у=1

при А |

16

ЛАБОРАТОРНАЯ РАБОТА № 9.

“ИССЛЕДОВАНИЕ СТЕКОВОГО ЗАПОМИНАЮЩЕГО

УСТРОЙСТВА”.

ЦЕЛЬЮ работы является ознакомление с принципами построения и функционирования оперативных запоминающих устройств с безадресной организацией памяти.

Краткие теоретические сведения.

Оперативное запоминающее устройство (ОЗУ) представляет собой совокупность запоминающих ячеек, называемых накопителем, и схем управления. В каждую из ячеек можно записать информацию в виде сигнала логического нуля или логической единицы и считывать ее на внешние устройства. Ячейки накопителя могут объединяться в группы. В этом случае запись информации производится сразу в группу ячеек, также одновременно осуществляется и считывание.

Основной характеристикой запоминающего устройства является его емкость, которая числено равна количеству запоминающих ячеек накопителя. Единицей измерения емкости является "бит" и производные от его величины 1Кбит=1К=1024 бит и т.д. Емкость многоразрядных ОЗУ обычно записывается в виде произведения количества групп запоминающих ячеек на их разрядность, например: 16×8 бит, 2К×16 бит.

Для записи и считывания информации из нужной ячейки ее необходимо активизировать, или выбрать, для чего требуется подать специальные управляющие сигналы. По способу выбора ячейки, то есть нахождения ее в массиве накопителя все ОЗУ можно разделить на два класса - адресного типа и безадресные, в состав которых входят и так называемые стековые ОЗУ.

В

117

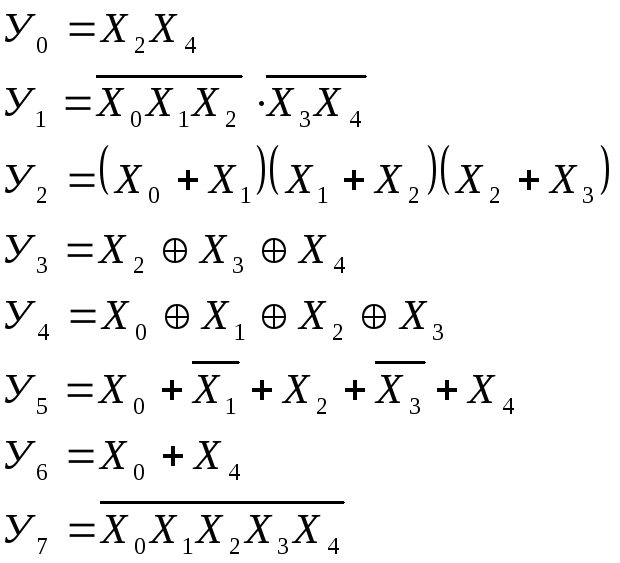

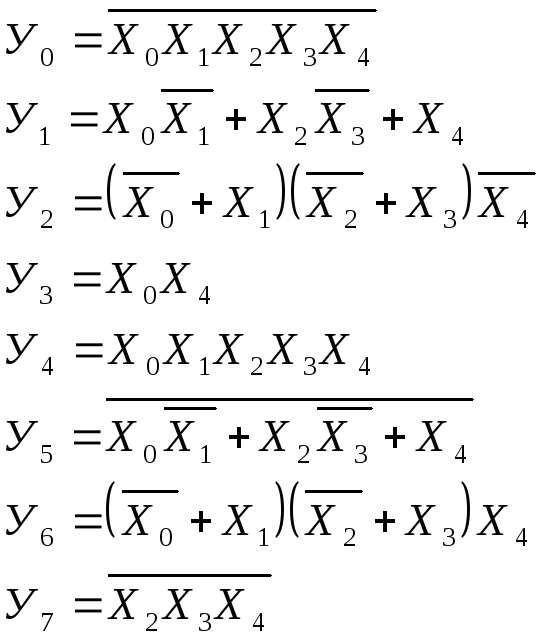

|

№ |

Логическая функция |

№ |

Логическая функция |

|

7 |

|

8 |

|

|

9 |

|

10 |

|

116

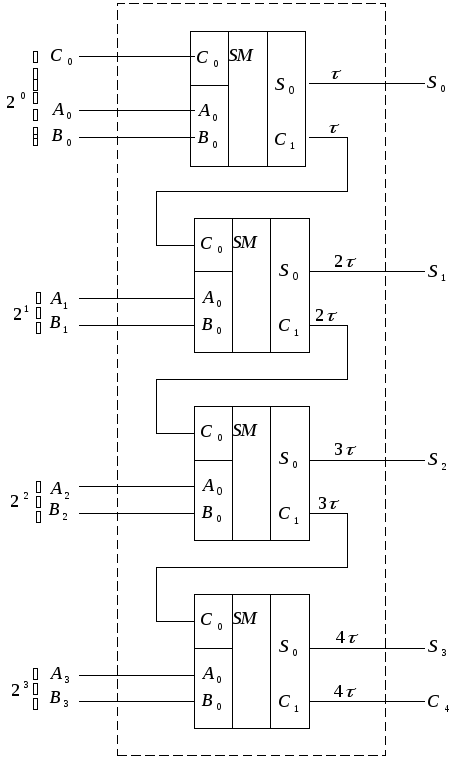

ЛАБОРАТОРНАЯ РАБОТА № 2.

"ИССЛЕДОВАНИЕ СУММАТОРА".

ЦЕЛЬЮ лабораторной работы является ознакомление с принципами работы двоичного, двоично-десятичного сумматоров и устройства вычитания кодов чисел.

К раткие теоретические сведения.

П

А0

В0

С0

S0

C1

0

0

1

1

0

0

1

1

0

1

0

1

0

1

0

1

0

0

0

0

1

1

1

1

0

1

1

0

1

0

0

1

0

0

0

1

0

1

1

1

Рис. 2.1

Как следует из таблицы функционирования, сумма S0 описывается логическим выражением:

![]() ,

а функция переноса после минимизации

будет иметь вид

,

а функция переноса после минимизации

будет иметь вид

![]() .

Данные соотношения могут быть реализованы

путем соответствующей обработки входных

сигналов сумматора с использованием

различных наборов логических элементов.

.

Данные соотношения могут быть реализованы

путем соответствующей обработки входных

сигналов сумматора с использованием

различных наборов логических элементов.

П

17

Э

Рис. 2.2

Недостатком, приведенного на рис. 2.2 сумматора с последовательным переносом, является значительное время требуемое на формирование результата. В общем случае задержка получения последнего разряда, а следовательно и всей суммы составляет

Рис. 2.3![]()

![]() - время задержки получения частичной

суммы, а

- время задержки получения частичной

суммы, а![]() -

время, через которое появляется сигнал

переноса. Считая в первом приближении,

что

-

время, через которое появляется сигнал

переноса. Считая в первом приближении,

что

![]() ,

получим, что

,

получим, что![]() .

.

Д

18

![]() при любом количестве разрядов.

при любом количестве разрядов.

|

№ |

Адрес |

Тип индикатора |

№ |

Адрес |

Тип индикатора |

|

9 |

0 - 15 16 - 31 |

ОА ОК |

10 |

0 - 15 16 - 31 |

ОК ОА |

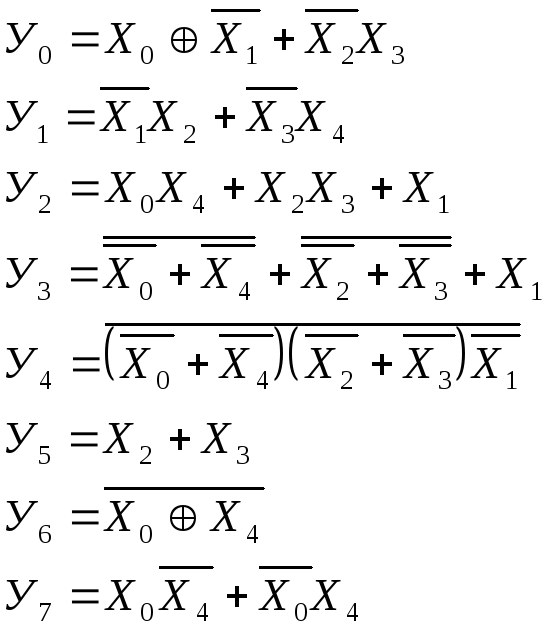

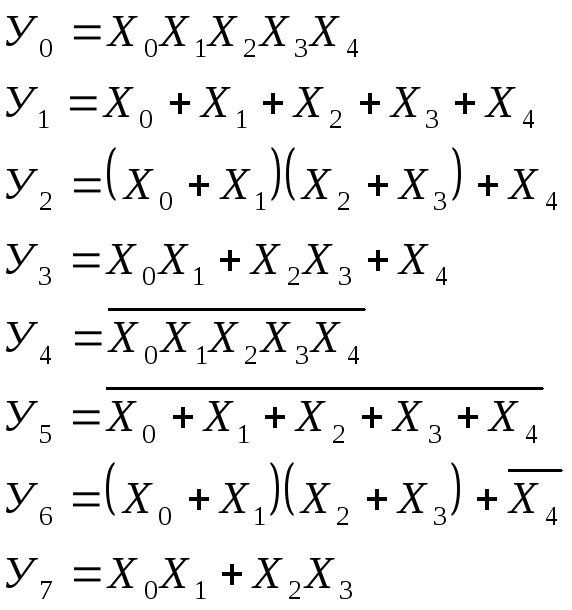

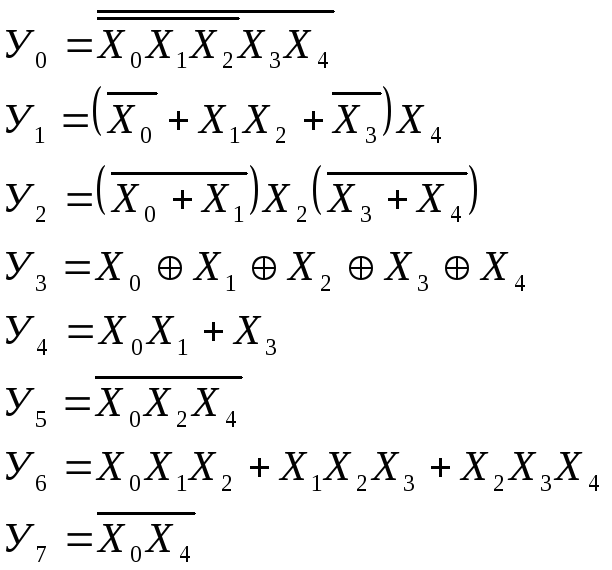

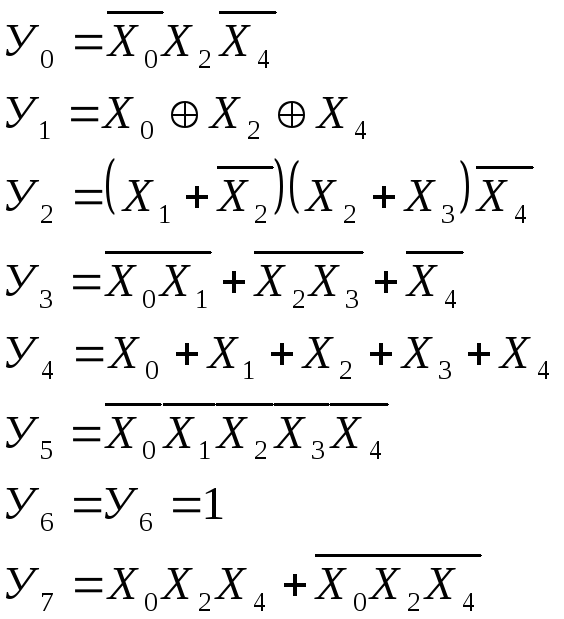

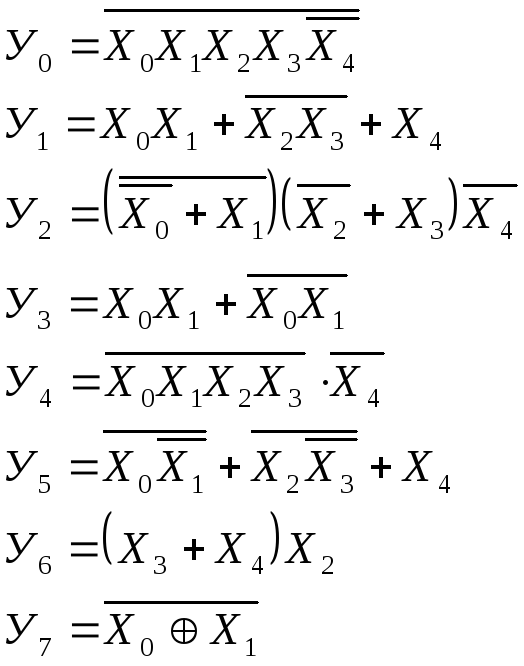

Формирователь логических функций.

|

№ |

Логическая функция |

№ |

Логическая функция |

|

1 |

|

2 |

|

|

3 |

|

4 |

|

|

115 |

|

6 |

|

м

Рис. 2.4

Все данные, полученные в ходе лабораторной работы, должны быть зафиксированы в рабочей тетради, в которой, по окончании работы делается соответствующая запись преподавателя.