- •Псковский политехнический институт

- •Псковский политехнический институт

- •Варианты заданий к лабораторной работе

- •3. Содержание отчета.

- •130 Содержание

- •Порядок проведения лабораторной работы.

- •20__ Год

- •Описание лабораторной установки.

- •Краткие теоретические сведения.

- •Описание лабораторной установки.

- •Варианты заданий к лабораторной работе "Исследование мультиплексора".

- •Краткие теоретические сведения.

- •К раткие теоретические сведения.

- •3. Содержание отчета.

- •Варианты заданий к лабораторной работе "Исследование оперативного запоминающего устройства".

- •Порядок проведения лабораторной работы.

- •Описание лабораторной установки.

- •Описание лабораторной установки.

- •Краткие теоретические сведения.

- •Варианты заданий к лабораторной работе "Исследование синхронного счетчика".

- •Порядок проведения лабораторной работы.

- •3. Содержание отчета.

- •3. Содержание отчёта.

- •Порядок проведения лабораторной работы.

- •Варианты заданий к лабораторной работе "Исследование сумматора".

- •Описание лабораторной установки.

- •Краткие теоретические сведения.

- •Описание лабораторной установки.

- •Порядок проведения лабораторной работы.

- •Краткие теоретические сведения.

- •3. Содержание отчёта.

- •Варианты заданий к лабораторной работе "Исследование счетчика Джонсона"

- •Варианты заданий к лабораторной работе "Исследование матричного умножителя".

- •Краткие теоретические сведения.

- •Порядок проведения лабораторной работы.

- •Описание лабораторной установки.

- •Описание лабораторной установки.

- •Порядок проведения лабораторной работы.

- •Краткие теоретические сведения.

- •Варианты заданий к лабораторной работе "Исследование кольцевого счетчика".

- •3. Содержание отчета.

- •Варианты заданий к лабораторной работе "Исследование алу".

- •Краткие теоретические сведения.

- •Порядок проведения лабораторной работы

- •Описание лабораторной установки.

Описание лабораторной установки.

Установка для проведения лабораторной работы № 9 "Исследование стекового запоминающего устройства" состоит из лабораторного стенда, внешний вид которого приведен на рис. 9.7. Стенд содержит все необходимые элементы для создания и исследования принципов функционирования стекового ЗУ емкостью 16×8.

126

ЛАБОРАТОРНАЯ РАБОТА № 1.

"ИССЛЕДОВАНИЕ МУЛЬТИПЛЕКСОРА".

ЦЕЛЬЮ работы является ознакомление с принципами работы типовых мультиплексоров, способами наращивания их разрядности и вариантами применения.

Краткие теоретические сведения.

Мультиплексором

или коммутатором называется комбинационная

логическая схема, реализующая операцию

передачи цифрового сигнала с любого из

N его информационных входов на выход.

Номер выбираемого входа задаётся

двоичным кодом, который поступает на

специальные управляющие входы

мультиплексора. Количество управляющих

входов n и входов данных N связано

соотношением N=![]() .

Мультиплексорc

N

входами часто обозначается как

мультиплексор типа

.

Мультиплексорc

N

входами часто обозначается как

мультиплексор типа

![]() .

.

Логическая функция, описывающая состояние выхода мультиплексора в общем случае задаётся соотношением:

![]()

где

![]() и

и![]() - знаки логического сложения и умножения,

- знаки логического сложения и умножения,

![]() -

коэффициенты разложения номера входа

j в двоичный код, принимающие значения

0 и 1.

-

коэффициенты разложения номера входа

j в двоичный код, принимающие значения

0 и 1.

Из данного соотношения следует, что на основе логических элементов, реализующих операции И, ИЛИ, НЕ возможно построение мультиплексоров на любое число входов.

Однако,

более оптимальным является путь, при

котором, с целью наращивания разрядности,

используются типовые мультиплексоры,

обычно выпускаемые в виде отдельных

микросхем. На рис. 1.1 приведено

функциональное обозначение и таблица

истинности мультиплексора 4![]() 1,

промышленностью выпускаются также

мультиплексоры 8

1,

промышленностью выпускаются также

мультиплексоры 8![]() 1,

16

1,

16![]() 1.

1.

7

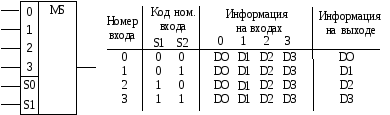

Рис. 1.1

Н

Рис. 1.2

Первый

заключается в том, что одноименные входы

![]() идентичных

мультиплексоров объединяются и на них

подаются младшие разряды управляющего

кода.

идентичных

мультиплексоров объединяются и на них

подаются младшие разряды управляющего

кода.

Старшие

разряды кода подаются на входы управления

дополнительного мультиплексора, входы

данных которого подключаются к выходам

предыдущих, а выход является выходом

всего устройства. На рис. 1.2 приведена

структурная схема мультиплексора 64![]() 1,

собранного на мультиплексорах 8

1,

собранного на мультиплексорах 8![]() 1.

1.

В

8

8

запись информации со входов D0-D3 в группу ячеек по адресу, заданному комбинацией сигналов на входах A0-A3.

В

режиме хранения на вход

![]() подается логическая единица. При этом

сигналы на управляющем входе, входах

адресов и данных не влияют на состояние

ОЗУ, выходы которого переходят в режим

с высоким выходным сопротивлением или

в Z-состояние. В такой ситуации выводы

подается логическая единица. При этом

сигналы на управляющем входе, входах

адресов и данных не влияют на состояние

ОЗУ, выходы которого переходят в режим

с высоким выходным сопротивлением или

в Z-состояние. В такой ситуации выводы![]() микросхемы фактически отключаются от

ячеек накопителя ОЗУ и на них могут быть

поданы произвольные логические сигналы.

Данное обстоятельство позволяет

подключать в таком режиме выходы ОЗУ к

шинам, по которым производится передача

информации от других источников.

микросхемы фактически отключаются от

ячеек накопителя ОЗУ и на них могут быть

поданы произвольные логические сигналы.

Данное обстоятельство позволяет

подключать в таком режиме выходы ОЗУ к

шинам, по которым производится передача

информации от других источников.

Четырехразрядный

реверсивный двоичный счетчик, обозначенный

СТ2, может работать в режимах предустановки,

прямого и обратного счета. В первом

режиме по отрицательному перепаду

сигнала на входе

![]() происходит занесение в разряды счетчика

информации со входовD0-D3

и появление ее на выходах

происходит занесение в разряды счетчика

информации со входовD0-D3

и появление ее на выходах

![]() .

.

В

режиме счета на вход

![]() подается сигнал логической единицы.

При наличии логической единицы на входе

"

подается сигнал логической единицы.

При наличии логической единицы на входе

"![]() 1"

происходит увеличение содержимого

счетчика с приходом положительного

фронта импульса синхронизации С. Если

же на вход "

1"

происходит увеличение содержимого

счетчика с приходом положительного

фронта импульса синхронизации С. Если

же на вход "![]() 1"

подан сигнал логического нуля, то счетчик

будет работать в режиме вычитания и, с

поступлением положительного фронта

очередного импульса синхронизации, его

содержимое будет на единицу уменьшаться.

1"

подан сигнал логического нуля, то счетчик

будет работать в режиме вычитания и, с

поступлением положительного фронта

очередного импульса синхронизации, его

содержимое будет на единицу уменьшаться.

Р

125![]() и поступлении положительного фронта

импульса на вход С. Если на данном входе

присутствуют сигналы логического нуля

или единицы, то регистр находится в

режиме хранения, при котором возможно

считывание,

и поступлении положительного фронта

импульса на вход С. Если на данном входе

присутствуют сигналы логического нуля

или единицы, то регистр находится в

режиме хранения, при котором возможно

считывание,

на

вход выбора кристалла

![]() поступает сигнал логического нуля, если

при этом на входе управления режимом

записи считывания

поступает сигнал логического нуля, если

при этом на входе управления режимом

записи считывания![]() присутствует логическая единица, то

осуществляется чтение информации

одновременно из четырех ячеек.

присутствует логическая единица, то

осуществляется чтение информации

одновременно из четырех ячеек.

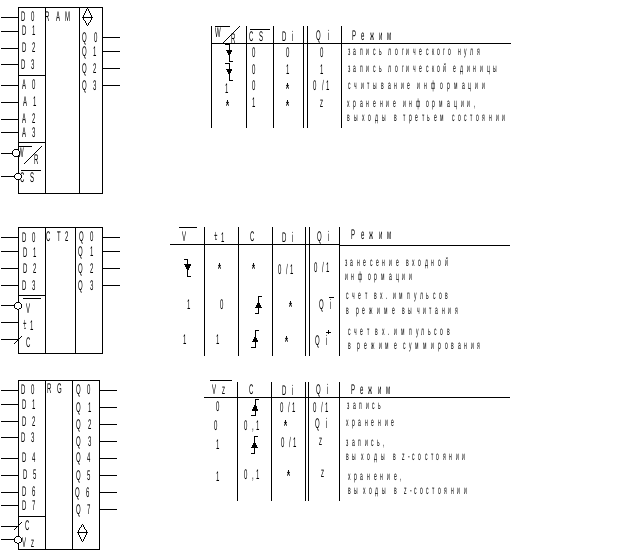

Рис. 9.5

В

124![]() отрицательного перепада управляющего

сигнала происходит

отрицательного перепада управляющего

сигнала происходит

Например,

если управляющий код равен числу

![]() в двоичной системе или

в двоичной системе или![]() в десятичной, то первой группой

мультиплексоров будет воспринята

кодовая комбинация 110, а на управление

выходным поступит код 010. При этом к

выходам линейки мультиплексоров будут

подключены сигналы с их входов с номерами

6, или с внешних информационных входовD6,

D14,

D22,

D3О,

D38,

D46,

D54,

D62.

Под действием старших разрядов

управляющего кода к выходу устройства

окажется подключенным сигнал только с

шестого входа третьего по счёту

мультиплексора – т.е. сигнал с

информационного входа под номером 22.

в десятичной, то первой группой

мультиплексоров будет воспринята

кодовая комбинация 110, а на управление

выходным поступит код 010. При этом к

выходам линейки мультиплексоров будут

подключены сигналы с их входов с номерами

6, или с внешних информационных входовD6,

D14,

D22,

D3О,

D38,

D46,

D54,

D62.

Под действием старших разрядов

управляющего кода к выходу устройства

окажется подключенным сигнал только с

шестого входа третьего по счёту

мультиплексора – т.е. сигнал с

информационного входа под номером 22.

|

Входы Х2 Х1 Х0 |

Выходы 0 1 2 3 4 5 6 7 |

|

0 0 0 |

0 1 1 1 1 1 1 1 |

|

0 0 1 |

1 0 1 1 1 1 1 1 |

|

0 1 0 |

1 1 0 1 1 1 1 1 |

|

0 1 1 |

1 1 1 0 1 1 1 1 |

|

1 0 0 |

1 1 1 1 0 1 1 1 |

|

1 0 1 |

1 1 1 1 1 0 1 1 |

|

1 1 0 |

1 1 1 1 1 1 0 1 |

|

1 1 1 |

1 1 1 1 1 1 1 0 |

|

Рис. 1.3 | |

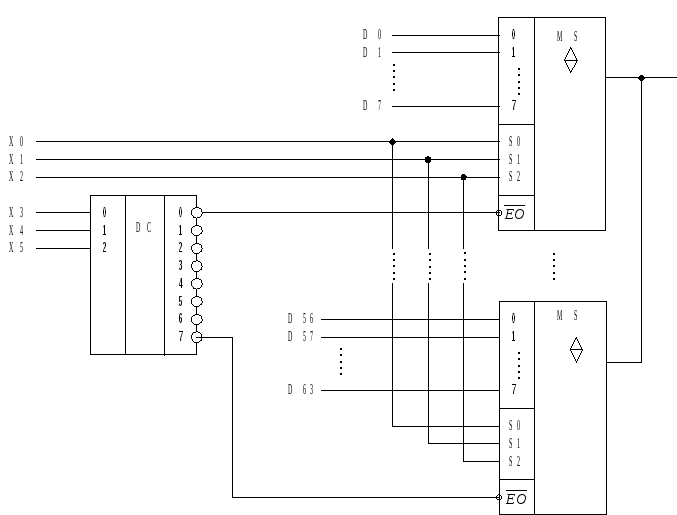

Д

9![]() 3

приведена на рисунке 1.3, а структурная

схема многоразрядного мультиплексора

на рис.1.4. Под действием старших разрядов

входного управляющего кода

3

приведена на рисунке 1.3, а структурная

схема многоразрядного мультиплексора

на рис.1.4. Под действием старших разрядов

входного управляющего кода![]() сигнал

сигнал

логического

нуля появляется только на одном из

выходов дешифратора и переводит нулевым

сигналом по входу

![]() соответствующий мультиплексор в активное

состояние. На выходах остальных

мультиплексоров никакие сигналы

формироваться не будут, так как они

находятся в третьем (Z) состоянии, что и

позволяет соединять их друг с другом.

соответствующий мультиплексор в активное

состояние. На выходах остальных

мультиплексоров никакие сигналы

формироваться не будут, так как они

находятся в третьем (Z) состоянии, что и

позволяет соединять их друг с другом.

Под

действием младших разрядов управляющего

кода

![]() выбираются

одноимённые входы всех мультиплексоров,

но на выход устройства пройдёт сигнал

лишь с одного из них. Этот вход будет

связан с мультиплексором, выход которого

находится а активном состоянии, т.е. на

его входе

выбираются

одноимённые входы всех мультиплексоров,

но на выход устройства пройдёт сигнал

лишь с одного из них. Этот вход будет

связан с мультиплексором, выход которого

находится а активном состоянии, т.е. на

его входе![]() присутствует логический нуль.

Многоразрядные мультиплексоры такого

типа обладают меньшими задержками

распространения информационных сигналов

по сравнению с другими структурами.

присутствует логический нуль.

Многоразрядные мультиплексоры такого

типа обладают меньшими задержками

распространения информационных сигналов

по сравнению с другими структурами.

Рис. 1.4

К

10

счетчика на единицу. При этом осуществляется выбор следующей ячейки ОЗУ (с адресом А0+1). Информация, содержащаяся в ней, появляется на выходах ОЗУ, но не на шине данных.

Указатель стека, как и в предыдущем случае, индицирует адрес ячейки, из которой будет производиться считывание информации в следующем цикле. При дальнейшем поступлении импульсов управления, информация на шине данных появляется в том же порядке, как и заносилась. Таким образом, запоминающее устройство работает в этом случае как стек типа FIFO.

В случае, когда после перехода к считыванию установка начального адреса не производится, но счетчик переведен в режим вычитания, адреса выбираемых ячеек будут последовательно уменьшаться (начиная с А0+2 как показано в нижней таблице на рис. 9.4). В результате данные на выходе моделируемого стека будут появляться в порядке, обратном порядку их записи, то есть стек будет работать в режиме LIFO.

Из принципа работы моделируемого стека следует, что никаких ограничений на количество циклов считывания информации из одной ячейки не налагается, то есть считывание данных происходит без их разрушения. Кроме того глубина стека зависит лишь от емкости используемого ОЗУ и разрядности счетчика и может быть сделана сколь угодно большой.

При разработке стеков на реальных цифровых устройствах необходимо учитывать особенности их функционирования, отражаемые обычно в таблицах истинности. В данной лабораторной работе необходимо спроектировать и исследовать стек с объемом памяти 16 восьмиразрядных ячеек, используя блоки ОЗУ емкостью 16×4. Для этого дополнительно потребуется четырехразрядный счетчик адреса и восьмиразрядный буферный регистр. Обозначения и таблицы функционирования данных узлов приведены на рис. 9.5.

Оперативное запоминающее устройство емкостью 16×4, обозначаемое на схемах RAM, может работать в режимах записи, считывания и хранения информации. В первых двух режимах

123

|

Режим записи | |||||||

|

|

Исх. сост. |

Цикл 1 такт 1 такт 2 |

Цикл 2 такт 1 такт 2 |

Цикл 3 такт 1 такт2 | |||

|

Адрес |

А0 |

А0 |

А0+1 |

А0+1 |

А0+2 |

А0+2 |

|

|

SP |

А0 |

А0 |

А0+1 |

А0+1 |

А0+2 |

А0+2 |

|

|

Сод. ячеек |

|

D0→А0 |

(А0)=D0 |

D1→А0+1 |

(А0)= D0 (А0+1)= D1 |

D2→А0+2 |

(А0)=D0 (А1)=D1 (А2)=D2 |

|

Режим считывания (стек FIFO) | |||||||

|

|

Исх. сост. |

Цикл 1 такт 1 такт 2 |

Цикл 2 такт 1 такт 2 |

Цикл 3 такт 1 такт2 | |||

|

Адрес |

А0 |

А0 |

А0+1 |

А0+1 |

А0+2 |

А0+2 |

А0+3 |

|

SP |

А0 |

А0 |

А0+1 |

А0+1 |

А0+2 |

А0+2 |

А0+3 |

|

Сод. ячеек |

(А0)=D0 (А0+1)=D1 (А0+2)=D2 |

(А0)=D0 (А0+1)=D1 (А0+2)=D2 |

(А0)=D0 (А0+1)=D1 (А0+2)=D2 |

" " " |

" " " |

" " " |

" " " |

|

Вых. инф. |

_ |

D0 |

D0 |

D1 |

D1 |

D2 |

D2 |

|

Режим считывания (стек LIFO) | |||||||

|

|

Исх. сост. |

Цикл 1 такт 1 такт 2 |

Цикл 2 такт 1 такт 2 |

Цикл 3 такт 1 такт2 | |||

|

Адрес |

А0+2 |

А0+2 |

А0+1 |

А0+1 |

А0 |

А0 |

А0-1 |

|

SP |

А0+2 |

А0+2 |

А0+1 |

А0+1 |

А0 |

А0 |

А0-1 |

|

Сод. ячеек |

(А0)=D0 (А0+1)=D1 (А0+2)=D2 |

(А0)=D0 (А0+1)=D1 (А0+2)=D2 |

" " " |

" " " |

" " " |

" " " |

" " " |

|

Вых. инф. |

_ |

D2 |

D2 |

D1 |

D1 |

D0 |

D0 |

Р

122

|

X2 |

X1 |

X0 |

У |

Входы мультиплексора |

|

0 |

0 |

0 |

0 |

0 |

|

0 |

0 |

1 |

0 |

1 |

|

0 |

1 |

0 |

0 |

2 |

|

0 |

1 |

1 |

0 |

3 |

|

1 |

0 |

0 |

1 |

4 |

|

1 |

0 |

1 |

1 |

5 |

|

1 |

1 |

0 |

1 |

6 |

|

1 |

1 |

1 |

0 |

7 |

|

Рис. 1.5 | ||||

Рис. 1.6

На

рис. 1.5 приведён вариант представления

функции![]() .

Если, как показано на рис. 1.6, сигналы

.

Если, как показано на рис. 1.6, сигналы![]() подать на управляющие входы мультиплексора

8→1, а значения

подать на управляющие входы мультиплексора

8→1, а значения

![]() на

соответствующие информационные, то при

задании номера входа, на выходе

мультиплексора сформируется сигнал,

равный значению функции на данном наборе

переменных. При смене комбинации сигналов

на информационных входах, мультиплексор

будет формировать другую функцию от

тех же логических переменных.

на

соответствующие информационные, то при

задании номера входа, на выходе

мультиплексора сформируется сигнал,

равный значению функции на данном наборе

переменных. При смене комбинации сигналов

на информационных входах, мультиплексор

будет формировать другую функцию от

тех же логических переменных.