- •Псковский политехнический институт

- •Псковский политехнический институт

- •Варианты заданий к лабораторной работе

- •3. Содержание отчета.

- •130 Содержание

- •Порядок проведения лабораторной работы.

- •20__ Год

- •Описание лабораторной установки.

- •Краткие теоретические сведения.

- •Описание лабораторной установки.

- •Варианты заданий к лабораторной работе "Исследование мультиплексора".

- •Краткие теоретические сведения.

- •К раткие теоретические сведения.

- •3. Содержание отчета.

- •Варианты заданий к лабораторной работе "Исследование оперативного запоминающего устройства".

- •Порядок проведения лабораторной работы.

- •Описание лабораторной установки.

- •Описание лабораторной установки.

- •Краткие теоретические сведения.

- •Варианты заданий к лабораторной работе "Исследование синхронного счетчика".

- •Порядок проведения лабораторной работы.

- •3. Содержание отчета.

- •3. Содержание отчёта.

- •Порядок проведения лабораторной работы.

- •Варианты заданий к лабораторной работе "Исследование сумматора".

- •Описание лабораторной установки.

- •Краткие теоретические сведения.

- •Описание лабораторной установки.

- •Порядок проведения лабораторной работы.

- •Краткие теоретические сведения.

- •3. Содержание отчёта.

- •Варианты заданий к лабораторной работе "Исследование счетчика Джонсона"

- •Варианты заданий к лабораторной работе "Исследование матричного умножителя".

- •Краткие теоретические сведения.

- •Порядок проведения лабораторной работы.

- •Описание лабораторной установки.

- •Описание лабораторной установки.

- •Порядок проведения лабораторной работы.

- •Краткие теоретические сведения.

- •Варианты заданий к лабораторной работе "Исследование кольцевого счетчика".

- •3. Содержание отчета.

- •Варианты заданий к лабораторной работе "Исследование алу".

- •Краткие теоретические сведения.

- •Порядок проведения лабораторной работы

- •Описание лабораторной установки.

Описание лабораторной установки.

Установка для проведения лабораторной работы № 8 "Исследование оперативного запоминающего устройства" состоит из лабораторного стенда, внешний вид панели которого приведен на рис. 8.8. Стенд содержит все необходимые элементы для создания модулей ОЗУ емкостью 64×4 или 32×8 и исследования принципов их работы.

С

110

Рис. 2.7.

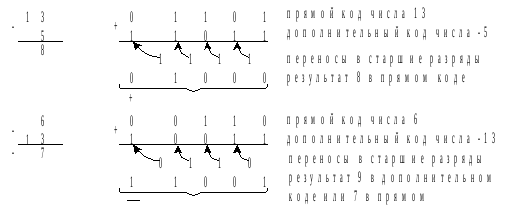

Преобразователь прямого кода вычитаемого В в дополнительный осуществляет инвертирование разрядов двоичного кода числа В и арифметическое прибавление единицы в младший.

Для этого используется вход переноса С0 сумматора D1, на который поступает и уменьшаемое А. Знаковый разряд результата формируется в дополнительном одноразрядном двоичном сумматоре D2.

Рис.

2.8.

Рис.

2.8.

К

23

преобразовании прямого кода в дополнительный. Это объясняется тем, что если число L дополняет К до М, то К соответственно является дополнением L до того же М.

|

|

|

|

0 0 |

0

( |

|

0 1 |

1

( |

|

1 0 |

1

( |

|

1 1 |

0

( |

Схема одного из вариантов соответствующего устройства представлена на рис. 2.9. Здесь элемент D4 "исключающее ИЛИ", называемый иначе "сумматор по модулю два", используется в качестве управляемого инвертора. Его таблица истинности выглядит следующим образом.

Рис. 2.9

Если сигнал в знаковом разряде (на выходе сумматора D2) равен нулю, то результат вычитания на выходах D1 положительный, представлен в прямом коде и ни инвертирования, ни прибавления единицы к его младшему разряду не требуется и не происходит. Соответственно сигналы на выходе устройства (сумматор D5) будут тождественны сигналам на выходах сумматора D1. Если же в знаковом разряде появляется единица (результат на выходе первого сумматора отрицательный и представлен в

24

109

Тогда

в режиме чтения, при подаче на адресные

входы ЗУ комбинаций переменных

![]() -

-![]() ,

на выходе будет получена искомая функция.

,

на выходе будет получена искомая функция.

Так как информацию в ОЗУ можно произвольно изменять, то соответственно можно менять и вид формируемой логической функции. Это позволяет использовать ОЗУ в качестве универсального логического элемента.

|

Двоичный код |

Н-код |

Символы индикатора |

|

0 0 0 0 |

0 |

|

|

0 0 0 1 |

1 |

|

|

0 0 1 0 |

2 |

|

|

0 0 1 1 |

3 |

|

|

0 1 0 0 |

4 |

|

|

0 1 0 1 |

5 |

|

|

0 1 1 0 |

6 |

|

|

0 1 1 1 |

7 |

|

|

1 0 0 0 |

8 |

|

|

1 0 0 1 |

9 |

|

|

1 0 1 0 |

A |

|

|

1 0 1 1 |

B |

|

|

1 1 0 0 |

C |

|

|

1 1 0 1 |

D |

|

|

1 1 1 0 |

E |

|

|

1 1 1 1 |

F |

|

|

Рис. 8.5 | ||

Такой индикатор содержит обычно семь элементов (восьмым является точка), которые могут засвечиваться независимо друг от друга. При этом формируются символические изображения цифр и знаков, как показано на рис. 8.5.

В настоящее время очень широкое распространение получили светодиодные индикаторы, благодаря удобству стыковки с низковольтными цифровыми микросхемами. Сегменты в таких индикаторах маркируются обычно латинскими буквами как показано на рис. 8.6, а светодиоды могут включаться по схеме с общим анодом (ОА), либо с общим катодом (ОК). В зависимости от структуры индикатора, значения управляющих сигналов

нии питающих напряжений, так как после включения питания ячейки накопителя устанавливаются в произвольные состояния.

Рис. 8.4

Основное

назначение запоминающих устройств -

хранение массивов информации. Однако

они могут использоваться и для других

целей, в частности для формирования

логических функций. Как известно, для

n

логических переменных существует

![]() функций, каждая из которых принимает

функций, каждая из которых принимает![]() значений.

значений.

|

|

0 |

1 |

0 |

1 |

0 |

1 |

0 |

1 |

|

|

0 |

0 |

1 |

1 |

0 |

0 |

1 |

1 |

|

|

0 |

0 |

0 |

0 |

1 |

1 |

1 |

1 |

|

У |

0 |

0 |

0 |

1 |

1 |

0 |

1 |

1 |

дополнительном коде), то она поступает на вход переноса оконечного сумматора и приводит к переключению схем «исключающее ИЛИ» в режим инверсии. В итоге дополнительный код первого сумматора будет преобразован в прямой.

Для анализа входные и выходные данные различных арифметических узлов удобно отображать с помощью семисегментных индикаторов. Он позволяет сформировать все символы шестнадцатеричного кода путём засветки определенных комбинаций сегментов. Для трансформации значений тетрад двоичного кода в коды управления сегментами необходимо использование специальных преобразователей кодов.

В ряде случаев возникает необходимость суммирования чисел представленных в двоично-десятичном коде. Для этой цели можно использовать сумматоры двоичных чисел, введя специальные узлы коррекции результата. Так как тетрада двоично-десятичного кода ничем не отличается от аналогичной тетрады двоичного, то и все арифметические действия с этими кодами должны выполняться по одним и тем же законам.

Однако, если сумма двух чисел получается больше 9, то при работе с двоично-десятичным кодом должен сформироваться перенос в следующую тетраду, а при работе с двоичным такой перенос возникает лишь если результат > 15. Таким образом, для создания двоично-десятичного сумматора на основе двоичных, необходимо специальное устройство, формирующее сигнал переноса, если сумма больше 9. Но, кроме этого, при возникновении переноса потребуется ещё и коррекция результата, так как тетрады двоично-десятичного кода для чисел больших, чем 9 просто не существует.

П

108

25

Таким образом, для получения правильного результата при сложении двоично-десятичных кодов чисел в двоичных сумматорах, необходимо в случае получения суммы большей девяти сформировать перенос в следующую тетраду и скорректировать результат путём вычитания числа десять из выходного кода двоичного сумматора. Аналогичная операция должна производиться и при появлении переноса в двоичном сумматоре.

Так

как вычитание можно заменить сложением

с дополнительным кодом вычитаемого, то

в устройство для суммирования

двоично-десятичных чисел необходимо

ввести ещё один сумматор, на входы

которого должен поступать результат с

выходов двоичного сумматора и, либо

число

![]() ,

если данный результат<

9, либо

,

если данный результат<

9, либо

![]() в противном случае, так как

в противном случае, так как![]() является, дополнительным кодом

является, дополнительным кодом![]() .

.

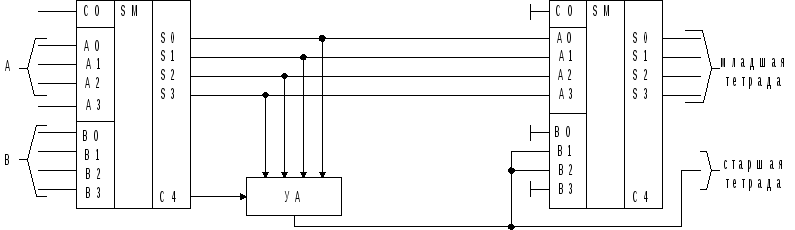

Структура сумматора двоично-десятичных чисел и таблица его функционирования приведены, на рис. 2.10, рис. 2.11. Устройство анализа УА формирует единичный сигнал при необходимости коррекции результата и может быть построено на стандартных логических элементах.

Р ис.

2.10

ис.

2.10

|

а в |

0 |

1 |

2 |

3 |

4 |

5 |

6 |

7 |

8 |

9 |

|

0 |

0 |

1 |

2 |

3 |

4 |

5 |

6 |

7 |

8 |

9 |

|

1 |

1 |

2 |

3 |

4 |

5 |

6 |

7 |

8 |

9 |

10 |

|

2 |

2 |

3 |

4 |

5 |

6 |

7 |

8 |

9 |

10 |

11 |

|

3 |

3 |

4 |

5 |

6 |

7 |

8 |

9 |

10 |

11 |

12 |

|

4 |

4 |

5 |

6 |

7 |

8 |

9 |

10 |

11 |

12 |

13 |

|

26

|

5 |

6 |

7 |

8 |

9 |

10 |

11 |

12 |

13 |

14 |

Рис. 8.2

![]() ,

как показано на рис. 8.3. Для нормальной

работы модуля емкостью 8х2, сигнал решения

,

как показано на рис. 8.3. Для нормальной

работы модуля емкостью 8х2, сигнал решения![]() должен подаваться на соответствующий

вход только одного из ОЗУ, выходы которого

при этом будут переведены в активное

состояние. Выходы других ОЗУ в данной

ситуации отключены, а сами они находятся

в режиме хранения. Адресация запоминающих

ячеек такого модуля отличается от

естественной, так как требуется

двухразрядный сигнал адреса и два

сигнала

должен подаваться на соответствующий

вход только одного из ОЗУ, выходы которого

при этом будут переведены в активное

состояние. Выходы других ОЗУ в данной

ситуации отключены, а сами они находятся

в режиме хранения. Адресация запоминающих

ячеек такого модуля отличается от

естественной, так как требуется

двухразрядный сигнал адреса и два

сигнала![]() .

.

В

Рис.

8.3

![]()

Используя описанные выше способы, можно одновременно наращивать и разрядность, и количество запоминающих ячеек ОЗУ.

О

107

Все ячейки накопителя дополнительно связаны между собой едиными шинами данных и управления, посредством которых обеспечивается ввод и вывод информации, а также реализация режимов записи, считывания или хранения.

Выходные

каскады ОЗУ строятся обычно по схеме с

открытым коллектором, либо с тремя

состояниями. Это позволяет специальным

сигналом

![]() (chip

select

- выборка кристалла) как бы отключить

выходы ОЗУ от остальных узлов, что

обеспечивает возможность наращивания

информационной емкости запоминающих

устройств путем их параллельного

соединения.

(chip

select

- выборка кристалла) как бы отключить

выходы ОЗУ от остальных узлов, что

обеспечивает возможность наращивания

информационной емкости запоминающих

устройств путем их параллельного

соединения.

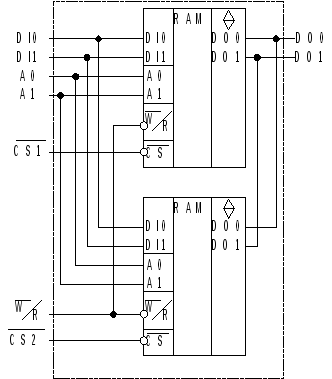

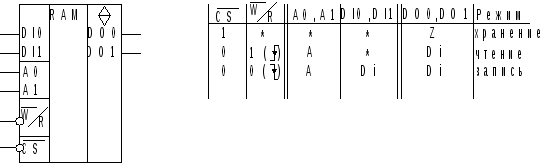

На рис. 8.1 приведено обозначение на принципиальных схемах типового ОЗУ емкостью 4х2 с тремя состояниями выходов. Там же представлена таблица режимов его работы. Звездочками отмечены произвольные уровни сигналов, символом Z - состояние высокого выходного импеданса.

Рис. 8.1

Увеличение информационной емкости ОЗУ может производиться как за счет наращивания разрядности групп запоминающих ячеек накопителя, так и за счет увеличения их количества (глубины адресного пространства). В первом случае у нужного числа идентичных ОЗУ объединяются входы управления, как это показано для ОЗУ емкостью 4×4 на рис. 8.2. При этом все ОЗУ работают параллельно в одних и тех же режимах.

106

|

в |

0 |

1 |

2 |

3 |

4 |

5 |

6 |

7 |

8 |

9 |

|

6 |

6 |

7 |

8 |

9 |

10 |

11 |

12 |

13 |

14 |

15 |

|

7 |

7 |

8 |

9 |

10 |

11 |

12 |

13 |

14 |

15 |

16 |

|

8 |

8 |

9 |

10 |

11 |

12 |

13 |

14 |

15 |

16 |

17 |

|

9 |

9 |

13 |

11 |

12 |

13 |

14 |

15 |

16 |

17 |

18 |

Рис. 2.11

а

а