- •Псковский политехнический институт

- •Псковский политехнический институт

- •Варианты заданий к лабораторной работе

- •3. Содержание отчета.

- •130 Содержание

- •Порядок проведения лабораторной работы.

- •20__ Год

- •Описание лабораторной установки.

- •Краткие теоретические сведения.

- •Описание лабораторной установки.

- •Варианты заданий к лабораторной работе "Исследование мультиплексора".

- •Краткие теоретические сведения.

- •К раткие теоретические сведения.

- •3. Содержание отчета.

- •Варианты заданий к лабораторной работе "Исследование оперативного запоминающего устройства".

- •Порядок проведения лабораторной работы.

- •Описание лабораторной установки.

- •Описание лабораторной установки.

- •Краткие теоретические сведения.

- •Варианты заданий к лабораторной работе "Исследование синхронного счетчика".

- •Порядок проведения лабораторной работы.

- •3. Содержание отчета.

- •3. Содержание отчёта.

- •Порядок проведения лабораторной работы.

- •Варианты заданий к лабораторной работе "Исследование сумматора".

- •Описание лабораторной установки.

- •Краткие теоретические сведения.

- •Описание лабораторной установки.

- •Порядок проведения лабораторной работы.

- •Краткие теоретические сведения.

- •3. Содержание отчёта.

- •Варианты заданий к лабораторной работе "Исследование счетчика Джонсона"

- •Варианты заданий к лабораторной работе "Исследование матричного умножителя".

- •Краткие теоретические сведения.

- •Порядок проведения лабораторной работы.

- •Описание лабораторной установки.

- •Описание лабораторной установки.

- •Порядок проведения лабораторной работы.

- •Краткие теоретические сведения.

- •Варианты заданий к лабораторной работе "Исследование кольцевого счетчика".

- •3. Содержание отчета.

- •Варианты заданий к лабораторной работе "Исследование алу".

- •Краткие теоретические сведения.

- •Порядок проведения лабораторной работы

- •Описание лабораторной установки.

Порядок проведения лабораторной работы.

1. Домашняя подготовка.

а) В ходе домашней подготовки к лабораторной работе необходимо разработать принципиальную схему пятиразрядного счетчика Джонсона на D-триггерах с учетом элементной базы лабораторного стенда и представить временные диаграммы его функционирования;

в) спроектировать схему, обеспечивающую самовосстановление работоспособности счетчика после сбоев, проанализировать процесс смены его состояний приняв в качестве исходной ситуацию, указанную в соответствующем варианте задания, при наличии схемы самовосстановления и без нее. Результаты анализа должны быть представлены в виде таблиц функционирования и временных диаграмм;

г) разработать с использованием элементов, входящих в состав лабораторного стенда принципиальную схему преобразователя кода Джонсона в двоичный код.

Все перечисленные расчеты должны быть оформлены в виде предварительного отчета и представлены преподавателю перед началом лабораторной работы.

2. Проведение лабораторной работы.

85

84

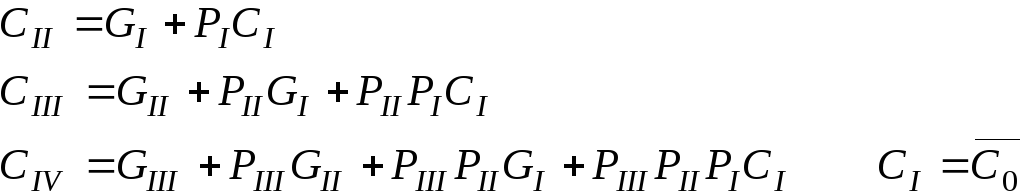

АЛУ формируются два дополнительных сигнала Р и G, называемые сигналами распространения и генерации переноса.

В режимах сложения и вычитания они синтезируются непосредственно из входных переменных АЛУ по алгоритмам:

и

связаны с

![]() следующим

образом:

следующим

образом:![]()

В свою очередь переносы в АЛУ, обрабатывающие группы разрядов операндов, связаны с функциями Р и G соотношениями:

Римскими

цифрами здесь обозначены номера АЛУ,

![]() -

входной перенос в самый младший разряд.

-

входной перенос в самый младший разряд.

Таким

образом, если сигналы Р и G

с выходов нескольких АЛУ обработать по

вышеприведенному алгоритму, то переносы

во все АЛУ будут формироваться практически

одновременно с поступлением операндов

и задержка выполнения операции

суммирования не превысит величины

![]() при любом числе АЛУ. Здесь

при любом числе АЛУ. Здесь![]() - время формирования сигналов

распространения и генерации переноса,

- время формирования сигналов

распространения и генерации переноса,![]() -

время их обработки.

-

время их обработки.

Устройства обработки сигналов Р и G выпускаются в виде отдельных функционально законченных узлов и называются схемами ускоренного переноса. Принцип их подключения к АЛУ показан на рис. 4.4.

49

Рис. 4.4

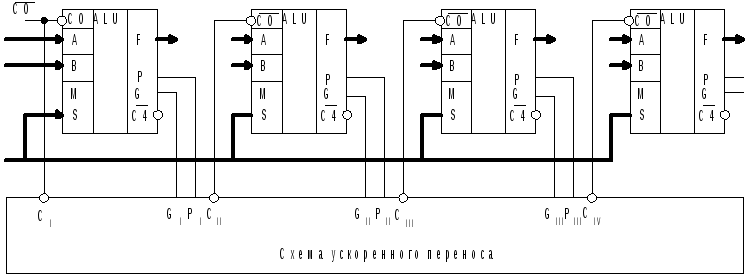

Выполнение

операций над входными данными в АЛУ

имеет ряд особенностей. Логические

операции реализуются поразрядно, то

есть над одноименными разрядами операндов

без всякой их взаимосвязи друг с другом.

Так, например, если выбрана операция

![]() и заданы операнды А=0110, В=0100, то результатом

будет число F=1001. Арифметические операции

в АЛУ выполняются над всеми разрядами

одновременно с учётом переносов из

младших разрядов в старшие и состояния

входа переноса

и заданы операнды А=0110, В=0100, то результатом

будет число F=1001. Арифметические операции

в АЛУ выполняются над всеми разрядами

одновременно с учётом переносов из

младших разрядов в старшие и состояния

входа переноса![]() .

Например, при тех же операндax

A=0110,

В=0100,

.

Например, при тех же операндax

A=0110,

В=0100,

![]() =1

и F=A+В,

результат будет равен 1010. Если результат

арифметической операции положителен,

то он формируется в прямом коде с

инверсным значением выходного переноса.

Если же результат отрицательный, то он

формируется в дополнительном коде.

Примеры выполнения описанных операций

приведены на рис. 4.5.

=1

и F=A+В,

результат будет равен 1010. Если результат

арифметической операции положителен,

то он формируется в прямом коде с

инверсным значением выходного переноса.

Если же результат отрицательный, то он

формируется в дополнительном коде.

Примеры выполнения описанных операций

приведены на рис. 4.5.

Рис. 4.5

50

83

Рис. 6.14

Описание лабораторной установки.

Установка для проведения лабораторной работы № 7 "Исследование счетчика Джонсона" состоит из лабораторного стенда, цифрового коммутатора и осциллографа. Внешний вид передней панели стенда приведен на рис. 6.15 , а коммутатора на рис. 6.16 . Стенд содержит все необходимые элементы для сборки и исследования работы счетчика Джонсона с разрядностью от 2 до 5, реализации схемы устранения сбоев и преобразователя кода Джонсона в двоичный код.

Сборка счетчика Джонсона и вспомогательных схем производится путем соединения требуемых сигнальных гнезд проводниками со стандартными штеккерами. Для реализации разветвленных связей имеются специальные соединители с увеличенным количеством штеккеров.

Цифровой коммутатор используется для одновременного наблюдения на экране осциллографа до восьми цифровых сигналов. Стенд коммутатора содержит также ряд дополнительных элементов, используемых для расширения функциональных возможностей лабораторной установки.

82

Дополнительный

код двоичного числа образуется путём

инвертирования значений всех его

разрядов и арифметического прибавления

единицы к младшему разряду полученного

числа. Например, прямой двоичный код

десятичнoгo

числа 13 равен 1101. Дополнительный код

этого же числа находится следующим

образом 1101![]() 0010

0010![]() 0010+1

0010+1![]() 0011.

Это число 3 в десятичном коде.

0011.

Это число 3 в десятичном коде.

Для

преобразования дополнительного кода

числа в прямой необходимо провести ту

же цепочку операций 0011![]() 1100

1100![]() 1100+1

1100+1![]() 1101.

Таким образом, если выбрана функцияF=A-B,

то при значениях операндов А=0010 и В=0101

результат будет равен 1101. Так как А<В,

то он представлен в дополнительном

коде. Прямой код результата 0011. В

десятичной системе А=2, В=5, F=

-3. Таким образом, прямой код равен модулю

результата.

1101.

Таким образом, если выбрана функцияF=A-B,

то при значениях операндов А=0010 и В=0101

результат будет равен 1101. Так как А<В,

то он представлен в дополнительном

коде. Прямой код результата 0011. В

десятичной системе А=2, В=5, F=

-3. Таким образом, прямой код равен модулю

результата.

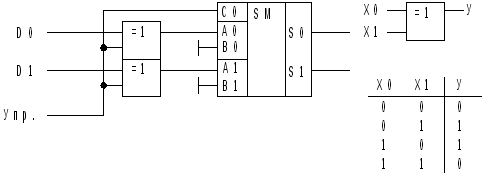

Устройство для преобразования прямого кода в дополнительный и обратно может быть выполнено на основе сумматора и управляемого инвертора. В качестве последнего удобно использовать схему "исключающее ИЛИ", которая иначе называется сумматором по модулю два. Её таблица истинности приведена на рис. 4.6, там же представлена и схема преобразователя.

Рис. 4.6

Е

51

произойдёт инвертирование всех разрядов операнда и прибавление единицы через разряд переноса. Выходной код сумматора в этом случае будет равен дополнительному коду операнда.

Арифметико-логические

(смешанные) операции выполняются в АЛУ

в два этапа. Сначала поразрядно реализуется

логическая операция, а затем с учетом

переносов между разрядами - арифметическая.

Например, операция

![]() при А=0110, В=0100 выполняется следующим

образом. На первом этапе формируются

функции

при А=0110, В=0100 выполняется следующим

образом. На первом этапе формируются

функции![]() и

и![]() ,

затем производится арифметическое

сложение получившихся кодовых комбинаций,

представляемых уже как двоичные коды

чисел, и формируется результатF=0101

и сигнал переноса

,

затем производится арифметическое

сложение получившихся кодовых комбинаций,

представляемых уже как двоичные коды

чисел, и формируется результатF=0101

и сигнал переноса

![]() .

.

Использование АЛУ позволяет строить универсальные блоки обработки цифровой информации, выполняющие по определенным программам практически любые операции над совокупностью входных данных. Однако, в ряде случаев, когда требуется реализовать лишь некоторые конкретные действия, например, перемножение чисел, возведение в степень, интегрирование более целесообразным, с точки зрения быстродействия, является использование не универсальных, а специализированных устройств.

В цифровых системах автоматического управления одной из основных операций над входными данными является интегрирование, которое можно свести к последовательному суммированию поступающих по одному каналу операндов.

Р

52

значение функции D. В следующую строчку записываются состояния счетчика после прихода очередного тактирующего импульса (они получаются путем сдвига вправо на один разряд предыдущих кодовых комбинаций). Вычисления продолжаются до появления рабочей комбинации сигналов на выходах счетчика (рис. 6.12), либо одной из ранее наблюдавшихся сбойных. Последнее будет говорить о некорректной работе схемы восстановления.

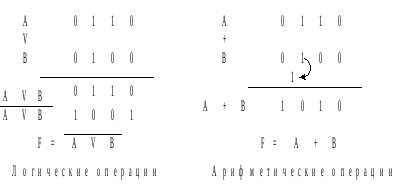

В

ряде случаев информацию о состояниях

счетчика Джонсона требуется представлять

в двоичном коде, как показано в правой

части таблицы на рис. 6.2. Это можно сделать

подключив к выходам счетчика специальный

преобразователь кодов. Синтез такого

устройства осуществляется обычными

способами, в частности с использованием

карт Карно, которые приведены на рис.

6.13 для определения функций

![]() из таблицы (рис. 6.2 ).

из таблицы (рис. 6.2 ).

Рис. 6.13

На рис. 6.14 показана структура преобразователя кодов , реализующая получаемые из карт соотношения:

81

помехоустойчивой системы необходимо объединить состояния, соответствующие единичным значениям D всеми возможными способами. В итоге выражение для искомой функции будет иметь вид:

![]()

Аналогичное

соотношение справедливо и в общем случае

для n-разрядного счетчика Джонсона -

![]() .

Для устранения инверсий переменных

полученное выражение можно преобразовать

к следующей форме:

.

Для устранения инверсий переменных

полученное выражение можно преобразовать

к следующей форме:![]()

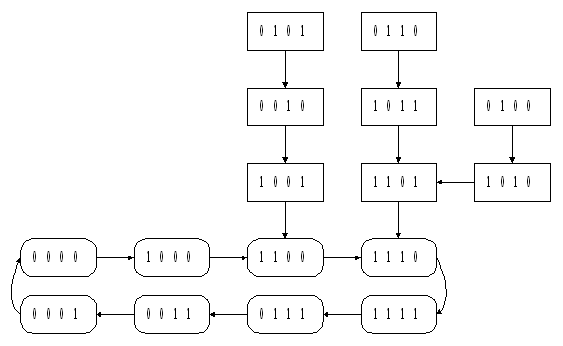

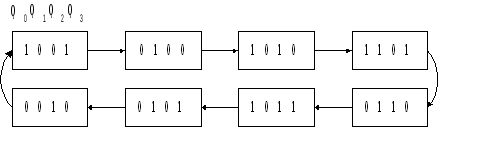

В итоге схема четырехразрядного счетчика Джонсона с самовосстановлением после сбоев будет иметь структуру, показанную на рис. 6.10. Из графа переходов такого счетчика, приведенного на рис. 6.11 видно, что возвращение в рабочее состояние после любого сбоя происходит максимум через три такта входного синхронизирующего сигнала.

Рис. 6.10

Рис. 6.12

Анализ

процесса самовосстановления счетчика

Джонсона удобно производить следующим

образом. В строчку выписываются символы,

обозначающие вход D

и выходы

![]() Под символами

Под символами

![]() заносятся значения уровней сигналов,

соответствующие текущему состоянию

счетчика и вычисляется

заносятся значения уровней сигналов,

соответствующие текущему состоянию

счетчика и вычисляется

80

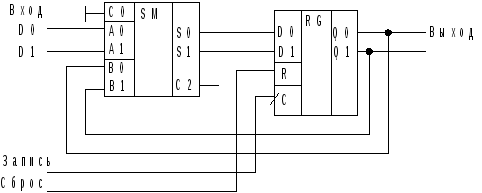

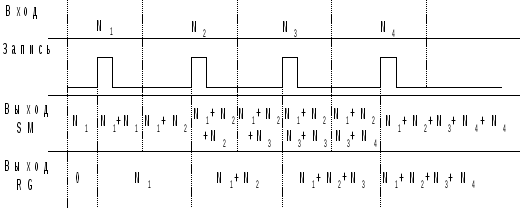

Устройство, реализующее операцию цифрового интегрирования называется накапливающим сумматором и может быть построено на основе обычного сумматора (или АЛУ в соответствующем режиме) и регистра памяти. На рис. 4.7 приведена принципиальная схема двухразрядного накапливающего сумматора, а на рис. 4.8 временные диаграммы его работы.

Рис. 4.8

Пусть

в исходном состоянии регистр RG обнулён,

а на вход сумматора поступает число N1.

При этом результат на выходе сумматора

SM также будет равен N1,

но число на выходах накапливающего

сумматора будет равно нулю. С приходом

импульса записи число N1

запишется

в регистр, на выходе сумматора SM

при этом сформируется число

![]() .

При подаче на вход накапливающего

сумматора числа

.

При подаче на вход накапливающего

сумматора числа![]() ,

результат SM станет равным

,

результат SM станет равным![]() и последующим импульсом записи он

зафиксируется в регистре, появившись

при этом и на выходе самого накапливающего

сумматора.

и последующим импульсом записи он

зафиксируется в регистре, появившись

при этом и на выходе самого накапливающего

сумматора.

Таким образом, при поступлении в определенной последовательности совокупности чисел, N1, N2, N3,… и импульсов записи, будет происходить формирование текущей суммы вида S=. N1,+N2,+N3…., т.е. накопление результата суммирования. На временных диаграммах (рис. 4.8) показано, как при этом изменяются состояния выходов сумматора и регистра.

О

53![]() ,

гдеn –

разрядность сумматора SM. Это обстоятельство

следует учитывать при анализе работы

накапливающих сумматоров.

,

гдеn –

разрядность сумматора SM. Это обстоятельство

следует учитывать при анализе работы

накапливающих сумматоров.

|

Десятичное число |

Двоичный код |

Шестнадцатеричный код |

|

0 |

0 0 0 0 |

0 |

|

1 |

0 0 0 1 |

1 |

|

2 |

0 0 1 0 |

2 |

|

3 |

0 0 1 1 |

3 |

|

4 |

0 1 0 0 |

4 |

|

5 |

0 1 0 1 |

5 |

|

6 |

0 1 1 0 |

6 |

|

7 |

0 1 1 1 |

7 |

|

8 |

1 0 0 0 |

8 |

|

9 |

1 0 0 1 |

9 |

|

10 |

1 0 1 0 |

A |

|

11 |

1 0 1 1 |

B |

|

12 |

1 1 0 0 |

C |

|

13 |

1 1 0 1 |

D |

|

14 |

1 1 1 0 |

E |

|

15 |

1 1 1 1 |

F |

|

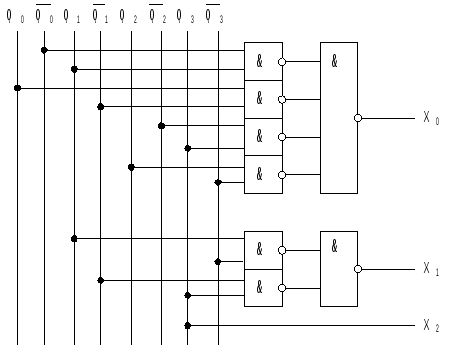

Рис. 4.9 | ||

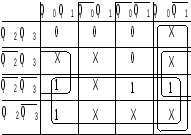

Рис. 6.9

онтроль функционирования различных арифметических устройств можно осуществлять анализируя совокупности логических сигналов на их входax и выходах. Однако в ряде случаев, бывает удобнее преобразовать двоичный код операндов и результата в шестнадцатеричный. Для этого двоичное число делится, начиная справа на группы по четыре разряда - тетрады, каждой из которых ставится в соответствие свой символ шестнадцатеричного кода, как это показано на рис. 4.9. В свою очередь символы шестнадцатеричного кода могут быть отображены посредством сегментных цифровых индикаторов, для обеспечения функционирования которых необходимы специальные преобразователи кодов, серийно пускаемые промышленностью.

54

ненужных при работе комбинаций. Эта ситуация называется сбоем. В ряде случаев, через определенное количество входных импульсов, сбой счетчика может самопроизвольно устраниться, но в некоторых ситуациях этого не происходит и счетчик начинает работать неправильно.

Рис. 6.8

Эта возможность отражена на графе переходов четырехразрядного счетчика Джонсона (рис. 6.8), триггера которого первоначально ,были установлены в состояния 1001. Поэтому для устранения сбоев в реальных схемах используют специальные внешние устройства.

Принцип

работы одного из вариантов таких

устройств заключается в следующем. Из

таблицы состояний счетчика приведенной

на рис. 6.2 следует, что сигнал на входе

данных D

должен принимать единичное значение

только при строго определенных комбинациях

выходных сигналов счетчика

![]() .

Будем считать, что состояние входаD

является некоторой функцией переменных

.

Будем считать, что состояние входаD

является некоторой функцией переменных

![]() и определим ее структуру. Для этой цели

можно воспользоваться картой Карно,

приведённой на рис. 6.9. Так как функцияD

определена не на всех наборах переменных

и определим ее структуру. Для этой цели

можно воспользоваться картой Карно,

приведённой на рис. 6.9. Так как функцияD

определена не на всех наборах переменных

![]() ,

то соответствующие клетки карты помечены

крестиками.

,

то соответствующие клетки карты помечены

крестиками.

Э

79

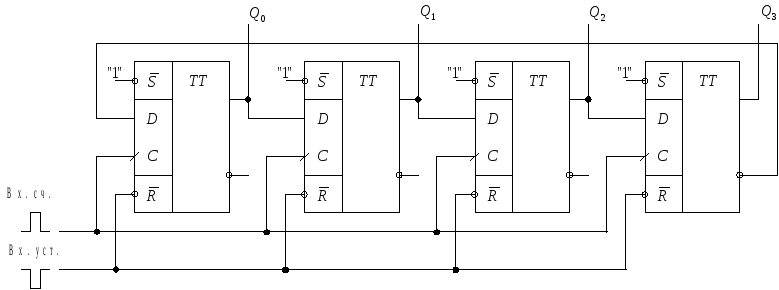

Если на входах установки присутствуют сигналы логической единицы, то по положительному фронту импульса синхронизации на входе С происходит запись в триггер и появление на его выходе Q информации со входа данных D.

Принципиальная

схема четырехразрядного счетчика

Джонсона на D

триггерах приведена на рис. 6.6. Для

предварительной установки всех триггеров

в исходное нулевое состояние их входы

![]() объединяются и перед началом работы

счетчика на вход "Уст." однократно

подается кратковременный сигнал

логического нуля.

объединяются и перед началом работы

счетчика на вход "Уст." однократно

подается кратковременный сигнал

логического нуля.

Рис. 6.6

Известно, что последовательностная схема из четырех триггеров может иметь 16 различных состояний, из которых в счетчике Джонсона используются лишь восемь, как показано на рис. 6.7.

Рис. 6.7

Под воздействием помех или по иным причинам триггера счетчика Джонсона могут перейти в одну из неправильных,

78