- •Псковский политехнический институт

- •Псковский политехнический институт

- •Варианты заданий к лабораторной работе

- •3. Содержание отчета.

- •130 Содержание

- •Порядок проведения лабораторной работы.

- •20__ Год

- •Описание лабораторной установки.

- •Краткие теоретические сведения.

- •Описание лабораторной установки.

- •Варианты заданий к лабораторной работе "Исследование мультиплексора".

- •Краткие теоретические сведения.

- •К раткие теоретические сведения.

- •3. Содержание отчета.

- •Варианты заданий к лабораторной работе "Исследование оперативного запоминающего устройства".

- •Порядок проведения лабораторной работы.

- •Описание лабораторной установки.

- •Описание лабораторной установки.

- •Краткие теоретические сведения.

- •Варианты заданий к лабораторной работе "Исследование синхронного счетчика".

- •Порядок проведения лабораторной работы.

- •3. Содержание отчета.

- •3. Содержание отчёта.

- •Порядок проведения лабораторной работы.

- •Варианты заданий к лабораторной работе "Исследование сумматора".

- •Описание лабораторной установки.

- •Краткие теоретические сведения.

- •Описание лабораторной установки.

- •Порядок проведения лабораторной работы.

- •Краткие теоретические сведения.

- •3. Содержание отчёта.

- •Варианты заданий к лабораторной работе "Исследование счетчика Джонсона"

- •Варианты заданий к лабораторной работе "Исследование матричного умножителя".

- •Краткие теоретические сведения.

- •Порядок проведения лабораторной работы.

- •Описание лабораторной установки.

- •Описание лабораторной установки.

- •Порядок проведения лабораторной работы.

- •Краткие теоретические сведения.

- •Варианты заданий к лабораторной работе "Исследование кольцевого счетчика".

- •3. Содержание отчета.

- •Варианты заданий к лабораторной работе "Исследование алу".

- •Краткие теоретические сведения.

- •Порядок проведения лабораторной работы

- •Описание лабораторной установки.

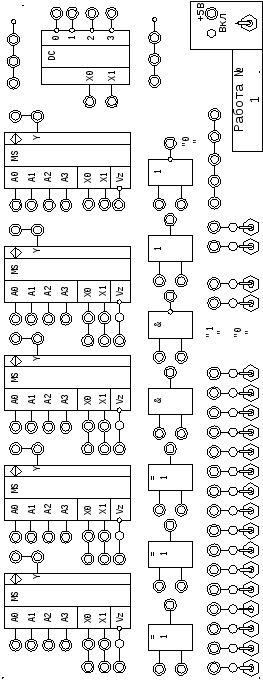

Описание лабораторной установки.

У

11![]() 1

и исследования принципов их работы.

Кроме этого в составе стенда имеются

логические элементы для реализации

требуемых в варианте задания логических

функций.

1

и исследования принципов их работы.

Кроме этого в составе стенда имеются

логические элементы для реализации

требуемых в варианте задания логических

функций.

|

12

|

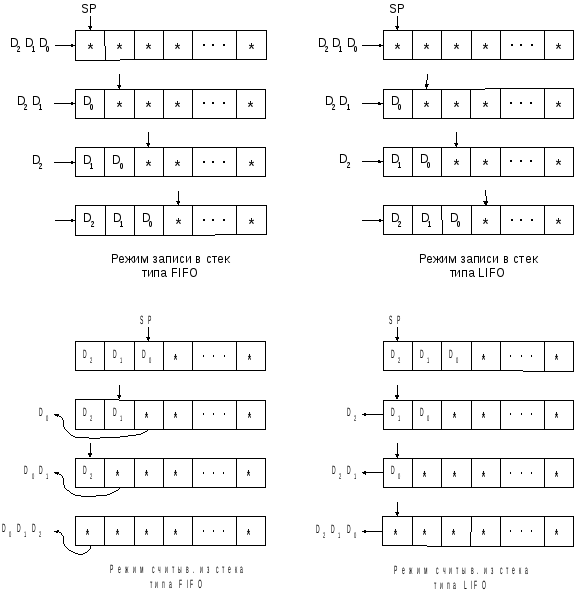

При записи информации в стек устройство управления УУ переводит счетчик в режим суммирования, ОЗУ в режим записи, а выходной регистр RG в режим, при котором его выходы находятся в состоянии высокого импеданса (Z или третье состояние). В этом случае шина данных работает на прием входной информации.

Процедура записи информации в такой стек (цикл записи) состоит из двух тактов, соответствующих приходам отрицательного и положительного фронтов импульсов управления как показано на рис. 9.3 и в таблице на рис.9.4.

При поступлении отрицательного фронта происходит запись входной информации D0 в ячейку с адресом A0. В момент прихода положительного перепада тактирующего сигнала, ОЗУ переводится в режим считывания и к содержимому счетчика А0 прибавляется единица. При этом происходит выбор ячейки ОЗУ с адресом А0+1 и это же значение адреса появляется на выходе указателя стека. Выходы регистра в режиме записи информации в стек поддерживаются в состоянии высокого импеданса и информация с ОЗУ на шину данных не поступает.

В

следующем цикле соответствующим уровнем

сигнала

![]() производится запись текущих данных в

ячейку ОЗУ с адресомA0+1

и так далее. Обозначение (A0)

на рис. 9.4

соответствует содержимому ячейки ОЗУ

с адресом А0.

производится запись текущих данных в

ячейку ОЗУ с адресомA0+1

и так далее. Обозначение (A0)

на рис. 9.4

соответствует содержимому ячейки ОЗУ

с адресом А0.

В

зависимости от режима считывания, схема,

изображенная на рис. 9.3 может работать

как стек FIFO либо как стек LIFO. В первом

случае необходимо вновь произвести

установку начального адреса А0,

сигналом

![]() (рис. 9.3) перевести ОЗУ в режим считывания,

выходы регистра RG сигналом Vz - в активное

состояние. Шина данных при этом начинает

работать на передачу информации, режим

работы счетчика СТ2 (сложение) сохраняется.

(рис. 9.3) перевести ОЗУ в режим считывания,

выходы регистра RG сигналом Vz - в активное

состояние. Шина данных при этом начинает

работать на передачу информации, режим

работы счетчика СТ2 (сложение) сохраняется.

П

121

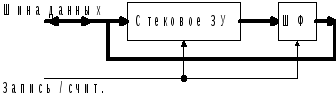

моделируемого стека и временные диаграммы его работы приведены на рис. 9.3.

Рис. 9.3

Приняты следующие обозначения RAM - оперативноe запоминающее устройство, СТ2 - двоичный счетчик, RG - регистр памяти, УУ - устройство управления, SР - указатель стека.

Такое

устройство функционирует следующим

образом. Перед началом работы в счетчик

СТ по сигналу, поступающему на вход V

заносится начальный адрес обращения

к ОЗУ -

![]() .

Указатель стека, связанный с выходами

счетчика, позволяет в том или ином виде

отобразить номер ячейки ОЗУ, к которой

будет происходить обращение в данном

цикле работы.

.

Указатель стека, связанный с выходами

счетчика, позволяет в том или ином виде

отобразить номер ячейки ОЗУ, к которой

будет происходить обращение в данном

цикле работы.

120

Сборка макета мультиплексора производится путём организации связей между сигнальными гнёздами, соединенными с выводами цифровых логических элементов и узлов, входящих в состав лабораторного стенда. Для реализации простых связей используются проводники с одиночными стандартными штеккерами. В случае необходимости установления разветвленных соединений возможно применение проводников с увеличенным количеством штеккеров.

Каждый лабораторный стенд подключается к внешнему источнику питания. Включение стенда производится тумблером "Вкл.". О наличии питающего напряжения свидетельствует свечение зеленого светодиода.

При сборке макета и в ходе работы не разрешается подавать какие-либо сигналы на выходы микросхем, находящиеся в активном состоянии и соединять их друг с другом. Все изменения в схеме должны производиться только при отключенном питании элементов лабораторного стенда.

Порядок проведения лабораторной работы.

1. Домашняя подготовка.

В ходе домашней подготовки необходимо:

а)

разработать на основе мультиплексоров

4![]() 1

принципиальные схемы мультиплексоров

16

1

принципиальные схемы мультиплексоров

16![]() 1

с использованием первого и второго

способа наращивания разрядности;

1

с использованием первого и второго

способа наращивания разрядности;

б)

записать в развёрнутом виде логическую

функцию, описывающую состояние выхода

мультиплексора 16![]() 1;

1;

в) представить в табличной форме логическую функцию из варианта задания, преобразовав её к виду, который может быть реализован на элементах макета;

г) записать состояния входов мультиплексора для формирования данной логической функции;

д) представить в табличной форме логическую функцию, описывающую заданную в соответствующем варианте операцию отношения между двумя двухразрядными числами А и В;

е

13![]() поступает число А, а на

поступает число А, а на![]() - В.

- В.

2. Проведение лабораторной работы.

а)

собрать макет мультиплексора 16![]() 1,

используя первый способ наращивания

разрядности, на входы управления

состоянием выходов мультиплексоров

1,

используя первый способ наращивания

разрядности, на входы управления

состоянием выходов мультиплексоров![]() подать сигнал логического нуля с

соответствующих гнезд;

подать сигнал логического нуля с

соответствующих гнезд;

б)

подключить гнезда, обслуживаемые группой

из шестнадцати тумблеров ко входам

данных мультиплексоров 16![]() 1

(свечение красного светодиода

свидетельствует о наличии в соответствующем

гнезде сигнала логической единицы);

1

(свечение красного светодиода

свидетельствует о наличии в соответствующем

гнезде сигнала логической единицы);

в)

подать сигналы с гнёзд, размещенных

вблизи группы из четырех тумблеров на

входы управления мультиплексора 16![]() 1,

выход мультиплексора соединить с

гнёздами, обслуживающими индикатор

состояния выхода, расположенный в

верхней правой части лицевой панели

лабораторного стенда и обозначенный

"Вх. инд." (при наличии на входе

индикатора сигнала логической единицы

загорается красный светодиод, если

сигнал равен нулю, то свечение отсутствует);

1,

выход мультиплексора соединить с

гнёздами, обслуживающими индикатор

состояния выхода, расположенный в

верхней правой части лицевой панели

лабораторного стенда и обозначенный

"Вх. инд." (при наличии на входе

индикатора сигнала логической единицы

загорается красный светодиод, если

сигнал равен нулю, то свечение отсутствует);

г) проверить работу собранного мультиплексора, для чего установить на информационных входах кодовую комбинацию 0100111111110010 и последовательным перебором сигналов управления убедиться в поочередном появлении соответствующих входных сигналов на выходе мультиплексора (следует учитывать, что сигналу тумблера, обслуживающему какой-либо вход управления мультиплексора приписывается двоичный вес этого входа);

д

Рис. 9.2

14

119

Рис. 9.1

сдвиговых регистров не нашли широкого применения в вычислительных устройствах из-за малого объема памяти (глубины стека) и потери информации при считывании. Последнее обстоятельство не позволяет реализовать режим многократного считывания данных.

Альтернативой регистровому стековому запоминающему устройству является, так называемый, "моделируемый" стек. Он строится на основе обычного ОЗУ и дополнительного устройства формирования адреса, в качестве которого чаще всего используется двоичный счетчик с предустановкой. Структурная схема

В запоминающих устройствах стекового типа обращение к ячейкам производится по специальному алгоритму, а именно, после занесения информации в какую-либо ячейку подготавливается к записи соседняя и т.д. Аналогично реализуется и режим считывания. То есть информация в стековом ОЗУ записывается и считывается последовательным образом.

Номер ячейки, в которую будет производиться запись информации или из которой произойдет считывание называется указателем стека (SP) и в процессе работы изменяется автоматически. Из последовательного принципа обработки информации в стековых ОЗУ вытекает жесткая взаимосвязь режимов записи и считывания. В частности оказывается, что в любой данный момент возможно считывание информации, занесенной либо в самом начале работы стека, либо в конце, то есть непосредственно перед переходом в режим считывания.

В первом случае структура стекового ОЗУ называется FIFO (first in, first out - первым вошел, первым вышел), а во втором LIFO (last in, first out - последним вошел, первым вышел). Принцип работы стековых запоминающих устройств пояснен на рис. 9.1. Стрелкой отмечено положение указателя стека, звездочками - произвольные состояния запоминающих ячеек.

Обычно стековые ЗУ используются в устройствах обработки информации с единой шиной данных. Это значит, что записываемые и считываемые из ЗУ данные передаются по одним и тем же линиям. Таким образом, в режиме записи выводы ЗУ, связанные с шиной данных должны вести себя как входы, а в режиме считывания - как выходы. Обычно это реализуется путем использования в схеме специальных шинных формирователей (ШФ) с тремя состояниями, как показано на рис. 9.2 либо введением третьего - высокоимпедансного состояния в само запоминающее устройство.

И

118

соединительные проводники с увеличением количеством штеккеров);

е) последовательно изменяя комбинации сигналов на управляющих входах мультиплексора и логической схемы проверить идентичность формируемых ими логических функций и соответствие их заданным, зафиксировать полученные результаты;

ж)

поменять местами штеккера, связанные

с крайними гнёздами, в которых формируются

управляющие сигналы, (![]() )

проделать все операции, писанные в

пункте "е", определить явный вид

формируемой логической функции, в отчете

объяснить полученные результаты;

)

проделать все операции, писанные в

пункте "е", определить явный вид

формируемой логической функции, в отчете

объяснить полученные результаты;

и)

собрать макет мультиплексора 16![]() 1

с использованием дешифратора, произвести

подключения аналогичные описанным в

пунктах "б" и "в";

1

с использованием дешифратора, произвести

подключения аналогичные описанным в

пунктах "б" и "в";

к) проверить работу мультиплексора по методике, указанной в пункте "г";

л)

считая, что левая группа из двух тумблеров,

связанных с входами управления

![]() задает код числа А, а правая, обслуживающая

входы

задает код числа А, а правая, обслуживающая

входы![]() -

код числа В, установить на информационных

входах сигналы, соответствующие

формированию заданной функции отношения

чисел;

-

код числа В, установить на информационных

входах сигналы, соответствующие

формированию заданной функции отношения

чисел;

м) путем перебора кодов чисел А и В проверить функционирование реализованной на мультиплексоре логической схемы и сравнить полученные результаты о расчётными;

н)

поменять местами группы штеккеров,

посредством которых на управляющие

входы мультиплексора задаются числа А

и В, (![]() )проверить

функционирование системы в этом случае,

зафиксировать и объяснить полученные

результаты;

)проверить

функционирование системы в этом случае,

зафиксировать и объяснить полученные

результаты;

По окончании лабораторной работы рабочая тетрадь с результатами экспериментов представляется преподавателю и в ней делается соответствующая запись о выполнении работы.

15

3. Содержание отчёта.

Окончательный отчет по лабораторной работе должен включать в себя материалы предварительного отчёта, а также описания хода выполненных исследований, полученные результаты, их анализ и соответствующие выводы.

При подготовке к работе рекомендуется использовать следующую литературу:

Угрюмов E.П. Проектирование элементов и узлов ЭВМ. Учеб. пособие для спец. ЭВМ вузов. - М.: Выс.шк. 1987. - 318 с., ил. (стр. 157 - 160).

Опадчий Ю.Ф. и др. Аналоговая и цифровая электроника (Полный курс): Учебник для вузов. - М.: Горячая линия – Телеком, 2000. – 768 с.: ил. (стр 540-544).

Угрюмов Е.П. Цифровая схемотехника. – СПб.: БХВ – Санкт – Петербург, 2000.- 528 с.: ил. ( стр. 54-64)

Схемотехника ЭВМ: Учебник для студентов вузов спец. ЭВМ.Под ред. Г.Н.Соловьева. - М.: Высш. шк., 1985. - 391 с., ил. (стp.110 - 119).