- •Составитель: Валерий Анатольевич Засов

- •Рецензенты: генеральный директор научно-производственного центра «Информационные и транспортные системы», д.Т.Н., профессор с.В. Архангельский

- •Оглавление

- •1.Принципы организации классической эвм

- •2.Структурная организация процессора

- •3.Принципы организации и программирование

- •4.Принципы организации и программирование

- •5.Структурная организация современных

- •Приложение 1.Список основных команд микропроцессора i8080

- •1.Принципы организации классической эвм и определение микропроцессорной системы

- •1.1.Принципы организации эвм Дж. Фон-Неймана

- •1.2.Определение микропроцессора и микропроцессорной системы

- •1.3.Понятие архитектуры микропроцессорной системы

- •1.4.Структура типовой микропроцессорной системы

- •1.4. Командный цикл и его фазы

- •Контрольные вопросы и задания

- •2.2.Устойство управления с аппаратной логикой

- •2.3.Устройство управления с программируемой логикой

- •2.4.Функция и структура арифметико-логического устройства

- •2.5.Система команд процессора и способы адресации

- •Контрольные вопросы и задания

- •3.Принципы организации и программирование

- •3.1.Структурная схема 8-разрядного микропроцессора

- •3.2.Программная модель 8-разрядной микропроцессорной системы

- •3.3. Способы адресации данных в 8-разрядной микропроцессорной системе

- •3.4.Программирование на ассемблере 8-разрядного микропроцессора

- •3.5. Инструментальные средства разработки и отладки программ для 8-разрядных микропроцессоров

- •3.6. Пример решения задачи

- •3.7.Функциональная схема ядра 8-разрядной микропроцессорной системы

- •Контрольные вопросы

- •4. Принципы организации и программирование

- •4.1. Структурная схема микропроцессоров семейства i8086/8088

- •4.2.Функциональная схема центрального процессора на базе микропроцессора i8086/8088

- •Типы циклов шины мп i8086/8088 Таблица 4.2.

- •4.3. Конвейерный метод выполнения команд и направления его развития

- •4.4. Сегментная организация памяти и ее эволюция

- •4.5.Адресное пространство ввода – вывода

- •4.6.Программная модель микропроцессоров i8086/8088 и способы адресации

- •4.7. Описание системы команд 16-разрядного микропроцессора

- •4.8. Основные элементы программ на языке Турбо ассемблер

- •Контрольные вопросы и задания

- •5.Структурная организация современных микропроцессоров

- •5.1.Структура микропроцессора Intel Pentium 4

- •5.2.Структура микропроцессора amd Athlon

- •5.3.Гиперпотоковая технология организации вычислений

- •5.4.Эффективность многоядерной архитектуры микропроцессоров

- •5.5.Регистровые структуры 32-разрядных микропроцессоров

- •5.6.Регистровые структуры 64-разрядных микропроцессоров

- •5.7.Обобщенный формат команд и типы данных

- •Контрольные вопросы и задания

- •6. Организация памяти в микропроцессорных

- •Системах

- •6.1.Назначение, основные параметры и классификация видов памяти

- •6.2. Иерархическая структура памяти мс

- •6.3. Оперативные запоминающие устройства

- •6.4. Постоянные запоминающие устройства

- •7. Интерфейсы микропроцессорных систем

- •7.1. Назначение и функции интерфейсов

- •7.2. Принципы организации и классификация интерфейсов

- •7.3. Система интерфейсов компьютера

- •8.Способы обмена информацией между устройствами микропроцессорной системы

- •8.1. Программно – управляемый обмен и прямой доступ к памяти

- •8.2. Организация прерываний в мс

- •8.3. Циклы шины

- •9. Программируемый периферийный адаптер

- •9.1. Назначение, структурная схема и режимы работы программируемого периферийного адаптера

- •9.2. Управление работой программируемого периферийного адаптера

- •9.3. Примеры программирования периферийного адаптера

- •Признак pc7-pc4

- •Канал а Канал в

- •Контрольные вопросы и задания

- •10. Программируемый интервальный таймер.

- •Организация счета времени и событий

- •10.1.Назначение, структурная схема и программирование таймера.

- •10.2.Режимы работы таймера

- •10.3. Примеры программирования таймера

- •10.4. Организация счета времени и событий в мс

- •Контрольные вопросы и задания

- •Рассмотрим основные блоки программируемого связного адаптера.

- •11.2. Режимы работы связного адаптера

- •11.3. Управление работой и программирование связного адаптера

- •9.4. Особенности программирования асинхронных адаптеров коммуникационных портов компьютеров

- •11.5. Организация обмена между компьютерами по интерфейсу rs-232с

- •Контрольные вопросы и задания

- •Б иблиографический список

- •Список основных команд микропроцессора i8080

- •Список основных команд микропроцессора i8086/8088 и директивы языка Турбо Ассемблер

- •Основные директивы (псевдокоманды) языка

- •Турбо Ассемблер (tasm)

- •Типы символов в tasm

- •Команды передачи данных

- •Арифметические команды

- •Логические команды и команды сдвигов

- •Строковые или цепочечные команды

- •Команды передачи управления

- •Коды условий перехода (сс)

- •Команды управления микропроцессором

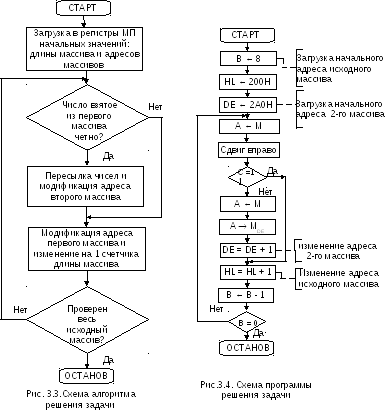

3.6. Пример решения задачи

Порядок решения задач разберем на примере задачи переноса четных чисел из массива с начальным адресом ADR = 200H и длиной N = 8 в массив с начальным адресом ADR2 = 2A0H. Схема алгоритма решения задачи изображена на рис.3.3, а схема программы PRIM приведена на рис.3.4.

В схеме программы использован вычитающий счетчик элементов исходного массива, построенный на регистре В. Исходным загружаемым в счетчик числом является длина массива (В ← 8), изменением текущего состояния счетчика производится уменьшение содержимого регистра В на единицу (В ← В – 1).

Определение четности элемента исходного массива осуществляется путем определения значения младшего бита двоичного кода этого числа. Если меньший бит равен 0, то число четное, а если младший бит равен 1 – число нечетное.

Определение значения младшего бита в программе выполнено путем операции сдвига вправо и проверки значения признака переноса «С» регистра признаков F. В данном примере определение четности числа начинается с пересылки A←M, т. к. команды сдвига выполняются только в аккумуляторе.

В

данном процессоре нет команд пересылки

данных из одной ячейки памяти в другую,

поэтому сначала данные из ячейки памяти

с адресом в HL

пересылаются в регистр А, а затем из

регистра А – в ячейку памяти с адресом

в DE.

В

данном процессоре нет команд пересылки

данных из одной ячейки памяти в другую,

поэтому сначала данные из ячейки памяти

с адресом в HL

пересылаются в регистр А, а затем из

регистра А – в ячейку памяти с адресом

в DE.

Текст исходного модуля рассматриваемой программы имеет следующий вид:

N EQU 8 ; директивы

ADR2 EQU 2A0H ; определения

ADR SET 200H ; имен

ORG 1A0H ; директива установки адреса программы

MVI B, N ; B ← N

LXI D, ADR2 ; DE ← ADR2

-

LXI H, ADR ; HL ← ADR

M1: MOV A, M ; A ← MHL

RRC ; сдвиг вправо

JC M2 ; если есть перенос –

; переход по метке M2

MOV A, M ; A ← MHL Команды

STAX D ; A → MDE программы

INX D ; DE + 1 → DE

-

M2: INX H ; HL + 1 → HL

-

DCR B ; B – 1 → B

JNZ M1 ; если результат предыдущей

; операции ≠ 0 – переход

; по метке М1

HLT ; остановка процессора

END ; директива прекращения

; ассемблирования

Далее производится подготовка загрузочных модулей и отладка программы PRIM с помощью симулятора СРМ.

3.7.Функциональная схема ядра 8-разрядной микропроцессорной системы

Функциональная схема ядра МС, содержащего центральный процессор и память, приведена на рис.3.5. Схема содержит 8-разрядный микропроцессор МП, генератор тактовых импульсов ГТИ, системный контроллер СК, шинный формирователь адреса ШФ, постоянное ПЗУ и оперативное ОЗУ запоминающие устройства, шины адреса ША, шины данных ШД, шины управления ШУ.

МП реализован на БИС КР580ВМ80. ГТИ реализован на микросхеме КР580ГФ24 и формирует синхросигналы для МП.

ШФ адреса, выполненный на микросхеме КР580ВА86, и СК, выполненный на микросхеме КР580ВК28, формируют сигналы для системной шины – ША, ШД, ШУ.

ПЗУ – энергонезависимая память, предназначенная для хранения программ.

ОЗУ – предназначена для записи и чтения данных в процессе вычислений.

Подобную функциональную схему имеют промышленно выпускаемые контроллеры, используемые для автоматизации несложных производственных процессов.