- •Составитель: Валерий Анатольевич Засов

- •Рецензенты: генеральный директор научно-производственного центра «Информационные и транспортные системы», д.Т.Н., профессор с.В. Архангельский

- •Оглавление

- •1.Принципы организации классической эвм

- •2.Структурная организация процессора

- •3.Принципы организации и программирование

- •4.Принципы организации и программирование

- •5.Структурная организация современных

- •Приложение 1.Список основных команд микропроцессора i8080

- •1.Принципы организации классической эвм и определение микропроцессорной системы

- •1.1.Принципы организации эвм Дж. Фон-Неймана

- •1.2.Определение микропроцессора и микропроцессорной системы

- •1.3.Понятие архитектуры микропроцессорной системы

- •1.4.Структура типовой микропроцессорной системы

- •1.4. Командный цикл и его фазы

- •Контрольные вопросы и задания

- •2.2.Устойство управления с аппаратной логикой

- •2.3.Устройство управления с программируемой логикой

- •2.4.Функция и структура арифметико-логического устройства

- •2.5.Система команд процессора и способы адресации

- •Контрольные вопросы и задания

- •3.Принципы организации и программирование

- •3.1.Структурная схема 8-разрядного микропроцессора

- •3.2.Программная модель 8-разрядной микропроцессорной системы

- •3.3. Способы адресации данных в 8-разрядной микропроцессорной системе

- •3.4.Программирование на ассемблере 8-разрядного микропроцессора

- •3.5. Инструментальные средства разработки и отладки программ для 8-разрядных микропроцессоров

- •3.6. Пример решения задачи

- •3.7.Функциональная схема ядра 8-разрядной микропроцессорной системы

- •Контрольные вопросы

- •4. Принципы организации и программирование

- •4.1. Структурная схема микропроцессоров семейства i8086/8088

- •4.2.Функциональная схема центрального процессора на базе микропроцессора i8086/8088

- •Типы циклов шины мп i8086/8088 Таблица 4.2.

- •4.3. Конвейерный метод выполнения команд и направления его развития

- •4.4. Сегментная организация памяти и ее эволюция

- •4.5.Адресное пространство ввода – вывода

- •4.6.Программная модель микропроцессоров i8086/8088 и способы адресации

- •4.7. Описание системы команд 16-разрядного микропроцессора

- •4.8. Основные элементы программ на языке Турбо ассемблер

- •Контрольные вопросы и задания

- •5.Структурная организация современных микропроцессоров

- •5.1.Структура микропроцессора Intel Pentium 4

- •5.2.Структура микропроцессора amd Athlon

- •5.3.Гиперпотоковая технология организации вычислений

- •5.4.Эффективность многоядерной архитектуры микропроцессоров

- •5.5.Регистровые структуры 32-разрядных микропроцессоров

- •5.6.Регистровые структуры 64-разрядных микропроцессоров

- •5.7.Обобщенный формат команд и типы данных

- •Контрольные вопросы и задания

- •6. Организация памяти в микропроцессорных

- •Системах

- •6.1.Назначение, основные параметры и классификация видов памяти

- •6.2. Иерархическая структура памяти мс

- •6.3. Оперативные запоминающие устройства

- •6.4. Постоянные запоминающие устройства

- •7. Интерфейсы микропроцессорных систем

- •7.1. Назначение и функции интерфейсов

- •7.2. Принципы организации и классификация интерфейсов

- •7.3. Система интерфейсов компьютера

- •8.Способы обмена информацией между устройствами микропроцессорной системы

- •8.1. Программно – управляемый обмен и прямой доступ к памяти

- •8.2. Организация прерываний в мс

- •8.3. Циклы шины

- •9. Программируемый периферийный адаптер

- •9.1. Назначение, структурная схема и режимы работы программируемого периферийного адаптера

- •9.2. Управление работой программируемого периферийного адаптера

- •9.3. Примеры программирования периферийного адаптера

- •Признак pc7-pc4

- •Канал а Канал в

- •Контрольные вопросы и задания

- •10. Программируемый интервальный таймер.

- •Организация счета времени и событий

- •10.1.Назначение, структурная схема и программирование таймера.

- •10.2.Режимы работы таймера

- •10.3. Примеры программирования таймера

- •10.4. Организация счета времени и событий в мс

- •Контрольные вопросы и задания

- •Рассмотрим основные блоки программируемого связного адаптера.

- •11.2. Режимы работы связного адаптера

- •11.3. Управление работой и программирование связного адаптера

- •9.4. Особенности программирования асинхронных адаптеров коммуникационных портов компьютеров

- •11.5. Организация обмена между компьютерами по интерфейсу rs-232с

- •Контрольные вопросы и задания

- •Б иблиографический список

- •Список основных команд микропроцессора i8080

- •Список основных команд микропроцессора i8086/8088 и директивы языка Турбо Ассемблер

- •Основные директивы (псевдокоманды) языка

- •Турбо Ассемблер (tasm)

- •Типы символов в tasm

- •Команды передачи данных

- •Арифметические команды

- •Логические команды и команды сдвигов

- •Строковые или цепочечные команды

- •Команды передачи управления

- •Коды условий перехода (сс)

- •Команды управления микропроцессором

11.5. Организация обмена между компьютерами по интерфейсу rs-232с

Для подключения к компьютерам удаленных терминалов, систем сбора информации или других компьютеров часто используют интерфейс последовательной связи RS-232C. Этот популярный интерфейс получил свое название от Рекомендуемого Стандарта номер 232 (Recommended Standard 232 – RS-232) на соединение оборудования, введенного в 1969 году Ассоциацией электронной промышленности (EIA) США. Вариант С этого стандарта определяет протокол, электрические параметры сигналов и описывает разъемы системы последовательной передачи данных, обеспечивающей на расстоянии до 15 м скорость передачи до 20 Кбит/сек / 40/. К настоящему времени введены и широко применяются родственные стандарты RS-422A, RS-423A и RS-485, позволяющие реализовать скорости обмена до 100 Кбит/сек на расстояниях до 1000м /27/. Назначение некоторых сигналов интерфейса RS-232C и разводка разъемов DB25 и DB9 коммуникационных портов компьютера приведены в таблице 11.11.

Каждый СОМ порт компьютера помимо микросхемы асинхронного связного адаптера, регистровая структура которого рассмотрена выше, содержит буферные схемы приемников и передатчиков (например, MAX222, MAX232, MAX242), преобразующих двуполярные сигналы интерфейса RS-232C (см. табл. 9.1.) в сигналы TTL/CMOS уровней, используемые микросхемой связного адаптера. Функциональная схема типового коммуникационного порта компьютера приведена на рис.11.7.

Для осуществления обмена данными между компьютерами по интерфейсу RS-232C необходимо организовать управление потоком данных как между процессором и связным адаптером в каждом из компьютеров, так и управление потоком данных между процессорами компьютеров (микропроцессорных систем).

При передаче очередной байт данных из памяти в буферный регистр связного адаптера процессор может записывать только при условии, что предыдущий байт передан в линию связи. При приеме байт из буферного регистра связного адаптера процессор может считывать в память только при условии его полного приема из линии связи. Для управления потоком данных между процессором и буферным регистром связного адаптера применяется два метода – программный опрос и коммуникационное прерывание.

Табл.11.11.

Сигналы интерфейса RS-232С

-

Номер контакта

разъема

-

Сигнал

-

Назначение сигнала

Вход

или

выход

-

DB25

-

DDB9

1

-

FG

Защитное заземление (Frame Ground), соединяется с корпусом устройства и экраном кабеля

2

3

TD

Передаваемые данные (Transmitted Data)

Выход

3

2

RD

Принимаемые данные (Received Data)

Вход

4

7

RTS

Запрос для передачи данных (Request To Send)

Выход

5

8

CTS

Разрешение терминалу (передатчику) передавать данные (Clear To Send)

Вход

6

6

DSR

Сигнал готовности от аппаратуры передачи данных (модема) (Data Set Ready)

Вход

7

5

SG

Сигнальное заземление (Signal Ground)

8

1

DCD

Сигнал обнаружения несущей удаленного модема (Data Carrier Detect)

Вход

9-19

--

Не используются

20

4

DTR

Сигнал готовности терминала (РС) к обмену данными (Data Terminal Ready)

Выход

21

--

Не используются

22

9

RI

Сигнал вызова (звонка) (Ring Indicator)

Вход

23-35

--

Не используются

При обмене с использованием программного опроса процессор постоянно проверяет регистр состояния связного адаптера для определения моментов чтения из порта данных принятого байта или записи в порт данных очередного передаваемого байта.

В ПСА i8251 регистр состояния имеет адрес на единицу больший базового адреса адаптера.

В СОМ портах компьютера, выполненных на основе микросхемы i8250 или ее аналогов, программно опрашивается порт 3FDh (2FDh), называемый регистром состояния линии.

Бит 0 этого регистра будет равен 0 до тех пор, пока не будет принят код данных в буферный регистр данных приемника адаптера. Когда бит 0 становится равным 1, код данных надо немедленно считать из буферного регистра приемника, в противном случае на него может наложиться следующий принимаемый код данных. После того как код данных считан, бит 0 опять становиться равным 0 и остается таковым, пока не будет принят следующий код.

Бит 5 регистра состояния линии будет равен 0, пока идет процесс передачи кода данных из буферного регистра передатчика в линию связи. Когда буферный регистр передатчика освобождается, бит 5 становиться равным 1 и возможна запись из памяти в буферный регистр передатчика очередного кода данных.

К оммуникационная

программа кроме управления приемом и

передачей данных должна контролировать

правильность процесса обмена. Для этого

производится анализ бита 1 – бита 4

регистра состояния линии (см. табл.9.9.),

что позволяет определить наличие тех

или иных ошибок, возникающих при обмене.

оммуникационная

программа кроме управления приемом и

передачей данных должна контролировать

правильность процесса обмена. Для этого

производится анализ бита 1 – бита 4

регистра состояния линии (см. табл.9.9.),

что позволяет определить наличие тех

или иных ошибок, возникающих при обмене.

Коммуникационные программы, реализующие метод программного опроса, неэффективно используют ресурсы микропроцессора, ибо временные затраты программы существенно превышают время на собственно прием и передачу данных.

Более эффективным, и поэтому более предпочтительным, является второй метод управления потоком данных между процессором и буферным регистром связного адаптера, основанный на коммуникационных прерываниях, генерируемых асинхронными связными адаптерами СОМ портов компьютера при программируемых условиях. Порт СОМ1 генерирует аппаратное прерывание IRQ4, которому соответствует вектор прерывания INT0Ch, а порт СОМ2 – аппаратное прерывание IRQ3 с вектором INT0Bh. Сигналы коммуникационных прерываний портов поступают на соответствующие входы запросов на прерывания микросхемы i8259 – программируемого контроллера прерываний. Коммуникационные программы, использующие прерывания портов, не затрачивают на ввод и вывод больше времени, чем он того требует, и обычно функционируют в фоновом режиме.

Для разрешения прерываний необходимо на этапе инициализации асинхронного связного адаптера установить в 1 биты порта 3F9h (2F9h) управления прерываниями, соответствующие тем прерываниям, которые нужно обрабатывать.

Когда происходит прерывание, программа – обработчик прерывания должна проанализировать причину прерывания, прочитав содержимое порта 3FAh (2FAh) идентификации прерывания. Определив причину прерывания программа – обработчик устраняет ее и выполняет все необходимые действия. Например, если прерывание вызвано событием «данные приняты и доступны для чтения», обработчик прерывания считывает байт из буферного регистра приемника и записывает его в память.

Перед завершением своей работы программа – обработчик прерывания должна проанализировать наличие других прерываний, ожидающих обслуживания. Такая ситуация может возникнуть, когда одновременно произойдет несколько прерываний. В этом случае бит 0 регистра идентификации прерывания будет установлен в 1. Если такая ситуация имеет место, перед завершением обработки прерывания, необходимо снова прочитать регистр идентификации прерывания и обработать очередное прерывание. Так следует поступать до тех пор, пока бит 0 регистра идентификации прерывания не станет равным 0.

В конце программы – обработчика аппаратного прерывания обязательно требуется очистить внутренний регистр обслуживания прерывания контроллера i8259, чтобы разрешить обработку прерываний с более низкими уровнями, чем только что обработанное.

Обычная микросхема асинхронного связного адаптера i8250 не имеет буферной памяти, поэтому при больших скоростях обмена число прерываний, генерируемых схемой за одну секунду будет велико. Например, при скорости обмена 115200 бит/сек за одну секунду генерируется в среднем 11520 прерываний, и выполнение фоновой задачи обмена может существенно замедлить выполнение основных задач. Более современные асинхронные адаптеры, например, NS16550A, содержат буферную память. При использовании режима буферизации, например, на 14 символов, число прерываний за одну секунду при той же скорости 115200 бит/сек сократиться до 823, поэтому степень влияния фоновой задачи на скорость выполнения основной задачи будет значительно меньше.

Для управления потоком данных между компьютерами могут использоваться два варианта протокола –аппаратный и программный.

Аппаратный протокол RTS/CTS управления потоком использует сигнал CTS, который позволяет остановить передачу данных компьютером, если другой компьютер – приемник не готов к их приему. Компьютер – передатчик передает в линию связи очередной байт только при сигнале CTS=1. При сигнале CTS=0 (неготовность компьютера - приемника) компьютер – передатчик останавливает передачу, но байт, который уже начал передаваться задержать сигналом CTS невозможно. Это гарантирует целостность кодовой посылки.

Аппаратный протокол обеспечивает самую быструю реакцию компьютера – передатчика на состояние компьютера – приемника. Обычно даже самые простые микросхемы асинхронных адаптеров имеют не менее двух регистров в приемной части – сдвигающий для приема очередной кодовой посылки и буферный, из которого принятый байт считывается процессором. Это позволяет реализовывать обмен с аппаратным протоколом RTS/CTS без потери данных, не используя программную буферизацию.

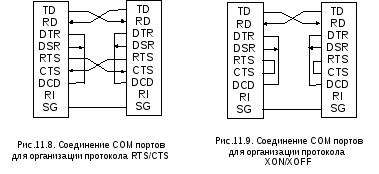

При непосредственном (без модемов) соединении двух компьютеров (микропроцессорных систем) аппаратный протокол требует перекрестного соединения линий RTS – CTS, как показано на рис.11.8.

Программный протокол XON/XOFF управления потоком предполагает наличие двунаправленного канала передачи данных. Управление обменом производится следующим образом. Если компьютер, принимающий данные, обнаруживает причины, по которым он не может их далее принимать, этот компьютер по обратному последовательному каналу посылает байт – символ XOFF (13h). Другой компьютер, приняв этот символ, приостанавливает передачу. Далее, когда компьютер - приемник снова становится готовым к приему данных, он посылает байт – символ XON (11h), приняв который компьютер – передатчик возобновляет передачу. Время реакции передатчика на изменение состояния приемника по сравнению с аппаратным протоколом увеличивается по крайней мере на время передачи управляющего символа (XON или XOFF) плюс время реакции программы передатчика на прием символа. Поэтому данные без потерь могут приниматься только приемником, имеющим дополнительную буферную память для принимаемых данных. В этой буферной памяти всегда должно быть зарезервировано свободное место на случай неготовности компьютера- приемника продолжать прием данных и передачи им символа XOFF.

Преимущество программного протокола при непосредственном соединении компьютеров (МС) заключается в отсутствии необходимости передачи управляющих сигналов RTS или CTS интерфейса, что позволяет использовать для двухстороннего обмена минимальный трехпроводный кабель, как показано на рис.11.9.

Недостатком этого протокола, кроме требования наличия буферной памяти и большого времени реакции, является сложность реализации полнодуплексного режима обмена. В этом случае из потока принимаемых данных должны выделяться и обрабатываться байты – символы управления потоком, что ограничивает набор передаваемых символов.

Кроме этих двух распространенных стандартных протоколов, поддерживаемых различными периферийными устройствами и операционными системами, существуют и некоторые другие. Например, ряд протоколов использует для управления обменом условие BREAK – запрос на прерывание передачи, для чего анализируется состояние бита 4 порта 3FDh (2FDh), представляющего собой регистр состояния линии.

Рассмотрим примеры фрагментов коммуникационных программ на языке Turbo Assembler, реализующих изложенные выше алгоритмы обмена /21/.

Пример 1.

;=============================================================

;Этот фрагмент коммуникационной программы выполняет программный ;опрос регистра состояния линии, т.е. порта 3FDh (2FDh), и анализирует ;байт – символ XOFF

;=============================================================

-

………………….

……..

…………………………

……………………………...

;Процедура цикла опроса регистра состояния (статуса) линии порта 3FDh

KEEP_TRYING:

MOV

DX,BASE_ADDRESS

;Запись базового адреса ;адаптера

ADD

DX,5

;Указываем на регистр ;статуса линии

IN

AL,DX

;Получаем байт статуса

;линии

TEST

AL,00011110B

;Проверяем, есть ли ;ошибки при обмене

JNZ

ERROR_ROUTINE

;Если да, то переходим к ;обработке ошибок ;процедурой ;ERROR_ROUTINE

TEST

AL,00000001B

;Проверяем, получены ли ;данные

JNZ

RECEIVE

;Если да, то переходим к ;приему процедурой ;RECEIVE

TEST

AL,00100000B

;Проверяем готовность к ;передаче

JZ

KEEP_TRYING

;Если нет, то переходим к ;началу цикла опроса ;KEEP_TRYING

;Процедура передачи символа, принимаемого с клавиатуры

MOV

AH.1

;Функция проверки ;нажатия клавиши

INT

16H

;Прерывание клавиатуры ;BIOS

JZ

KEEP_TRYING

;Возврат, если не было ;нажатия на клавишу

MOV

AH,0

;Функция получения кода с ;клавиатуры

INT

16H

;Теперь символ клавиши в ;AL

SUB

DX,5

;Запись базового адреса ;адаптера – буферного ;регистра передатчика

OUT

DX,AL

;Передача символа в ;линию связи

JMP

SHORT KEEP_TRYING

;Возврат к началу цикла

;Процедура приема символа и вывода его на экран

RECEIVE:

MOV

DX,BASE_ADDRESS

;Запись базового адреса ;адаптера

IN

AL,DX

;Считываем полученный ;символ

CMP

AL,13H

;Проверка символа на ;XOFF

JE

XOFF_ROUTINE

;Если принятый символ ;XOFF, то переходим к ;процедуре обработки ;XOFF_ROUTINE(передачу ;прекращаем до получения ;символа XON)

MOV

DL,AL

;Готовим символ для ;вывода на экран

MOV

AH,2

;Функция вывода символа ;на экран

INT

21h

;Вывод символа на экран

JMP

SHORT KEEP_TRYING

;Возврат к началу цикла

………………….

……..

…………………………...

………………………………...

Пример 2.

;=============================================================

;Этот фрагмент коммуникационной программы использует коммуникационное прерывание

;=============================================================

-

………………….

……..

………………………...

……………………………...

;Производим установку вектора прерывания на адрес программы IO_INT – ;обработчика коммуникационного прерывания

PUSH

DS

;Сохраняем регистр DS

MOV

DX,OFFSET IO_INT

;Записываем смещение IP ;процедуры обработчика ;прерываний IO_INT

MOV

AX,SEG IO_INT

;Записываем значение ;сегмента CS процедуры ;обработчика прерываний ;IO_INT в сегментный ;регистр DS

MOV

DS.AX

MOV

AL,0BH

;Записываем номер ;вектора прерываний для ;порта СОМ1

MOV

AH,25H

;Функция DOS установки ;вектора 0Bh на адрес ;программы - обработчика

INT

21H

;Производим установку ;вектора на адрес ;программы - обработчика

;Инициализация регистра управления прерываниями – порта 3F9h (2F9h)

MOV

DX,BASE_ADDRESS

;Запись базового адреса ;адаптера

INC

DX

;Получаем адрес регистра ;управления прерываниями

MOV

AL,00000011B

;Разрешаем прерывания ;приема и передачи

OUT

DX,AL

POP

DS

;Восстанавливаем ;сегментный регистр DS

………………….

……….

………………………...

………………………………….

………………….

……….

………………………...

………………………………….

;Процедура IO_INT обработки прерывания, сначала определяем его тип

IO_INT PROC FAR

NEXT_INT:

MOV

DX,BASE_ADDRESS

;Запись базового адреса ;адаптера

INC

DX

;Указываем на регистр ;идентификации ;прерывания

INC

DX

IN

AL,DX

;Считываем содержимое ;этого регистра

TEST

AL,00000100B

;Проверяем, это ;прерывание от ;передатчика?

JNZ

TRANSMIT

;Если да, переходим к ;процедуре передачи ;TRANSMIT

RECEIVE:

MOV

DX,BASE_ADDRESS

;Если нет, выполняем ;процедуру приема ;RECEIVE

……………………………………

……….

……….

……………………..…………………………..

;Здесь расположена ;процедура приемаRECEIVE

………………….

……….

………………………...

………………………………….

………………….

……….

………………………...

………………………………….

JMP

SHORT ANOTHER

;Переходим к проверке на ;наличие других ;прерываний, ожидающих ;обслуживания

TRANSMIT:

MOV

DX,BASE_ADDRESS

;Здесь расположена ;процедура передачи ;TRANSMIT

………………….

……….

………………………...

………………………………….

………………….

……….

………………………...

………………………………….

;Перед выходом из программы – обработчика проверяем, нет ли других ;прерываний, ожидающих обслуживания

ANOTHER:

MOV

DX,BASE_ADDRESS

;Запись базового адреса ;адаптера

INC

DX

;Указываем на регистр ;идентификации ;прерывания

INC

DX

IN

AL,DX

;Считываем содержимое ;этого регистра

TEST

AL,00000001B

;Проверяем бит 0 регистра

JNZ

NEXT_INT

;Если бит 0 равен 1, то ;переходим на начало ;обработчика IO_INT

MOV

AL,20H

; Если бит 0 равен 0, то ;очищаем регистр ;обслуживания прерываний ;контроллера прерываний

OUT

20H,AL

IRET

;Возврат из обработчика ;прерываний

IO_INT

ENDP