- •Составитель: Валерий Анатольевич Засов

- •Рецензенты: генеральный директор научно-производственного центра «Информационные и транспортные системы», д.Т.Н., профессор с.В. Архангельский

- •Оглавление

- •1.Принципы организации классической эвм

- •2.Структурная организация процессора

- •3.Принципы организации и программирование

- •4.Принципы организации и программирование

- •5.Структурная организация современных

- •Приложение 1.Список основных команд микропроцессора i8080

- •1.Принципы организации классической эвм и определение микропроцессорной системы

- •1.1.Принципы организации эвм Дж. Фон-Неймана

- •1.2.Определение микропроцессора и микропроцессорной системы

- •1.3.Понятие архитектуры микропроцессорной системы

- •1.4.Структура типовой микропроцессорной системы

- •1.4. Командный цикл и его фазы

- •Контрольные вопросы и задания

- •2.2.Устойство управления с аппаратной логикой

- •2.3.Устройство управления с программируемой логикой

- •2.4.Функция и структура арифметико-логического устройства

- •2.5.Система команд процессора и способы адресации

- •Контрольные вопросы и задания

- •3.Принципы организации и программирование

- •3.1.Структурная схема 8-разрядного микропроцессора

- •3.2.Программная модель 8-разрядной микропроцессорной системы

- •3.3. Способы адресации данных в 8-разрядной микропроцессорной системе

- •3.4.Программирование на ассемблере 8-разрядного микропроцессора

- •3.5. Инструментальные средства разработки и отладки программ для 8-разрядных микропроцессоров

- •3.6. Пример решения задачи

- •3.7.Функциональная схема ядра 8-разрядной микропроцессорной системы

- •Контрольные вопросы

- •4. Принципы организации и программирование

- •4.1. Структурная схема микропроцессоров семейства i8086/8088

- •4.2.Функциональная схема центрального процессора на базе микропроцессора i8086/8088

- •Типы циклов шины мп i8086/8088 Таблица 4.2.

- •4.3. Конвейерный метод выполнения команд и направления его развития

- •4.4. Сегментная организация памяти и ее эволюция

- •4.5.Адресное пространство ввода – вывода

- •4.6.Программная модель микропроцессоров i8086/8088 и способы адресации

- •4.7. Описание системы команд 16-разрядного микропроцессора

- •4.8. Основные элементы программ на языке Турбо ассемблер

- •Контрольные вопросы и задания

- •5.Структурная организация современных микропроцессоров

- •5.1.Структура микропроцессора Intel Pentium 4

- •5.2.Структура микропроцессора amd Athlon

- •5.3.Гиперпотоковая технология организации вычислений

- •5.4.Эффективность многоядерной архитектуры микропроцессоров

- •5.5.Регистровые структуры 32-разрядных микропроцессоров

- •5.6.Регистровые структуры 64-разрядных микропроцессоров

- •5.7.Обобщенный формат команд и типы данных

- •Контрольные вопросы и задания

- •6. Организация памяти в микропроцессорных

- •Системах

- •6.1.Назначение, основные параметры и классификация видов памяти

- •6.2. Иерархическая структура памяти мс

- •6.3. Оперативные запоминающие устройства

- •6.4. Постоянные запоминающие устройства

- •7. Интерфейсы микропроцессорных систем

- •7.1. Назначение и функции интерфейсов

- •7.2. Принципы организации и классификация интерфейсов

- •7.3. Система интерфейсов компьютера

- •8.Способы обмена информацией между устройствами микропроцессорной системы

- •8.1. Программно – управляемый обмен и прямой доступ к памяти

- •8.2. Организация прерываний в мс

- •8.3. Циклы шины

- •9. Программируемый периферийный адаптер

- •9.1. Назначение, структурная схема и режимы работы программируемого периферийного адаптера

- •9.2. Управление работой программируемого периферийного адаптера

- •9.3. Примеры программирования периферийного адаптера

- •Признак pc7-pc4

- •Канал а Канал в

- •Контрольные вопросы и задания

- •10. Программируемый интервальный таймер.

- •Организация счета времени и событий

- •10.1.Назначение, структурная схема и программирование таймера.

- •10.2.Режимы работы таймера

- •10.3. Примеры программирования таймера

- •10.4. Организация счета времени и событий в мс

- •Контрольные вопросы и задания

- •Рассмотрим основные блоки программируемого связного адаптера.

- •11.2. Режимы работы связного адаптера

- •11.3. Управление работой и программирование связного адаптера

- •9.4. Особенности программирования асинхронных адаптеров коммуникационных портов компьютеров

- •11.5. Организация обмена между компьютерами по интерфейсу rs-232с

- •Контрольные вопросы и задания

- •Б иблиографический список

- •Список основных команд микропроцессора i8080

- •Список основных команд микропроцессора i8086/8088 и директивы языка Турбо Ассемблер

- •Основные директивы (псевдокоманды) языка

- •Турбо Ассемблер (tasm)

- •Типы символов в tasm

- •Команды передачи данных

- •Арифметические команды

- •Логические команды и команды сдвигов

- •Строковые или цепочечные команды

- •Команды передачи управления

- •Коды условий перехода (сс)

- •Команды управления микропроцессором

-

Контрольные вопросы и задания

1.Какие особенности архитектуры имеет семейство микропроцессоров i8086/8088?

2.В чем суть конвейерного метода выполнения команд? Для каких типов задач конвейерный метод эффективен, а для каких нет?

3.Для эффективной работы конвейера как должны соотноситься длина конвейера и длина программы?

4.Выведите формулу для определения оптимального числа ступеней конвейера.

5.Структурная организация современных микропроцессоров

Характерными чертами современных микропроцессоров являются:

-

32-разрядные и 64-разрядные АЛУ;

-

адресное пространство памяти, определяемое сотнями Гбайт;

-

гарвардская архитектура с разделением потоков команд и данных;

-

конвейерное выполнение команд;

-

использование суперскалярной архитектуры;

-

гиперпотоковая и многоядерная организация вычислений;

-

динамическое изменение последовательности выполняемых команд;

-

предсказание ветвлений.

Основные принципы структурной организации современных процессоров рассмотрим на примерах микропроцессоров Pentium и Athlon, производимыми ведущими разработчиками процессоров – фирмами Intel и Advance Micro Devices (AMD).

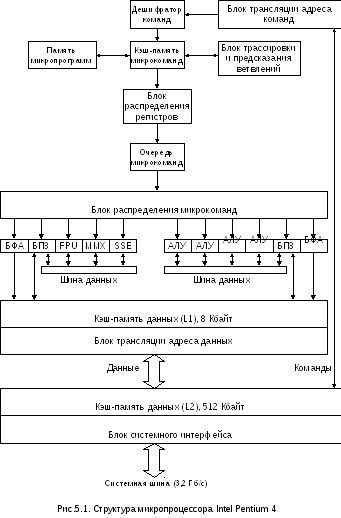

5.1.Структура микропроцессора Intel Pentium 4

Архитектура процессора Pentium 4, получившая название NetBurst (пакетно-сетевая), ориентирована на эффективную работу с Internet-приложениями. К основным особенностям данной архитектуры относятся:

-

кэш-память первого уровня с отслеживанием выполнения команд;

-

кэш-память второго уровня с улучшенной передачей данных;

-

гиперпоточная технология выполнения команд;

-

улучшенное динамическое выполнение команд с изменением порядка их следования и усовершенствованный алгоритм предсказания переходов;

-

работа блоков АЛУ на удвоенной по сравнению с ядром частоте;

-

использование расширенного набора потоковых SIMD-команд, получивших обозначение SSE-2;

-

логический блок с предварительной выборкой данных.

Название SIMD-команда представляет собой аббревиатуру от выражения Single Instruction Multiple Data буквально «одна инструкция – много данных» /2/. В современных процессорах, в отличие от обычных команд, оперирующих с двумя числами, SIMD-команда обрабатывает сразу две группы чисел. Такие команды позволяют существенно ускорить обработку потоков данных, что характерно для мультимедиа приложений и телекоммуникационных задач.

К числу первых SIMD-команд относят команды ММХ – MultiMedia Extension, расширяющие набор типовых команд процессора Pentium MMX 57 специальными командами для работы с мультимедийными приложениями.

Дальнейшее развитие потоковых SIMD-команд привело к появлению группы потоковых команд SSE1 (70 команд), и затем SSE2 (271 команда), где аббревиатура SSE – Streaming SIMD Extension, а также группы команд 3DNow! у процессоров фирмы AMD.

Структура

микропроцессора Pentium

4 изображена на рис.5.1. Гарвардская

внутренняя структура процессора

реализуется путем разделения потоков

команд и данных, поступающих с системной

шины через блок внешнего интерфейса и

размещенную на кристалле процессора

общую кэш-память 2–го уровня (L2)

емкостью 512 Кбайт. Такое размещение

позволяет сократить время выборки

команд и данных по сравнению с Pentium

3, где эта кэш-память располагается на

о тдельном

кристалле, расположенном в едином

корпусе с процессором.

тдельном

кристалле, расположенном в едином

корпусе с процессором.

Кэш-память с улучшенной передачей данных второго уровня обеспечивает более скоростной канал данных между кэш-памятью второго уровня и ядром процессора. Разрядность шины кэш-памяти 256 бита (32 байта), передача данных производится каждый такт частоты процессора. В результате для процессора Pentium 4 с тактовой частотой 2,40 ГГц обеспечивается скорость передачи данных 77 Гбайт/c. Для сравнения, оответствующая скорость передачи данных для процессора Intel Pentium 3 с тактовой частотой 1 ГГц равна 16 ГБ/с.

Дешифратор команд работает вместе с памятью микропрограмм и формирует последовательность микрокоманд, обеспечивающих выполнение поступающих в процессор команд программы. Декодированные команды загружаются в кэш-память микрокоманд, откуда они выбираются для исполнения.

Вместо обычной кэш-памяти L1, которая в Pentium 3 была разделена на область инструкций и область данных, в Pentium 4 применен новый подход. Инструкции в кэш-памяти L1 не сохраняются, а кэш-памяти L1 предназначена теперь только для данных. Для кэширования инструкций в Pentium 4 используется Trace Cache, который по сравнению с обычной кэш-памятью L1 имеет ряд особенностей, направленных на минимизацию простоев процессора при выполнении неправильных предсказаний переходов.

Главная особенность состоит в том, что в Trace Cache сохраняются уже декодированные инструкции. Это значит, что в Trace Cache хранятся не классические x86 инструкции, а составляющие их микрокоманды, которыми непосредственно оперирует процессорное ядро.

Сохранение в Trace Cache микрокоманд позволяет избежать повторного декодирования x86 инструкций при повторном выполнении того же участка программы или при неправильном предсказании переходов. Таким образом, после заполнения Trace Cache практически любая команда будет храниться в нем в декодированном виде. Поэтому при поступлении очередной команды блок трассировки выбирает из этой кэш-памяти уже декодированные команды, т.е. микрокоманды, реализующие ее выполнение. Такой подход существенно сокращает время выполнения команд, т.к. число ступеней конвейера, предназначенных для декодирования команд равно 8, что составляет весомую часть от общей длины конвейера в Pentium 4, равной 28 ступеням.

Вторая особенность Trace Cache заключается в том, что микрокоманды в нем сохраняются именно в том порядке, в каком они выполняются. Если в потоке команд оказывается команда условного перехода (ветвление программы), то включается механизм предсказания ветвлений, который формирует адрес следующей выбираемой команды до того, как будет определено условие выполнения перехода. Вероятность того, что переходы предсказываются неправильно, достаточно мала для того, чтобы отказаться от очевидного выигрыша, получаемого путем отказа от повторного декодирования и предсказаний переходов. Кэш-память Trace Cache может хранить до 12000 микрокоманд.

Основной частью блока предсказания ветвлений является ассоциативная память, называемая буфером адресов ветвлений (BTB – Branch Target Buffer), в которой хранятся 4092 адреса ранее выполненных переходов. Кроме того, BTB содержит биты, хранящие предысторию ветвления, которые указывают, выполнялся ли переход при предыдущих выборках данной команды. При поступлении очередной команды условного перехода, указанный в ней адрес сравнивается с содержимым BTB. Если этот адрес не содержится в BTB, то есть ранее не производились переходы по данному адресу, то предсказывается отсутствие ветвления. В этом случае продолжается выборка и декодирование команд, следующих за командой перехода. При совпадении указанного в команде адреса перехода с каким-либо из адресов, хранящихся в BTB, производится анализ предыстории.

В процессе анализа определяется чаще всего реализуемое направление ветвления, а также выявляются чередующиеся переходы. Если предсказывается выполнение ветвления, то выбирается и загружается в контейнер команда, размещенная по предсказанному адресу.

Усовершенствованный блок предсказания ветвления, используемый в Pentium 4, обеспечивает 90%-ую вероятность правильного предсказания. Таким образом, резко уменьшается число перезагрузок конвейера из-за неправильного предсказании ветвления.

После формирования потоков микрокоманд производится выделение регистров, необходимых для выполнения декодированных команд. Эта процедура реализуется блоком распределения регистров, который выделяет для каждого указанного в команде логического регистра (регистра целочисленных операндов EAX, ECX и других, регистра операндов с плавающей точкой ST0-ST7 или регистра блоков MMX, SSE) один из 128 физических регистров, входящих в состав блока регистров замещения (БРЗ).

Эта процедура позволяет выполнять команды, использующие одни и те же логические регистры, одновременно или с изменением их последовательности.

Выбранные микрокоманды размещаются в очереди микрокоманд. В ней содержатся микрокоманды, реализующие выполнение 126 поступивших и декодированных команд, которые затем направляются в исполнительные устройства по мере готовности операндов. Отметим, что в процессорах Pentium 3 в очереди находятся микрокоманды для 40 поступивших команд. Значительное увеличение числа, стоящих в очереди, позволяет более эффективно организовать поток их исполнения, изменяя последовательность выполнения команд и выделяя команды, которые могут выполняться параллельно. Эти функции реализует блок распределения микрокоманд. Он выбирает микрокоманды из очереди не в порядке их поступления, а по мере готовности соответствующих операндов и исполнительных устройств.

В результате, команды, поступившие позже, могут быть выполнены до ранее выбранных команд. При этом реализуется одновременное выполнение нескольких микрокоманд (команд) в параллельно работающих исполнительных устройствах. Таким образом, естественный порядок следования команд нарушается, чтобы обеспечить более полную загрузку параллельно включенных исполнительных устройств и повысить производительность процессора.

Суперскалярная архитектура реализуется путем организации исполнительного ядра процессора в виде ряда параллельно работающих блоков. Арифметико-логические блоки АЛУ производят обработку целочисленных операндов, которые поступают из заданных регистров БРЗ. В эти же регистры заносится результат операции. При этом проверяется также условия ветвления для команд условных переходов и выдаются сигналы перезагрузки конвейера команд в случае неправильно предсказанного ветвления. Работа блоков АЛУ производится на удвоенной по сравнению с ядром частоте.

Адреса операндов, выбираемых из памяти, вычисляются блоком формирования адреса (БФА), который реализует интерфейс с кэш-памятью данных уровня L1 емкостью 8 Кбайт. В соответствии с заданными в декодированных командах способами адресации формируются 48 адресов для загрузки операндов из памяти в регистр БРЗ и 24 адреса для записи из регистра в память (в Pentium 3 формируются 16 адресов для загрузки регистров и 12 адресов для записи в память). При этом БФА формирует адреса операндов для команд, которые еще не поступили на выполнение. При обращении к памяти БФА одновременно выдает адреса двух операндов: один для загрузки операнда в заданный регистр БРЗ, второй – для пересылки результата из БРЗ в память.

Таким образом, реализуется процедура предварительного чтения данных для последующей их обработки в исполнительных блоках, которая называется спекулятивной обработкой. Аналогичным образом организуется параллельная работа блоков SSE, FPU (АЛУ с плавающей запятой), MMX. При выборке операнда из памяти производится обращение к кэш-памяти данных L1, которая имеет отдельные порты для чтения и записи. За один такт производится выборка операндов для двух команд. Время обращения к этой кэш-памяти составляет 1,42 нс при тактовой частоте 1,5 ГГц, что в 2,1 раза меньше, чем при обращении к кэш-памяти данных в процессоре Pentium 3, работающем на частоте 1,0 ГГц.

При формировании адресов обеспечивается обращение к заданному сегменту памяти. Каждый сегмент может делиться на страницы, размещаемые в различных местах адресного пространства. Блоки трансляции адреса обеспечивают формирование физических адресов команд и данных при использовании страничной организации памяти. Для сокращения времени трансляции используется внутренняя буферная память, которая хранит базовые адреса наиболее часто используемых страниц. В Pentium 4 используется гиперконвейерная технология выполнения команд, при которой число ступеней конвейера достигает 28. таким образом, одновременно в процессе выполнения может находиться до 28 команд, находящихся на разных стадиях их реализации. Эффективность конвейера резко снижается из-за необходимости его перезагрузки при выполнении условных ветвлений, когда требуется произвести очистку всех предыдущих ступеней и выбрать команду из другой ветви программы. Поэтому для сокращения потерь времени, связанных с перезагрузкой конвейера, используется сложный блок предсказания ветвлений.

Блок внешнего интерфейса реализует обмен процессора с системной шиной, к которой подключается память, контроллеры ввода/вывода и другие устройства. Обмен по системной шине осуществляется с помощью 64-разрядной двунаправленной шины данных, 36-разрядной шины адреса, обеспечивающей адресацию до 64 Гбайт внешней памяти.