- •Составитель: Валерий Анатольевич Засов

- •Рецензенты: генеральный директор научно-производственного центра «Информационные и транспортные системы», д.Т.Н., профессор с.В. Архангельский

- •Оглавление

- •1.Принципы организации классической эвм

- •2.Структурная организация процессора

- •3.Принципы организации и программирование

- •4.Принципы организации и программирование

- •5.Структурная организация современных

- •Приложение 1.Список основных команд микропроцессора i8080

- •1.Принципы организации классической эвм и определение микропроцессорной системы

- •1.1.Принципы организации эвм Дж. Фон-Неймана

- •1.2.Определение микропроцессора и микропроцессорной системы

- •1.3.Понятие архитектуры микропроцессорной системы

- •1.4.Структура типовой микропроцессорной системы

- •1.4. Командный цикл и его фазы

- •Контрольные вопросы и задания

- •2.2.Устойство управления с аппаратной логикой

- •2.3.Устройство управления с программируемой логикой

- •2.4.Функция и структура арифметико-логического устройства

- •2.5.Система команд процессора и способы адресации

- •Контрольные вопросы и задания

- •3.Принципы организации и программирование

- •3.1.Структурная схема 8-разрядного микропроцессора

- •3.2.Программная модель 8-разрядной микропроцессорной системы

- •3.3. Способы адресации данных в 8-разрядной микропроцессорной системе

- •3.4.Программирование на ассемблере 8-разрядного микропроцессора

- •3.5. Инструментальные средства разработки и отладки программ для 8-разрядных микропроцессоров

- •3.6. Пример решения задачи

- •3.7.Функциональная схема ядра 8-разрядной микропроцессорной системы

- •Контрольные вопросы

- •4. Принципы организации и программирование

- •4.1. Структурная схема микропроцессоров семейства i8086/8088

- •4.2.Функциональная схема центрального процессора на базе микропроцессора i8086/8088

- •Типы циклов шины мп i8086/8088 Таблица 4.2.

- •4.3. Конвейерный метод выполнения команд и направления его развития

- •4.4. Сегментная организация памяти и ее эволюция

- •4.5.Адресное пространство ввода – вывода

- •4.6.Программная модель микропроцессоров i8086/8088 и способы адресации

- •4.7. Описание системы команд 16-разрядного микропроцессора

- •4.8. Основные элементы программ на языке Турбо ассемблер

- •Контрольные вопросы и задания

- •5.Структурная организация современных микропроцессоров

- •5.1.Структура микропроцессора Intel Pentium 4

- •5.2.Структура микропроцессора amd Athlon

- •5.3.Гиперпотоковая технология организации вычислений

- •5.4.Эффективность многоядерной архитектуры микропроцессоров

- •5.5.Регистровые структуры 32-разрядных микропроцессоров

- •5.6.Регистровые структуры 64-разрядных микропроцессоров

- •5.7.Обобщенный формат команд и типы данных

- •Контрольные вопросы и задания

- •6. Организация памяти в микропроцессорных

- •Системах

- •6.1.Назначение, основные параметры и классификация видов памяти

- •6.2. Иерархическая структура памяти мс

- •6.3. Оперативные запоминающие устройства

- •6.4. Постоянные запоминающие устройства

- •7. Интерфейсы микропроцессорных систем

- •7.1. Назначение и функции интерфейсов

- •7.2. Принципы организации и классификация интерфейсов

- •7.3. Система интерфейсов компьютера

- •8.Способы обмена информацией между устройствами микропроцессорной системы

- •8.1. Программно – управляемый обмен и прямой доступ к памяти

- •8.2. Организация прерываний в мс

- •8.3. Циклы шины

- •9. Программируемый периферийный адаптер

- •9.1. Назначение, структурная схема и режимы работы программируемого периферийного адаптера

- •9.2. Управление работой программируемого периферийного адаптера

- •9.3. Примеры программирования периферийного адаптера

- •Признак pc7-pc4

- •Канал а Канал в

- •Контрольные вопросы и задания

- •10. Программируемый интервальный таймер.

- •Организация счета времени и событий

- •10.1.Назначение, структурная схема и программирование таймера.

- •10.2.Режимы работы таймера

- •10.3. Примеры программирования таймера

- •10.4. Организация счета времени и событий в мс

- •Контрольные вопросы и задания

- •Рассмотрим основные блоки программируемого связного адаптера.

- •11.2. Режимы работы связного адаптера

- •11.3. Управление работой и программирование связного адаптера

- •9.4. Особенности программирования асинхронных адаптеров коммуникационных портов компьютеров

- •11.5. Организация обмена между компьютерами по интерфейсу rs-232с

- •Контрольные вопросы и задания

- •Б иблиографический список

- •Список основных команд микропроцессора i8080

- •Список основных команд микропроцессора i8086/8088 и директивы языка Турбо Ассемблер

- •Основные директивы (псевдокоманды) языка

- •Турбо Ассемблер (tasm)

- •Типы символов в tasm

- •Команды передачи данных

- •Арифметические команды

- •Логические команды и команды сдвигов

- •Строковые или цепочечные команды

- •Команды передачи управления

- •Коды условий перехода (сс)

- •Команды управления микропроцессором

2.4.Функция и структура арифметико-логического устройства

В классической фон-неймановской ЭВМ функция арифметической и логической обработки данных возлагается на арифметико-логическое устройство (АЛУ). Учитывая разнообразие выполняемых операций и типов обрабатываемых данных, реально можно говорить не о едином устройстве, а о комплексе специализированных операционных устройств (ОПУ), каждое из которых реализует определенное подмножество арифметических или логических операций, предусмотренных системой команд вычислительной машины. С этих позиций следует выделить:

-

ОПУ целочисленной арифметики;

-

ОПУ для реализации логических операций;

-

ОПУ десятичной арифметики;

-

ОПУ для чисел с плавающей запятой.

На практике две первых группы обычно объединяются в рамках одного операционного устройства. Специализированные ОПУ десятичной арифметики в современных ЭВМ встречаются достаточно редко, поскольку обработку чисел, представленных в двоично-десятичной форме, можно достаточно эффективно организовать на базе средств целочисленной двоичной арифметики. Таким образом, можно считать, что АЛУ состоит из двух видов операционных устройств: целочисленного ОПУ и ОПУ для обработки чисел в формате с плавающей запятой (ПЗ).

В минимальном варианте АЛУ должно содержать аппаратуру для реализации лишь основных логических операций, сдвигов, а также сложения и вычитания чисел в форме с фиксированной запятой (ФЗ). Опираясь на этот набор, можно программным способом обеспечить выполнение остальных арифметических и логических операций как для чисел с фиксированной запятой, так и для других форм представления информации. Следует, однако, учитывать, что подобный вариант не позволяет добиться высокой скорости вычислений, поэтому по мере расширения технологических возможностей доля аппаратных средств в составе АЛУ постоянно возрастает.

Набор элементов, на основе которых строятся структуры различных ОПУ, называется структурным базисом. Структурный базис ОПУ включает в себя:

-

регистры, обеспечивающие кратковременное хранение слов данных;

-

управляемые шины, предназначенные для передачи слов данных;

-

комбинационные схемы, реализующие вычисление функций микроопераций и логических условий по управляющим сигналам от устройства управления.

На практике распространены два вида структур ОПУ: жесткая и магистральная.

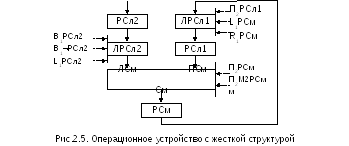

В ОПУ с жесткой структурой /2/ комбинационные схемы жестко распределены между всеми регистрами. К каждому регистру относится свой набор комбинационных схем, позволяющих реализовать определенные микрооперации. Пример ОПУ с жесткой структурой, обеспечивающего выполнение операций типа «сложение», приведен на рис.2.5.

В состав ОПУ входят три регистра со своими логическими схемами:

-

регистр первого слагаемого РСл1 и схема ЛРСл1;

-

регистр второго слагаемого РСл2 и схема ЛРСл2;

-

регистр суммы РСм и схема комбинационного сумматора См.

Логическая схема ЛРСл2 реализует микрооперации передачи второго слагаемого из РСл2 на левый вход сумматора:

-

прямым кодом ЛСм := РСл2 (по сигналу управления В1РСл2);

-

инверсным кодом ЛСм := ¬РСл2 (по сигналу управления В1РСл2);

-

с

о

сдвигом на один разряд влево ЛСм :=

L1(РСл2 • 0) (по сигналу управления L1РСл2).

о

сдвигом на один разряд влево ЛСм :=

L1(РСл2 • 0) (по сигналу управления L1РСл2).

Логическая схема ЛРСл1 обеспечивает передачу результата из регистра РСм в регистр РСл1:

-

прямым кодом РСл1 := РСм (по сигналу управления П2РСл1);

-

со сдвигом на один разряд влево РСл1 := L1(PCм • 0) (по сигналу управления L1PCм);

-

со сдвигом на два разряда вправо РСл1 := R2(s • s • РСм) (по сигналу управления R1PCм).

Комбинационный

сумматор См предназначен для суммирования

(обычного или по модулю 2) операндов,

поступивших на его левый (ЛСм) и правый

(ПСм) входы. Результат суммирования

заносится в регистр РСм: РСм := ЛСм + ПСм

(по сигналу управления П2РСм)

или РСм := ЛСм

![]() ПСм (по сигналу управления П2М2РСм).

ПСм (по сигналу управления П2М2РСм).

Моделью ОПУ с жесткой структурой является так называемый I-автомат, с особенностями синтеза которого можно ознакомиться в /6/.

Затраты времени на выполнение операций типа «сложение» в ОПУ с жесткой структурой равны

ТЖ = tB + tc + tп,

где tB – длительность микрооперации выдачи операндов из регистров; tc – продолжительность микрооперации «сложение»; tп – длительность микрооперации приема результата в регистр.

Достоинством ОПУ с жесткой структурой является высокое быстродействие, недостатком – малая регулярность структуры, что затрудняет реализацию таких ОПУ в виде больших интегральных схем.

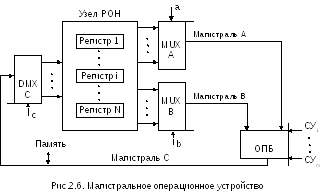

В ОПУ с магистральной структурой все внутренние регистры объединены в отдельный узел регистров общего назначения (РОН), а все комбинационные схемы – в операционный блок (ОПБ), который зачастую ассоциируют с термином «арифметико-логическое устройство».

Операционный блок и узел регистров сообщаются между собой с помощью магистралей – отсюда и название «магистральное ОПУ».

Пример магистрального ОПУ представлен на рис. 2.6.

В состав узла РОН здесь входят N регистров общего назначения, подключаемых к магистралям А и В через мультиплексоры MUX А и MUX В. Каждый из мультиплексоров является управляемым коммутатором, соединяющим выход одного из РОН с соответствующей магистралью. Номер подключаемого регистра определяется адресом a или b, подаваемым на адресные входы мультиплексора из устройства управления.

По

магистралям А и В операнды поступают

на входы операционного блока, к которым

подключается комбинационная схема,

реализующая требуемую микрооперацию

(по сигналу управления из УУ). Таким

образом, любая микрооперация ОПБ может

быть выполнена над содержимым любых

регистров ОПУ. Результат микрооперации

по магистрали С заносится через

демультиплексор DМХ

С в конкретный регистр узла РОН.

Демультиплексор представляет собой

управляемый коммутатор, имеющий один

информационный в ход

и N

информационных

выходов. Вход подключается к выходу с

заданным адресом с, который поступает

на адресные входы DМХ

С из УУ.

ход

и N

информационных

выходов. Вход подключается к выходу с

заданным адресом с, который поступает

на адресные входы DМХ

С из УУ.

Моделью ОПУ с магистральной структурой является М-автомат /6/.

Затраты времени на сложение в магистральных ОПУ больше, чем в ОПУ с жесткой структурой:

ТМ = tB + tС + tП + tMUX + tDMX = tж + tMUX + tDMX,

где tMUX – задержка на подключение операндов из РОН к ОПБ; tDMX – задержка на подключение результата к РОН.

Основным достоинством магистральных ОПУ является высокая универсальность и регулярность структуры, что облегчает их реализацию на кристаллах ИС. Вообще говоря, магистральная структура ОПУ в современных ВМ является наиболее распространенной.