- •Составитель: Валерий Анатольевич Засов

- •Рецензенты: генеральный директор научно-производственного центра «Информационные и транспортные системы», д.Т.Н., профессор с.В. Архангельский

- •Оглавление

- •1.Принципы организации классической эвм

- •2.Структурная организация процессора

- •3.Принципы организации и программирование

- •4.Принципы организации и программирование

- •5.Структурная организация современных

- •Приложение 1.Список основных команд микропроцессора i8080

- •1.Принципы организации классической эвм и определение микропроцессорной системы

- •1.1.Принципы организации эвм Дж. Фон-Неймана

- •1.2.Определение микропроцессора и микропроцессорной системы

- •1.3.Понятие архитектуры микропроцессорной системы

- •1.4.Структура типовой микропроцессорной системы

- •1.4. Командный цикл и его фазы

- •Контрольные вопросы и задания

- •2.2.Устойство управления с аппаратной логикой

- •2.3.Устройство управления с программируемой логикой

- •2.4.Функция и структура арифметико-логического устройства

- •2.5.Система команд процессора и способы адресации

- •Контрольные вопросы и задания

- •3.Принципы организации и программирование

- •3.1.Структурная схема 8-разрядного микропроцессора

- •3.2.Программная модель 8-разрядной микропроцессорной системы

- •3.3. Способы адресации данных в 8-разрядной микропроцессорной системе

- •3.4.Программирование на ассемблере 8-разрядного микропроцессора

- •3.5. Инструментальные средства разработки и отладки программ для 8-разрядных микропроцессоров

- •3.6. Пример решения задачи

- •3.7.Функциональная схема ядра 8-разрядной микропроцессорной системы

- •Контрольные вопросы

- •4. Принципы организации и программирование

- •4.1. Структурная схема микропроцессоров семейства i8086/8088

- •4.2.Функциональная схема центрального процессора на базе микропроцессора i8086/8088

- •Типы циклов шины мп i8086/8088 Таблица 4.2.

- •4.3. Конвейерный метод выполнения команд и направления его развития

- •4.4. Сегментная организация памяти и ее эволюция

- •4.5.Адресное пространство ввода – вывода

- •4.6.Программная модель микропроцессоров i8086/8088 и способы адресации

- •4.7. Описание системы команд 16-разрядного микропроцессора

- •4.8. Основные элементы программ на языке Турбо ассемблер

- •Контрольные вопросы и задания

- •5.Структурная организация современных микропроцессоров

- •5.1.Структура микропроцессора Intel Pentium 4

- •5.2.Структура микропроцессора amd Athlon

- •5.3.Гиперпотоковая технология организации вычислений

- •5.4.Эффективность многоядерной архитектуры микропроцессоров

- •5.5.Регистровые структуры 32-разрядных микропроцессоров

- •5.6.Регистровые структуры 64-разрядных микропроцессоров

- •5.7.Обобщенный формат команд и типы данных

- •Контрольные вопросы и задания

- •6. Организация памяти в микропроцессорных

- •Системах

- •6.1.Назначение, основные параметры и классификация видов памяти

- •6.2. Иерархическая структура памяти мс

- •6.3. Оперативные запоминающие устройства

- •6.4. Постоянные запоминающие устройства

- •7. Интерфейсы микропроцессорных систем

- •7.1. Назначение и функции интерфейсов

- •7.2. Принципы организации и классификация интерфейсов

- •7.3. Система интерфейсов компьютера

- •8.Способы обмена информацией между устройствами микропроцессорной системы

- •8.1. Программно – управляемый обмен и прямой доступ к памяти

- •8.2. Организация прерываний в мс

- •8.3. Циклы шины

- •9. Программируемый периферийный адаптер

- •9.1. Назначение, структурная схема и режимы работы программируемого периферийного адаптера

- •9.2. Управление работой программируемого периферийного адаптера

- •9.3. Примеры программирования периферийного адаптера

- •Признак pc7-pc4

- •Канал а Канал в

- •Контрольные вопросы и задания

- •10. Программируемый интервальный таймер.

- •Организация счета времени и событий

- •10.1.Назначение, структурная схема и программирование таймера.

- •10.2.Режимы работы таймера

- •10.3. Примеры программирования таймера

- •10.4. Организация счета времени и событий в мс

- •Контрольные вопросы и задания

- •Рассмотрим основные блоки программируемого связного адаптера.

- •11.2. Режимы работы связного адаптера

- •11.3. Управление работой и программирование связного адаптера

- •9.4. Особенности программирования асинхронных адаптеров коммуникационных портов компьютеров

- •11.5. Организация обмена между компьютерами по интерфейсу rs-232с

- •Контрольные вопросы и задания

- •Б иблиографический список

- •Список основных команд микропроцессора i8080

- •Список основных команд микропроцессора i8086/8088 и директивы языка Турбо Ассемблер

- •Основные директивы (псевдокоманды) языка

- •Турбо Ассемблер (tasm)

- •Типы символов в tasm

- •Команды передачи данных

- •Арифметические команды

- •Логические команды и команды сдвигов

- •Строковые или цепочечные команды

- •Команды передачи управления

- •Коды условий перехода (сс)

- •Команды управления микропроцессором

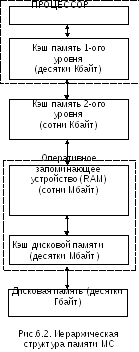

6.2. Иерархическая структура памяти мс

Т ребования

увеличения информационной емкости и

быстродействия памяти и уменьшение ее

стоимости являются противоречивыми.

Действительно, устройства памяти большой

емкости являются сравнительно медленными,

а быстродействующая память большой

емкости является очень дорогой. Поэтому

память МС организуется в виде иерархической

структуры запоминающих устройств (см.

рис.6.2.), обладающих различным

быстродействием, емкостью и стоимостью.

Порядок расположения устройств памяти

по уровням иерархии от верхнего

(процессор) до нижнего (дисковые и

ленточные ВЗУ) соответствует убыванию

быстродействия памяти и возрастанию

ее емкости. Каждый уровень иерархии

может содержать несколько модулей

(экземпляров) соответствующих устройств

памяти для получения нужной емкости

данного уровня памяти.

ребования

увеличения информационной емкости и

быстродействия памяти и уменьшение ее

стоимости являются противоречивыми.

Действительно, устройства памяти большой

емкости являются сравнительно медленными,

а быстродействующая память большой

емкости является очень дорогой. Поэтому

память МС организуется в виде иерархической

структуры запоминающих устройств (см.

рис.6.2.), обладающих различным

быстродействием, емкостью и стоимостью.

Порядок расположения устройств памяти

по уровням иерархии от верхнего

(процессор) до нижнего (дисковые и

ленточные ВЗУ) соответствует убыванию

быстродействия памяти и возрастанию

ее емкости. Каждый уровень иерархии

может содержать несколько модулей

(экземпляров) соответствующих устройств

памяти для получения нужной емкости

данного уровня памяти.

Между устройствами памяти соседних уровней иерархии с помощью операционной организован обмен информацией, называемый свопингом (swapping).

Иерархическая структура памяти основана на ее страничной организации, при которой все пространство памяти разбито на страницы фиксированного размера. Например, в процессорах Pentium допустимы страницы размером 4 Кбайт и 2 Мбайт. В кэш-памяти и ОЗУ из-за их сравнительно небольшой емкости в каждый момент времени хранится только малая часть страниц. Остальные страницы хранятся в дисковой памяти, откуда операционная система может «подкачать» их в ОЗУ и далее в кэш, предварительно выгрузив на диск часть неиспользуемых в данный момент модифицированных страниц. Процесс свопинга происходит в случае, когда требуемая процессору страница отсутствует в кэш или оперативной памяти. Если бы свопинг производился часто, эффективность применения иерархической структуры памяти была бы низкой. Но благодаря свойству пространственной и временной локальности программ и данных свопинг происходит сравнительно редко.

Действительно, как правило, адрес следующей исполняемой команды либо следует за адресом текущей исполняемой команды, либо расположен вблизи него. Такое свойство расположения адресов называется пространственной локальностью программ. Обрабатываемые данные, как правило, организованы в виде массивов, поэтому обращение к операндам также выполняется последовательно в соседние ячейки памяти. Это свойство называется пространственной локальностью данных. Кроме того, из-за наличия в программах циклов и обращений к подпрограммам выборка команды по одному и тому же адресу, а также доступ к данным по некоторому адресу могут повторяться в течение определенного интервала времени. Это свойство называется временной локальностью.

Благодаря рассмотренным свойствам процессор при обращении к памяти значительно чаще обнаруживает в кэш требуемую информацию, чем определяет ее отсутствие и необходимость свопинга нужной страницы.

Важно отметить, что свопинг производится страницами (блоками), при котором устройства памяти используют особый режим передачи – пакетный цикл обмена (Burst Cycle). В пакетном режиме на передачу страницы затрачивается гораздо меньше времени, чем суммарное время передачи отдельных байт (слов) страницы.

Иерархическая структура памяти является основой реализации в компьютере виртуальной памяти, в которой предоставляемое программисту виртуальное пространство оперативной памяти по емкости существенно превышает емкость физически установленной в компьютере оперативной памяти.

Таким образом, иерархическая структура памяти позволяет экономически эффективно сочетать хранение больших объемов информации с быстрым доступом к информации в процессе обработки.