- •Составитель: Валерий Анатольевич Засов

- •Рецензенты: генеральный директор научно-производственного центра «Информационные и транспортные системы», д.Т.Н., профессор с.В. Архангельский

- •Оглавление

- •1.Принципы организации классической эвм

- •2.Структурная организация процессора

- •3.Принципы организации и программирование

- •4.Принципы организации и программирование

- •5.Структурная организация современных

- •Приложение 1.Список основных команд микропроцессора i8080

- •1.Принципы организации классической эвм и определение микропроцессорной системы

- •1.1.Принципы организации эвм Дж. Фон-Неймана

- •1.2.Определение микропроцессора и микропроцессорной системы

- •1.3.Понятие архитектуры микропроцессорной системы

- •1.4.Структура типовой микропроцессорной системы

- •1.4. Командный цикл и его фазы

- •Контрольные вопросы и задания

- •2.2.Устойство управления с аппаратной логикой

- •2.3.Устройство управления с программируемой логикой

- •2.4.Функция и структура арифметико-логического устройства

- •2.5.Система команд процессора и способы адресации

- •Контрольные вопросы и задания

- •3.Принципы организации и программирование

- •3.1.Структурная схема 8-разрядного микропроцессора

- •3.2.Программная модель 8-разрядной микропроцессорной системы

- •3.3. Способы адресации данных в 8-разрядной микропроцессорной системе

- •3.4.Программирование на ассемблере 8-разрядного микропроцессора

- •3.5. Инструментальные средства разработки и отладки программ для 8-разрядных микропроцессоров

- •3.6. Пример решения задачи

- •3.7.Функциональная схема ядра 8-разрядной микропроцессорной системы

- •Контрольные вопросы

- •4. Принципы организации и программирование

- •4.1. Структурная схема микропроцессоров семейства i8086/8088

- •4.2.Функциональная схема центрального процессора на базе микропроцессора i8086/8088

- •Типы циклов шины мп i8086/8088 Таблица 4.2.

- •4.3. Конвейерный метод выполнения команд и направления его развития

- •4.4. Сегментная организация памяти и ее эволюция

- •4.5.Адресное пространство ввода – вывода

- •4.6.Программная модель микропроцессоров i8086/8088 и способы адресации

- •4.7. Описание системы команд 16-разрядного микропроцессора

- •4.8. Основные элементы программ на языке Турбо ассемблер

- •Контрольные вопросы и задания

- •5.Структурная организация современных микропроцессоров

- •5.1.Структура микропроцессора Intel Pentium 4

- •5.2.Структура микропроцессора amd Athlon

- •5.3.Гиперпотоковая технология организации вычислений

- •5.4.Эффективность многоядерной архитектуры микропроцессоров

- •5.5.Регистровые структуры 32-разрядных микропроцессоров

- •5.6.Регистровые структуры 64-разрядных микропроцессоров

- •5.7.Обобщенный формат команд и типы данных

- •Контрольные вопросы и задания

- •6. Организация памяти в микропроцессорных

- •Системах

- •6.1.Назначение, основные параметры и классификация видов памяти

- •6.2. Иерархическая структура памяти мс

- •6.3. Оперативные запоминающие устройства

- •6.4. Постоянные запоминающие устройства

- •7. Интерфейсы микропроцессорных систем

- •7.1. Назначение и функции интерфейсов

- •7.2. Принципы организации и классификация интерфейсов

- •7.3. Система интерфейсов компьютера

- •8.Способы обмена информацией между устройствами микропроцессорной системы

- •8.1. Программно – управляемый обмен и прямой доступ к памяти

- •8.2. Организация прерываний в мс

- •8.3. Циклы шины

- •9. Программируемый периферийный адаптер

- •9.1. Назначение, структурная схема и режимы работы программируемого периферийного адаптера

- •9.2. Управление работой программируемого периферийного адаптера

- •9.3. Примеры программирования периферийного адаптера

- •Признак pc7-pc4

- •Канал а Канал в

- •Контрольные вопросы и задания

- •10. Программируемый интервальный таймер.

- •Организация счета времени и событий

- •10.1.Назначение, структурная схема и программирование таймера.

- •10.2.Режимы работы таймера

- •10.3. Примеры программирования таймера

- •10.4. Организация счета времени и событий в мс

- •Контрольные вопросы и задания

- •Рассмотрим основные блоки программируемого связного адаптера.

- •11.2. Режимы работы связного адаптера

- •11.3. Управление работой и программирование связного адаптера

- •9.4. Особенности программирования асинхронных адаптеров коммуникационных портов компьютеров

- •11.5. Организация обмена между компьютерами по интерфейсу rs-232с

- •Контрольные вопросы и задания

- •Б иблиографический список

- •Список основных команд микропроцессора i8080

- •Список основных команд микропроцессора i8086/8088 и директивы языка Турбо Ассемблер

- •Основные директивы (псевдокоманды) языка

- •Турбо Ассемблер (tasm)

- •Типы символов в tasm

- •Команды передачи данных

- •Арифметические команды

- •Логические команды и команды сдвигов

- •Строковые или цепочечные команды

- •Команды передачи управления

- •Коды условий перехода (сс)

- •Команды управления микропроцессором

-

Типы циклов шины мп i8086/8088 Таблица 4.2.

-

-

Тип циклов шины

0

0

0

-

Подтверждение прерывания

0

0

1

Чтение из внешнего устройства

0

1

0

Запись во внешнее устройство

0

1

1

Останов

1

0

0

Выборка кода команды

1

0

1

Чтение из памяти

1

1

0

Запись в память

1

1

1

Цикла шины нет

-

![]() -

выходной сигнал блокировки (занятости)

шины, информирующий другие активные

устройства системы о том, что они не

могут использовать шину. Этот сигнал,

как и предыдущий используется только

в мультипроцессорных системах.

-

выходной сигнал блокировки (занятости)

шины, информирующий другие активные

устройства системы о том, что они не

могут использовать шину. Этот сигнал,

как и предыдущий используется только

в мультипроцессорных системах.

4.3. Конвейерный метод выполнения команд и направления его развития

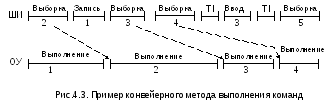

Параллельное выполнение во времени фазы выполнения очередной команды и фазы выборки следующей является важной особенностью МП семейства i8086/8088, позволяющей значительно повысить их быстродействие. Такое решение называется конвейерным методом (pipelining) выполнения команд и иллюстрируется примером, приведенным на рис.4.3., где ТI обозначает холостые такты работы шины, когда очередь команд заполнена, а операционное устройство занято выполнением текущей команды и не запрашивает выполнения цикла шины /2,8,15/.

Рассмотренный пример иллюстрирует работу простейшего 2 - ступенного конвейера, реализованного в МП семейства i8086/8088.

Дальнейшее развитие конвейерного метода выполнения команд идет по пути увеличения числа ступеней командного конвейера /2,9,10/. Учитывая, что число ступеней типового командного цикла равно 5, были разработаны процессоры с 5 – ступенным конвейером, в котором в каждый момент времени одновременно выполняются 5 ступеней командного цикла 5 следующих друг за другом различных команд. По очередному тактовому импульсу каждая команда в конвейере продвигается на следующую ступень, выполненная команда покидает конвейер, а новая входит в него. Принцип работы 5 – ступенного командного конвейера поясняется рис. 4.4. Хотя командам по-прежнему необходимо 5 тактов для прохождения от начала конвейера до его конца, процессор в идеальных условиях в каждом такте может заканчивать выполнение одной команды.

В современных процессорах 5 основных ступеней командного конвейера делятся на части, чтобы уменьшить сложность и время работы каждой ступени. Это позволяет увеличить тактовую частоту и, следовательно, производительность процессора. Такая организация вычислений называется суперконвейерной (superpipelining) /2,9,10/. Например, 20-28 – ступенный конвейер выполнения целочисленных команд имеет процессор Pentium4.

Конвейерное выполнение команд эффективно только на линейных участках программы, когда адрес следующей команды известен до завершения предыдущей.

1-рез. 2-рез. 3-рез.

Ступени конвейера

|

Запись результата

|

|

|

|

|

1 |

2 |

3 |

|

Исполнение команды

|

|

|

|

1 |

2 |

3 |

4 |

|

Чтение операнда

|

|

|

1 |

2 |

3 |

4 |

5 |

|

Декодирование кода команды

|

|

1 |

2 |

3 |

4 |

5 |

6 |

|

Выборка кода команды

|

1 |

2 |

3 |

4 |

5 |

6 |

7 |

П

Такты

Рис.4.4.

Диаграмма работы классического

5-ступенного конвейерного процессора.

Статический метод предсказания работает по схеме, заложенной в процессор, считая, что переходы по одним условиям, вероятнее всего произойдут, а по другим – нет.

Динамическое предсказание опирается на предысторию вычислительного процесса – для каждого конкретного случая перехода в таблице ветвлений накапливается статистика поведения системы, и переход предсказывается, основываясь именно на ней.

Дальнейшим развитием метода предсказаний является исполнение инструкций по предположению (спекулятивное исполнение – speculative execution. В этом методе предсказанные после перехода инструкции (команды) не только декодируются, но и по возможности исполняются до проверки условия перехода. Если предсказание сбывается, вычисления оказываются ненапрасными и результаты используются в последующих фрагментах программы. Если предсказание не сбывается – конвейер сбрасывается и затем выполняет поток инструкций той ветви вычислительного процесса, для которой выполнены условия перехода /2,9,10/. На заполнение всех ступеней конвейера затрачивается определенное число тактов, например, 5 тактов, как показано на диаграмме работы конвейера на рис.4.4. В течение тактов заполнения результаты выполнения инструкций на выходе конвейера не выдаются (конвейер простаивает). Естественно, что такие ситуации снижают быстродействие и производительность конвейерных процессоров.

С другой стороны, статистические исследования показывают, что команды переходов сравнительно редкие, и встречаются в среднем через шесть - восемь команд i80*86.

Хотя, с одной стороны, увеличение числа ступеней конвейера повышает быстродействие микропроцессора, с другой стороны, время заполнения конвейера при его сбросе при неверно предсказанном условном переходе, также возрастает, что негативно сказывается на быстродействии процессора. Кроме того, с увеличением числа ступеней конвейера увеличивается совокупное время передач данных между ступенями конвейера, что также снижает быстродействие конвейерного процессора. Поэтому для определенного уровня быстродействия элементной базы построения микропроцессоров существует оптимальная длина конвейера.

Процессор с единственным конвейером называют скалярным. Дальнейшее увеличение быстродействия можно получить организуя в процессоре несколько конвейеров. Такие процессоры называются суперскалярными (superscalar) , и они позволяют за один такт выполнять более одной команды, как показано на рис.4.5.

Cтупени двух конвейеров Результаты 1 2 3 4 5 6

|

Запись результата

|

|

|

|

|

|

|

|

|

1 |

2 |

3 |

4 |

5 |

6 |

|

Исполнение команды

|

|

|

|

|

|

|

1 |

2 |

3 |

4 |

5 |

6 |

7 |

8 |

|

Чтение операнда

|

|

|

|

|

1 |

2 |

3 |

4 |

5 |

6 |

7 |

8 |

9 |

10 |

|

Декодирование кода команды |

|

|

1 |

2 |

3 |

4 |

5 |

6 |

7 |

8 |

9 |

10 |

11 |

12 |

|

Выборка кода команды

|

1 2 |

3 4 |

5 6 |

7 8 |

9 10 |

11 12 |

13 14 |

|||||||

Н

Такты

Рис.4.5.

Диаграмма работы суперскалярного

5-ступенного конвейерного процессора

(вариант с двумя конвейерами)

Поэтому в состав суперскалярных (иногда называют мультискалярных) процессоров для обеспечения параллельной работы нескольких конвейеров вводят специальные программно–аппаратные средства, реализующие исполнение с изменением последовательности инструкций (out–of–order execution). При этом внутри процессора допускается изменять порядок выполнения инструкций, но внешние (шинные) операции ввода–вывода и записи в память выполняются, конечно же, в порядке, предписанным программным кодом. Цель изменения последовательности исполняемых инструкций внутри процессора – получить в последовательной программе группы инструкций (команд), которые могут выполняться параллельно во времени на разных конвейерах. Этот архитектурный подход увеличения производительности процессоров, называемый также динамическим исполнением команд /2,9,10/ применяется при организации вычислительных процессов в современных процессорах, например, процессорах фирмы Intel.

Конвейерный метод выполнения команд позволяет значительно увеличить быстродействие и производительность процессоров за счет распараллеливания вычислительных процессов. С другой стороны, организация параллельных вычислительных процессов резко увеличивает сложность процессоров, а следовательно трудоемкость изготовления и стоимость.

Для уменьшения сложности процессоров и обеспечения загрузки конвейеров разрабатывают такие компиляторы, генерация программного кода которыми производится с учетом возможности изменения порядка последовательности исполнения инструкций в процессорах /18/.

Дальнейшим развитием суперконвейерной и суперскалярной архитектуры являются многопоточная, многоядерная и мультипроцессорная архитектуры вычислительных систем /2,3,6,8/.