- •Составитель: Валерий Анатольевич Засов

- •Рецензенты: генеральный директор научно-производственного центра «Информационные и транспортные системы», д.Т.Н., профессор с.В. Архангельский

- •Оглавление

- •1.Принципы организации классической эвм

- •2.Структурная организация процессора

- •3.Принципы организации и программирование

- •4.Принципы организации и программирование

- •5.Структурная организация современных

- •Приложение 1.Список основных команд микропроцессора i8080

- •1.Принципы организации классической эвм и определение микропроцессорной системы

- •1.1.Принципы организации эвм Дж. Фон-Неймана

- •1.2.Определение микропроцессора и микропроцессорной системы

- •1.3.Понятие архитектуры микропроцессорной системы

- •1.4.Структура типовой микропроцессорной системы

- •1.4. Командный цикл и его фазы

- •Контрольные вопросы и задания

- •2.2.Устойство управления с аппаратной логикой

- •2.3.Устройство управления с программируемой логикой

- •2.4.Функция и структура арифметико-логического устройства

- •2.5.Система команд процессора и способы адресации

- •Контрольные вопросы и задания

- •3.Принципы организации и программирование

- •3.1.Структурная схема 8-разрядного микропроцессора

- •3.2.Программная модель 8-разрядной микропроцессорной системы

- •3.3. Способы адресации данных в 8-разрядной микропроцессорной системе

- •3.4.Программирование на ассемблере 8-разрядного микропроцессора

- •3.5. Инструментальные средства разработки и отладки программ для 8-разрядных микропроцессоров

- •3.6. Пример решения задачи

- •3.7.Функциональная схема ядра 8-разрядной микропроцессорной системы

- •Контрольные вопросы

- •4. Принципы организации и программирование

- •4.1. Структурная схема микропроцессоров семейства i8086/8088

- •4.2.Функциональная схема центрального процессора на базе микропроцессора i8086/8088

- •Типы циклов шины мп i8086/8088 Таблица 4.2.

- •4.3. Конвейерный метод выполнения команд и направления его развития

- •4.4. Сегментная организация памяти и ее эволюция

- •4.5.Адресное пространство ввода – вывода

- •4.6.Программная модель микропроцессоров i8086/8088 и способы адресации

- •4.7. Описание системы команд 16-разрядного микропроцессора

- •4.8. Основные элементы программ на языке Турбо ассемблер

- •Контрольные вопросы и задания

- •5.Структурная организация современных микропроцессоров

- •5.1.Структура микропроцессора Intel Pentium 4

- •5.2.Структура микропроцессора amd Athlon

- •5.3.Гиперпотоковая технология организации вычислений

- •5.4.Эффективность многоядерной архитектуры микропроцессоров

- •5.5.Регистровые структуры 32-разрядных микропроцессоров

- •5.6.Регистровые структуры 64-разрядных микропроцессоров

- •5.7.Обобщенный формат команд и типы данных

- •Контрольные вопросы и задания

- •6. Организация памяти в микропроцессорных

- •Системах

- •6.1.Назначение, основные параметры и классификация видов памяти

- •6.2. Иерархическая структура памяти мс

- •6.3. Оперативные запоминающие устройства

- •6.4. Постоянные запоминающие устройства

- •7. Интерфейсы микропроцессорных систем

- •7.1. Назначение и функции интерфейсов

- •7.2. Принципы организации и классификация интерфейсов

- •7.3. Система интерфейсов компьютера

- •8.Способы обмена информацией между устройствами микропроцессорной системы

- •8.1. Программно – управляемый обмен и прямой доступ к памяти

- •8.2. Организация прерываний в мс

- •8.3. Циклы шины

- •9. Программируемый периферийный адаптер

- •9.1. Назначение, структурная схема и режимы работы программируемого периферийного адаптера

- •9.2. Управление работой программируемого периферийного адаптера

- •9.3. Примеры программирования периферийного адаптера

- •Признак pc7-pc4

- •Канал а Канал в

- •Контрольные вопросы и задания

- •10. Программируемый интервальный таймер.

- •Организация счета времени и событий

- •10.1.Назначение, структурная схема и программирование таймера.

- •10.2.Режимы работы таймера

- •10.3. Примеры программирования таймера

- •10.4. Организация счета времени и событий в мс

- •Контрольные вопросы и задания

- •Рассмотрим основные блоки программируемого связного адаптера.

- •11.2. Режимы работы связного адаптера

- •11.3. Управление работой и программирование связного адаптера

- •9.4. Особенности программирования асинхронных адаптеров коммуникационных портов компьютеров

- •11.5. Организация обмена между компьютерами по интерфейсу rs-232с

- •Контрольные вопросы и задания

- •Б иблиографический список

- •Список основных команд микропроцессора i8080

- •Список основных команд микропроцессора i8086/8088 и директивы языка Турбо Ассемблер

- •Основные директивы (псевдокоманды) языка

- •Турбо Ассемблер (tasm)

- •Типы символов в tasm

- •Команды передачи данных

- •Арифметические команды

- •Логические команды и команды сдвигов

- •Строковые или цепочечные команды

- •Команды передачи управления

- •Коды условий перехода (сс)

- •Команды управления микропроцессором

11.3. Управление работой и программирование связного адаптера

Управление

обменом между центральным процессором

ЦП (central

processing

unit

- CPU)

u

буфером

данных

ПСА осуществляется по сигналам системной

шины /2, 4, 9/, поступающими на входы ПСА:

![]() ,

,

![]() ,

,

![]() ,

RESET.

Для синхронизации этих сигналов на вход

CLK

из ЦП поступают тактовые сигналы

системной частоты.

,

RESET.

Для синхронизации этих сигналов на вход

CLK

из ЦП поступают тактовые сигналы

системной частоты.

Обмен

осуществляется операциями ввода или

вывода из аккумулятора ЦП при выполнении

команд IN

PORT

или OUT

PORT.

Формируемые при этом в шине управления

ЦП сигналы

![]() или

или

![]() поступают на входы

поступают на входы

![]() или

или

![]() адаптера.

адаптера.

Сигнал

![]() служит для выбора кристалла ПСА и

формируется из старших разрядов (А7-А1)

адреса адаптера.

служит для выбора кристалла ПСА и

формируется из старших разрядов (А7-А1)

адреса адаптера.

На

вход

![]() поступает сигнал соответствующий

младшему разряду адреса ПСА. Сигнал

поступает сигнал соответствующий

младшему разряду адреса ПСА. Сигнал

![]() задает запись в ПСА управляющего

слова

или чтение из ПСА слова

состояния

адаптера. Сигнал

задает запись в ПСА управляющего

слова

или чтение из ПСА слова

состояния

адаптера. Сигнал

![]() задает запись или чтение ЦП в/из связного

адаптера передаваемого или принимаемого

байта данных.

задает запись или чтение ЦП в/из связного

адаптера передаваемого или принимаемого

байта данных.

Вход RESET служит для аппаратного сброса всех внутренних регистров адаптера. Дальнейшее управление работой ПСА со стороны ЦП осуществляется путем записи в адаптер управляющих слов и чтения из него слов состояния.

Управляющее слово инструкция режима - MI (Mode Instruction) задает режим работы адаптера и записывается в ПСА первым после операции сброса. Различают два формата MI - для асинхронного и для синхронного режимов (рис.11.3. и рис.11.4. соответственно). Форматы MI задаются разрядами D0 и D1 управляющего слова.

Назначение разрядов D2-D5 инструкциях режима MI одинаково.

Следующим этапом программирования ПСА в синхронном режиме является запись в него одного или двух синхрослов. В асинхронном режиме записи синхрослов нет.

Управляющее слово инструкция команды – CI (Command Instruction) выполняет оперативное управление установленным режимом обмена.

В табл.11.2 приведен формат инструкции команды CI.

Инструкции команд управляют выполнением конкретных операций на различных этапах обмена и в процессе обмена могут задаваться многократно. Они записываются в ПСА после записи MI (в асинхронном режиме), либо после записи синхрослов (в синхронном режиме). Инструкция команды CI разрешает или запрещает прием (передачу), управляет переходом в режим ожидания синхронизации, а также осуществляет программную установку ПСА в исходное состояние с целью его повторной инициализации.

Все команда, кроме EHM (D7=1 ) используются как в синхронном, так и в асинхронном режимах. Команда ЕНМ используется только для синхронного режима и программируется вместе с командой REN (D2=1).

Команды приема, за исключением IR (D6=1), могут выполняться как вместе, так и раздельно с командами передачи.

Если

в процессе работы передатчика в УСАПП

записывается команда TEN

(D0=0)

или на вход

![]() поступает “1”, то передатчик

ПСА

не прекращает передачу до тех пор, пока

все данные, записанные в буферных схемах

ввода/вывода передатчика, не будут

переданы полностью.

поступает “1”, то передатчик

ПСА

не прекращает передачу до тех пор, пока

все данные, записанные в буферных схемах

ввода/вывода передатчика, не будут

переданы полностью.

Команду ER (D4=1) «Сброс триггеров ошибок» надо записывать каждый раз перед программированием команды REN «Прием информации возможен» или одновременно с командой REN.

Команда D3 «Пауза» действует как в асинхронном, так и синхронном режимах, и указывает на паузу во время передачи данных. Выводить ПСА из состояния "Паузы" можно либо внешним сигналом RESET, либо командой IR “Программный сброс”, либо командой SBRK (D3=0), либо фронтом положительного импульса на входе RD.

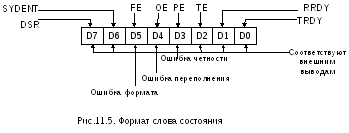

Для организации программно-управляемого обмена по условию в составе ПСА предусмотрено слово состояния - SW (Status Word), формат которого приведен на pис.9.5. Чтение SW возможно в любой момент времени, что позволяет ЦП управлять процессом передачи данных программными средствами. В состав SW входят флажки готовности передатчика TxRDY и приемника RxRDY. После выдачи кода данных флажок TxRDY устанавливается в 0 и затем снова в 1 после передачи DW в буфер передатчика. Аналогично работает флажок RxRDY при заполнении и считывании буфера принятых данных.

Кроме флажков готовности в состав слова состояния входят три признака ошибок. Наличие признаков ошибок не прерывает работы ПСА. Установка триггеров ошибок в исходное состояние осуществляется командой ER (D4=l в слове CI).

Последовательность операций при программировании ПСА и соответствующие этим операциям сигналы управления из МП приведена в табл.11.3.

В ПСА имеются вспомогательные управляющие выводы. Сигналы на этих выводах можно использовать для организации взаимодействия адаптера с ЦП и с ПУ. Рассмотрим основные сигналы этой группы.

На

выводе TRDY

формируется сигнал готовности передатчика

ПСА принять данные от МП для передачи

их в последовательный канал. Этот сигнал

применяется в МС при аппаратно -

управляемом обмене, например, может

использоваться в качестве сигнала

запроса на прерывание МП, либо сигнала

включения режима МП “Ожидание”. Сигнал

TRDY

сбрасывается по срезу сигнала шины

![]() при записи данных.

при записи данных.

На

выводе RRDY

формируется сигнал готовности приемника

ПСА передать в МП принятые из

последовательного канала данные. Этот

сигнал применяется в МС при аппаратно

- управляемом обмене, например, может

использоваться в качестве сигнала

запроса на прерывание МП, либо сигнала

включения режима МП “Ожидание”. Сигнал

RxRDY

сбрасывается по срезу

![]() при чтении данных.

при чтении данных.

На выводе TEND (в слове состояния SW бит TE) формируется сигнал конец передачи. Сигнал передается из ПСА в МС и сигнализирует об отсутствии процесса передачи данных в последовательный канал.

Рассмотрим примеры программ передачи и приема информации с помощью ПСА.

Пример 1. Составить программу, обеспечивающую асинхронную передачу информации из ПСА со скоростью 1/16 от тактовой частоты синхронизации, длиной кода данных 8 бит, контролем на четность и длительностью стопового сигнала 2 бита. Информация для передачи представляет собой блок из 16 байт, хранящийся памяти ОЗУ МС, начиная с ячейки ADR1. Базовый адрес ПСА – 60H.

;Программа OUT_USART асинхронной передачи из ПСА

MVI A,40H ;загрузка в аккумулятор инструкции команды

;программного сброса ПСА

OUT 61H ;засылка инструкции команды сброса в ПСА

MVI A,0FEH ;непосредственная загрузка в аккумулятор ;инструкции режима асинхронного приема или ;передачи

OUT 61H ;засылка инструкции режима в ПСА

MVI A, 21H ;загрузка в аккумулятор инструкции команды ;передачи (D0=1; D5=1)

OUT 61H ;засылка инструкции команды передачи в ПСА

LXI H, ADR1 ;загрузка в регистровую пару HL начального ;адреса блока данных

MVI B, 10H ;начальная установка счетчика байтов, ;организованного в РОНе В

L1: IN 61H ;чтение слова состояния ПСА

ANI 01H ;выделение бита D0 слова состояния ПСА - ;сигнала готовности передатчика к передаче ;очередного байта данных

JZ L1 ;возврат к L1 при D0= 0 (передатчик не готов)

MOV A, M ;пересылка в аккумулятор из косвенно ;адресуемой ячейки памяти очередного байта ;данных

OUT 60H ;вывод байта данных в ПСА

INX H ;вычисление адреса следующей ячейки памяти

DCR B ;декремент счетчика передаваемых байтов

JNZ L1 ;возврат к L1, если передан не весь блок данных

MVI A, 08H ;загрузка в аккумулятор инструкции команды ;конца передачи (D3=1)

OUT 61H ;засылка инструкции команды в ПСА

HLT ;конец программы

Пример 2. Составить программу, обеспечивающую асинхронный прием из ПСА с характеристиками, указанными в примере 1, и обработку блока информации из 16 байт. Каждый принятый байт необходимо обработать в МС программой PROG, записанной в ПЗУ, после чего результат, имеющий формат одного байта, записать в ОЗУ, начиная с ячейки ADR1. Базовый адрес ПСА – 70H.

;Программа IN_USART асинхронного приема из ПСА

MVI A,40H ;загрузка в аккумулятор инструкции команды

;программного сброса ПСА

OUT 71H ;засылка инструкции команды сброса в ПСА

MVI A, 0FEH ;непосредственная загрузка в аккумулятор ;инструкции режима асинхронного приема или ;передачи

OUT 71H ;засылка инструкции режима в ПСА

MVI A, 06 ;непосредственная загрузка в аккумулятор ;инструкции команды приема (D2=1, D1=1)

OUT 71H ;засылка инструкции команды приема в ПСА

LXI H, ADR1 ;загрузка в регистровую память HL начального ;адреса ADR1 ячейки памяти

MVI B, 10H ;начальная установка счетчика принимаемых ;байтов, организованного в регистре В

К1: IN 71H ;чтение слова состояния ПСА

ANI 02 ;выделение бита D1 слова состояния ПСА –;сигнала готовности приемника ПСА - очередной ;байт данных принят и может быть считан из ;буферного регистра ПСА в аккумулятор МП

JZ K1 ;возврат к К1 при D1=0 (приемник не готов – байт ;еще полностью не принят из линии связи)

IN 70H ;ввод байта данных из ПСА в аккумулятор МП

CALL PROG ;обработка принятого слова подпрограммой ;PROG

MOV M, A ;пересылка результата обработки в косвенно – ;адресуемую ячейку памяти

INX H ;вычисление адреса следующей ячейки памяти

DCR B ;декремент счетчика байтов

JNZ K1 ;возврат к К1, если принят не весь блок ;информации

MVI A, 08H ;непосредственная загрузка в аккумулятор ;инструкции команды конца приема

OUT 71H ;засылка инструкции команды в ПСА

HLT ;конец программы

PROG: ………………………;подпрограмма обработки принимаемой

……...……………….;информации