- •Список литературы………………………………………………………………………….

- •Тема 10. Транзисторные усилители электрических сигналов.

- •Тема 11. Нелинейные и параметрические преобразования сигналов.

- •Тема 12. Аналоговые и цифровые элементы и устройства. Аналоговые и цифровые ключи.

- •Тема 13. Комбинационные цифровые устройства.

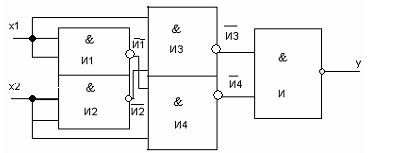

- •Демультиплексор

- •Набор элементарных операций:

- •Тема 14. Дискретная и цифровая обработка сигналов.

- •Тема 15. Волоконно – оптические линии связи (волс)

- •Тема 9. Основы теории электронных приборов .

- •Тема 10. Транзисторные усилители электрических сигналов.

- •Тема 11. Нелинейные и параметрические преобразования сигналов.

- •Тема 12. Аналоговые и цифровые элементы и устройства. Аналоговые и цифровые ключи.

- •Тема 13. Комбинационные цифровые устройства.

- •Демультиплексор

- •Набор элементарных операций:

- •Тема 14. Дискретная и цифровая обработка сигналов.

- •Тема 15. Волоконно – оптические линии связи (волс)

- •Тема 9. Основы теории электронных приборов .

- •Тема 10. Транзисторные усилители электрических сигналов.

- •Тема 11. Нелинейные и параметрические преобразования сигналов.

- •Тема 12. Аналоговые и цифровые элементы и устройства. Аналоговые и цифровые ключи.

- •Тема 13. Комбинационные цифровые устройства.

- •Демультиплексор

- •Набор элементарных операций:

- •Тема 14. Дискретная и цифровая обработка сигналов.

- •Тема 15. Волоконно – оптические линии связи (волс)

Тема 12. Аналоговые и цифровые элементы и устройства. Аналоговые и цифровые ключи.

Аналоговые и цифровые устройства работают соответственно с аналоговыми и цифровыми сигналами. Природа аналоговых сигналов заключается в том, что многие физические величины могут принимать любые значения и непрерывный сигнал, отображающий эту информацию, может иметь большое число значений. В этом случае непрерывный сигнал, который изменяется аналогично исходной информации, называется аналоговым.

Непрерывные сигналы можно представлять и в дискретной форме. И для этого непрерывного сообщения применяют квантование по уровню и времени. Для квантования сигнала по уровню непрерывный сигнал (ток или напряжение) заменяют набором дискретных значений из представленного интервала. Квантование по времени заключается в замене непрерывного сигнала чередующимися импульсами, которые следуют через определенные интервалы времени. Это и есть цифровой сигнал.

Механический ключ (аналоговый коммутатор).

Ключевая схема (рис 12-1) предназначена для коммутации тока в нагрузке и содержит источник напряжения питания, нагрузку (R) и ключ (Кл).

Рис 12-1. Аналоговый коммутатор(механический ключ).

Если ключ идеален, то есть его сопротивление в разомкнутом состоянии бесконечно велико, а в замкнутом равно 0, то ток в цепи при разомкнутом ключе I=0, а при замкнутом I=E/R.

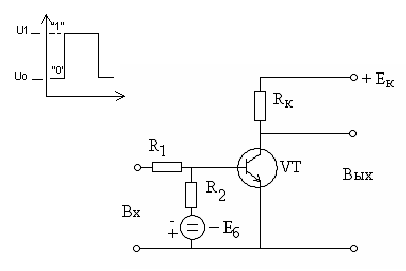

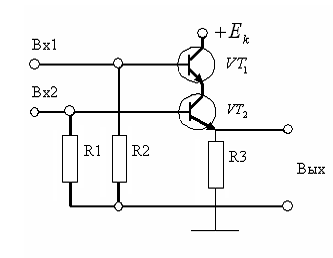

Аналоговый коммутатор на биополярном транзисторе (электронный ключ).

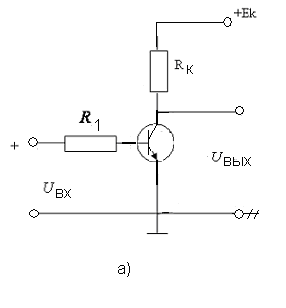

На рисунке 12-2 показана схема коммутатора на биополярном транзисторе.

Рис. 12-2 Схема аналогового коммутатора на биополярном транзисторе.

Для перевода транзистора в режим отсечки следует подать на базу отрицательное напряжение и на выходе Uвых = 0 (выключено). Чтобы открыть VT следует на вход подать напряжение больше, чем напряжение отсечки на величину ΔU=I1R1 и переход коллектор-база откроется и VT будет работать как ключ в инверсном включении.

Диодный коммутатор (аналоговый ключ).

Если на вход подать положительное напряжение (рис 12-3) VD открывается и через него протекает ток (включено), а при отрицательном напряжении, подаваемом на вход, через диод идет незначительный ток(отключен). Диодный коммутатор подобен механическому ключу.

Рис 12-3. Схема последовательного диодного ключа.

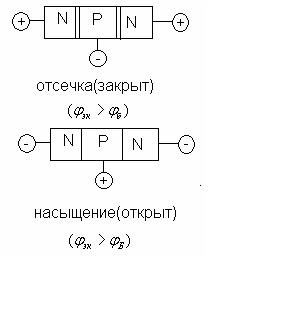

Цифровой электронный ключ на биполярном транзисторе

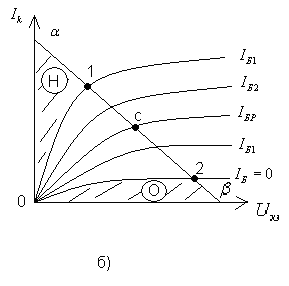

Рис 12-4. Схема цифрового ключа на биполярном транзисторе(а) входная статистическая характеристика VT(б).

В схеме цифрового ключа (рис 12-4), транзистор, работающий в ключевом режиме, должен находится только в определенном состоянии. Первое состояние соответствует точке 1 на выходных статистических характеристиках транзистора(рис 12-4 б) когда Uвх=0, транзистор закрыт и устанавливается это состояние резистором R1. При этом ток коллектора также равен 0 и Uвых=Ек. Второе состояние транзистора соответствует точке 2, которое обеспечивается подачей на вход высокого положительного напряжения и при этом Uвых=0. В этом случае коллекторный ток достигает максимального значения (Ik=Ek/Rk). Так работает цифровой ключ на биполярном транзисторе. Следует заметить, что в настоящее время находят применение цифровые ключи на полевых транзисторах, которые в изготовлении проще, чем на биполярных транзисторах.

Регенеративные импульсные устройства

Принципы построения и режим работы регенеративных импульсных устройств

На вход различных импульсных устройств часто требуется подать импульсы напряжений прямоугольной формы или крутые перепады напряжений. Крутые перепады напряжений (токов) могут создаваться в результате возникновения регенеративных процессов.

Регенеративными называются процессы, протекающие лавинообразно под воздействием положительной обратной связи.

Регенеративными импульсными устройствами называются устройства, в которых в результате регенеративных процессов возникают крутые перепады напряжений и токов. В этих устройствах используют усилители с положительной обратной связью. По построению и назначению регенеративные импульсные устройства делятся на две группы: мультивибраторы и триггеры.

Мультивибраторы на биполярных транзисторах

Мультивибратор это генератор, вырабатывающий импульсы прямоугольной формы.

Рассмотрим

мультивибратор на биполярных транзисторах

V и V

и V .

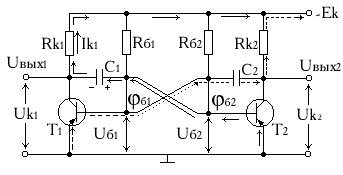

Схема мультивибратора с коллекторно-базовыми

связями представляет собой двухкаскадный

усилитель.

.

Схема мультивибратора с коллекторно-базовыми

связями представляет собой двухкаскадный

усилитель.

![]()

![]()

Рис.12-6 Схема мультивибратора в режиме автоколебаний.

и - обеспечивают ПОС;

и

и

- резисторы, которые осуществляют подачу

напряжения смещения на базы V

и V

;

- резисторы, которые осуществляют подачу

напряжения смещения на базы V

и V

;

Схема

симметрична и

и V

и V

одного типа. Каждый транзистор работает

в режиме ключа, т.е. переходит от отсечки

к насыщению и наоборот.

и V

и V

одного типа. Каждый транзистор работает

в режиме ключа, т.е. переходит от отсечки

к насыщению и наоборот.

заряжается по

контуру

![]() , а

- по контуру

, а

- по контуру

.

На базы V

и V

от

.

На базы V

и V

от

через

и

подается отрицательное смещение, поэтому

и

будут работать в активном режиме. При

малейшем нарушении симметрии в цепи

наступает самовозбуждение. Предположим,

что в какой-то момент

через

и

подается отрицательное смещение, поэтому

и

будут работать в активном режиме. При

малейшем нарушении симметрии в цепи

наступает самовозбуждение. Предположим,

что в какой-то момент

скачком окажется больше

скачком окажется больше

,

т.е.

>

.

Тогда

,

т.е.

>

.

Тогда

возрастает и

возрастает и

станет менее отрицательным, следовательно,

станет менее отрицательным, следовательно,

тоже станет менее отрицательным (т.к.

напряжение на

по второму закону коммутации скачком

измениться не может ) и

подзакроется и

уменьшится. Уменьшение

приведет к уменьшению

тоже станет менее отрицательным (т.к.

напряжение на

по второму закону коммутации скачком

измениться не может ) и

подзакроется и

уменьшится. Уменьшение

приведет к уменьшению

и

и

![]()

станет более отрицательным, следовательно,

станет более отрицательным, следовательно,

станет более отрицательным, V

еще больше откроется и

еще больше возрастет. Это закончится

тем, что транзистор V

войдет в режим насыщения, а V

- в режим отсечки. Этот процесс называют

лавинообразным (регенеративным). Он

происходит очень быстро. Во время

лавинообразного процесса формируются

крутые фронты импульса (аб).рис 12-7)

станет более отрицательным, V

еще больше откроется и

еще больше возрастет. Это закончится

тем, что транзистор V

войдет в режим насыщения, а V

- в режим отсечки. Этот процесс называют

лавинообразным (регенеративным). Он

происходит очень быстро. Во время

лавинообразного процесса формируются

крутые фронты импульса (аб).рис 12-7)

t

а

а

б

б

t

а

б

б

Рис 12-7 эпюры напряжений на выходе мультивибратора

Лавинообразный

процесс прекращается после того, как

V

войдет в режим насыщения, а V

-

в режим отсечки. Тогда

,

а

,

а

.

.

В схеме наступает состояние квазиустойчивого равновесия, во время которого формируются плоские вершины (см. графики) импульсов.

Режим насыщения V поддерживается отрицательным смещением на базе от через , а режим отсечки V поддерживается положительным потенциалом .

При

этом

заряжается по контуру:

![]() с

постоянной времени зарядки

с

постоянной времени зарядки

,

а

перезаряжается по контуру:

,

а

перезаряжается по контуру:

![]() с

постоянной времени перезарядки.

с

постоянной времени перезарядки.

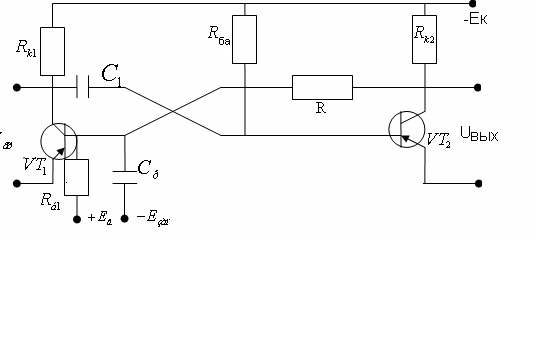

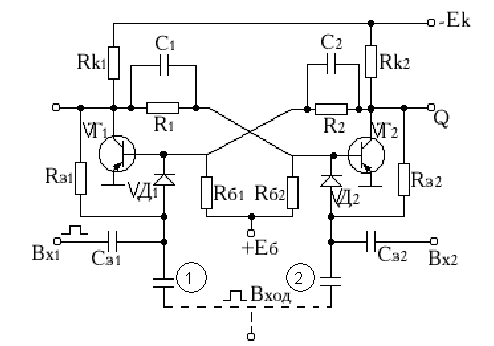

Ждущий мультивибратор с коллекторно-базовыми связями (одновибратор)

Этот мультивибратор используется для получения одиночных импульсов заданной длительности (рис 12-8).

.

Рис. 12-8.Схема ждущего

мультивибратора (одновибратор).

.

Рис. 12-8.Схема ждущего

мультивибратора (одновибратор).

Из рис 12-8 видно,

батарея Еб запирает транзистор

и открывает он тогда, когда его подключают

к Езап (запускающаяся батарея). Параметры

сопротивлений Rк1 и Rк2

подбираются так, чтобы

был закрыт батареей + Еб, а

и открывает он тогда, когда его подключают

к Езап (запускающаяся батарея). Параметры

сопротивлений Rк1 и Rк2

подбираются так, чтобы

был закрыт батареей + Еб, а

был бы открыт и насыщен. Зарядка

конденсатора идет по цепи 0,

,С,

Rк1 и

.

был бы открыт и насыщен. Зарядка

конденсатора идет по цепи 0,

,С,

Rк1 и

.

Для генерации

импульса на базу

подают запускающий импульс (-Езап),

и

открываются, в цепи устанавливается

лавинообразный процесс, изменяются

токи

и

и

и схема опрокидывается. После опрокидывания

схема

открывается и переходит в режим насыщения,

а

в режим отсечки. В этом случае

и

подсоединяются к нулевому зажиму

.

и схема опрокидывается. После опрокидывания

схема

открывается и переходит в режим насыщения,

а

в режим отсечки. В этом случае

и

подсоединяются к нулевому зажиму

.

Теперь

работает по цепи 0,

,

,

Rк1,

.

И по этой цепи

разряжается. Когда

=0,

то потенциал базы

тоже станет равен нулю. При значении 0

открывается и теперь

и

-

открыты, в схеме развивается лавинообразный

процесс и схема опрокидывается. При

этом

- закрыта,

=0,

то потенциал базы

тоже станет равен нулю. При значении 0

открывается и теперь

и

-

открыты, в схеме развивается лавинообразный

процесс и схема опрокидывается. При

этом

- закрыта,

-открыт

и

-открыт

и

,

перезаряжается по схеме 0,

,

перезаряжается по схеме 0,

,

, ,

, ,

, .

Схема опять приходит в устойчивое

состояние, а на выходе получаются почти

прямоугольные импульсы с любой заданной

длительностью.

.

Схема опять приходит в устойчивое

состояние, а на выходе получаются почти

прямоугольные импульсы с любой заданной

длительностью.

Триггеры на дискретных элементах

Триггер это устройство, имеющее два состояния устойчивого равновесия, которые скачкообразно переходят одно в другое под воздействием внешнего импульса.

Триггер – цифровой автомат, обладающий памятью и служащий для хранения одного разряда двоичных чисел (одного бита информации).Его называют также автоматом Мура.

Триггеры изготавливаются как на отдельных (дискретных) элементах, так и в интегральном исполнении. В различных устройствах они выполняют функцию счетных, переключающих, пороговых и запоминающих элементов.

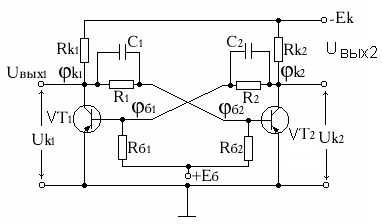

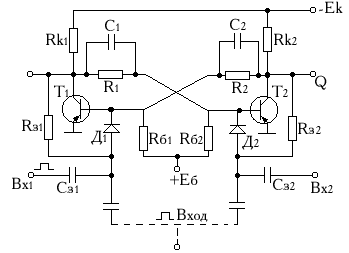

Физические процессы удобнее рассмотреть на схеме триггера в дискретном исполнении с коллекторно-базовыми связями на биполярных транзисторах с независимым смещением (рис.12- 9).

Рис.12-9 Схема триггера с коллекторно-базовыми связями на биполярных транзисторах.

Схема

триггера – двухкаскадный усилитель

постоянного тока с ПОС, осуществляемой

через цепи

и

и

,

которые соединяют коллектор одного с

базой другого транзистора. Схема

симметрична:

,

V

и V

одного типа. В отличии от мультивибратора

триггер имеет источник смещения

,

которые соединяют коллектор одного с

базой другого транзистора. Схема

симметрична:

,

V

и V

одного типа. В отличии от мультивибратора

триггер имеет источник смещения

>0,

(запирающий транзисторы ) и

и

в цепях связи между усилительными

каскадами.

>0,

(запирающий транзисторы ) и

и

в цепях связи между усилительными

каскадами.

Параметры

триггера подбираются так, чтобы открытый

транзистор работал в режиме насыщения,

а закрытый – в режиме отсечки. Открытый

транзистор имеет потенциал коллектора,

близкий к нулю (можно приписать ему

уровень “0”), т.к.

.

Закрытый транзистор имеет потенциал

коллектора близкий к напряжению источника

питания, т.е.

.

Закрытый транзистор имеет потенциал

коллектора близкий к напряжению источника

питания, т.е.

(можно приписать ему уровень “1”), т.к.

(можно приписать ему уровень “1”), т.к.

.

Это состояние триггера устойчивое до

тех пор, пока на вход триггера не будет

подан запускающий импульс, который

переводит триггер из одного устойчивого

состояния в другое. Пусть триггер

находится в таком устойчивом состоянии,

когда V

- открыт, а V

- закрыт, т.е.

.

Это состояние триггера устойчивое до

тех пор, пока на вход триггера не будет

подан запускающий импульс, который

переводит триггер из одного устойчивого

состояния в другое. Пусть триггер

находится в таком устойчивом состоянии,

когда V

- открыт, а V

- закрыт, т.е.

,

a

,

a

.

Это состояние протекает сколь угодно

долго. На базу V

снизу подается напряжение

.

Это состояние протекает сколь угодно

долго. На базу V

снизу подается напряжение

,

а сверху

,

но т.к.

,

а сверху

,

но т.к.

,

то на базу подается отрицательный

потенциал, который удерживает V

в состоянии насыщения. На базу V

снизу

,

то на базу подается отрицательный

потенциал, который удерживает V

в состоянии насыщения. На базу V

снизу

,

а сверху (с коллектора V

)

,

а сверху (с коллектора V

)

.

Следовательно, на базу V

подается положительный потенциал,

который удерживает V

в состоянии отсечки.

.

Следовательно, на базу V

подается положительный потенциал,

который удерживает V

в состоянии отсечки.

Чтобы

вывести схему из устойчивого состояния

нужно подать на базу

через

запускающий импульс положительной

полярности (положительный потенциал)

запускающий импульс положительной

полярности (положительный потенциал)

.

.

Uзап φб1 φб2 φб1 φб2

t

t

О Н О Н

t

Н О Н

Рис.12-10 Эпюры напряжений на выходах триггера:

,

,

- входные импульсы на базы

и

;

- входные импульсы на базы

и

;

0 – отсечка;

Н – насыщение;

,

примерно равное

.

.

Тогда

становится менее отрицательным и V

начинает закрываться, а

- уменьшается и

- уменьшается. При этом

- уменьшается. При этом

становится более отрицательным, а,

следовательно,

тоже более отрицательным и V

будет приоткрываться и т.д. Процесс

будет развиваться лавинообразно и

закончится тем, что V

закроется (отсечка), а V

откроется (насыщение). Чтобы вывести

схему из этого устойчивого состояния,

нужно подать запускающий импульс на

базу открытого теперь V

.

становится более отрицательным, а,

следовательно,

тоже более отрицательным и V

будет приоткрываться и т.д. Процесс

будет развиваться лавинообразно и

закончится тем, что V

закроется (отсечка), а V

откроется (насыщение). Чтобы вывести

схему из этого устойчивого состояния,

нужно подать запускающий импульс на

базу открытого теперь V

.

и

шунтируют

и

ускоряют процесс открывания и закрывания

VT. Их обычно называют

ускоряющими. Если V открыт, а V

закрыт, то

открыт, а V

закрыт, то

и

и

.

Как только V

закроется,

начнет заряжаться и в цепи базы V

потечет зарядный ток, который добавится

к току базы открывающегося V

.

Это ускорит процесс открывания V

.

.

Как только V

закроется,

начнет заряжаться и в цепи базы V

потечет зарядный ток, который добавится

к току базы открывающегося V

.

Это ускорит процесс открывания V

.

Схемы запуска триггера

Существует два способа запуска триггера: раздельный и счетный (общий).

Раздельный запуск.(без пунктирной линии)

Раздельный запуск осуществляется подачей импульсов одной полярности, попеременно то на один, то на другой входы триггера (на базы транзисторов).

Рассмотрим схему триггера с раздельным запуском с подачей запускающих импульсов на базы через диоды (рис.3).

Рис 12-11 Схемы запусков триггера

V и V

и V ,

,

и

и

,

,

и

и

- элементы цепи запуска. Пусть V

открыт (насыщен), а V

закрыт (отсечка). Подадим на

- элементы цепи запуска. Пусть V

открыт (насыщен), а V

закрыт (отсечка). Подадим на

![]() . Он продифференцируется

. Он продифференцируется

на два коротких импульса остроконечной

формы и противоположенной полярности.

Так как

открыт,

то

на два коротких импульса остроконечной

формы и противоположенной полярности.

Так как

открыт,

то

,

а, следовательно,

,

а, следовательно,

,

но

,

но

.

V

открыт и пропустит положительный импульс

на базу. Тогда V

начинает закрываться, а V

открываться. В результате лавинообразного

процесса V

закроется (отсечка), а V

откроется (насыщение). Это состояние

будет сохраняться до тех пор, пока не

поступит

на

.

V

открыт и пропустит положительный импульс

на базу. Тогда V

начинает закрываться, а V

открываться. В результате лавинообразного

процесса V

закроется (отсечка), а V

откроется (насыщение). Это состояние

будет сохраняться до тех пор, пока не

поступит

на

.

Когда V

закроется, то

.

Когда V

закроется, то

,

VД1 закрывается и отключает

,

VД1 закрывается и отключает

от базы V

(поэтому диоды V

и V

называются отсекающими).До подачи

следующего

от базы V

(поэтому диоды V

и V

называются отсекающими).До подачи

следующего

разряжается через

.

Такой триггер называют RS-

триггером.

разряжается через

.

Такой триггер называют RS-

триггером.

Счетный запуск (с учетом пунктирной линии, С31 переносится на 1 и С32 на 2)

При счетном запуске импульсы определенной полярности подаются на общий вход и каждый импульс приводит к опрокидыванию триггера. В отличие от RS- триггера здесь и соединены вместе. Эта схема применяется для счета импульсов.

Пусть

V

открыт (режим насыщения) (

,

),

а V

закрыт (режим отсечки) (

),

а V

закрыт (режим отсечки) ( ,

,

).

Тогда V

открыт, а V

- заперт.

заряжен до

).

Тогда V

открыт, а V

- заперт.

заряжен до

0,

а

до

0,

а

до

.

Положительный

,

продифференцированный

,

проходит через открытый

на базу V

,

подзакрывая его. При этом V

начинает открываться

.

Положительный

,

продифференцированный

,

проходит через открытый

на базу V

,

подзакрывая его. При этом V

начинает открываться

становится более отрицательным). В

результате лавинообразного процесса

V

запирается, а V

открывается, т.е. триггер опрокидывается.

V

и V

пропускают запускающий импульс только

на базу открытого VТ2.

становится более отрицательным). В

результате лавинообразного процесса

V

запирается, а V

открывается, т.е. триггер опрокидывается.

V

и V

пропускают запускающий импульс только

на базу открытого VТ2.

Разрешающие время триггера – время, за которое триггер переходит из одного устойчивого состояния в другое.

- время, в течение

которого транзисторы открываются и

устанавливается ПОС;

- время, в течение

которого транзисторы открываются и

устанавливается ПОС;

- время, в течение

которого длится лавинообразный процесс;

- время, в течение

которого длится лавинообразный процесс;

- время, в течение

которого заканчивается переходной

процесс;

- время, в течение

которого заканчивается переходной

процесс;

Величина,

обратная

,

называется быстродействием триггера.

,

называется быстродействием триггера.

Основные логические элементы.

В алгебре логики истинность суждения (высказывания) обозначают символом "I", а ложное-"0". Значение параметров электронных элементов необходимо перевести на язык алгебры логики ("0" или "I"). Значение параметров можно задавать уровнем напряжения или полярностью импульсов.

Если сигналы подаются в виде высокого и низкого напряжения, то такой способ подачи сигнала называть потенциальным. Логика называется положительной, если высокому потенциалу приписывается "I", а низкому "ноль" "0".

Логика называется отрицательной, если высокому потенциалу приписывается «0»,а низкому «1»

Если сигнал подают в форме импульса, то такой способ подачи называют импульсным. Наличие импульса – «1», отсутствие - «0». Это положительная логика. Если наоборот- отрицательная логика. Если наоборот-отрицательная.

Любые логические операции можно выполнить с помощью трёх основных и простых логических элементов(базисных логических функций), выполняющих операции:

"НЕ"- логическое отрицание (инверсия); "И"- логическое умножение (конъюнкция);

"ИЛИ"-логическое сложение (дизъюнкция).

Функционально полную систему могут обеспечить составные (комбинированные) логические элементы, выполняющие логические операции:

"И-НЕ"- отрицание конъюнкции;

"ИЛИ-НЕ"- отрицание дизъюнкции.

Логические элементы в дискретном исполнении

Базисные логические функции(логические элементы) могут быть представлены как в дискретном исполнении, так и методами интегральной технологии. Базисные логические функции(логические элементы) «И», «ИЛИ» и «НЕ» могут выполняться на диодах, резисторах, биполярных полевых транзисторах. В соответствии с конструкцией построения логических элементов различают резисторно-транзисторную логику(РТЛ), диодно-транзисторную(ДТЛ), транзисторно-транзисторную логику(ТТЛ), а также логику на полевых транзисторах(«р»-канальная-рМОП, «n»-nМОП), комплементарную (КМДП) и динамическую (МОП).

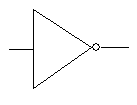

Логический элемент "НЕ" (логическое отрицание)

Логический элемент "НЕ" имеет один вход и один выход. Условно обозначается в схемах:

Таблица истинности операции "НЕ" имеет вид:

X |

Y |

0 |

1 |

1 |

0 |

Логический элемент " НЕ" представляет собой усилительный каскад на транзисторе, включённом по схеме ОЭ и работает в ключевом режиме. На вход подаются положительные сигналы в положительной логике. Используется транзистор типа n-p-n (рис.3-12.).

Рис. 12-12. Электронная схема реализующая логический элемент "НЕ".

Допустим,

что транзистор VT

закрыт отрицательным потенциалом на

базе от -Еб. Если на "Вх"

подать низкий потенциал, соответствующий

"0"

,

то VT

остаётся закрытым, а при этом Iк=0

и

,

то VT

остаётся закрытым, а при этом Iк=0

и

![]() .

.

Следовательно, на выходе будет высокое напряжение соответствующее "I".

Если

на “Вх” подать высокий положительный

потенциал соответствующий "I",

то VT

будет в состоянии насыщения и.![]()

.Такой логический элемент еще называют "инвертором".

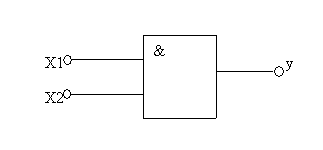

Логический элемент "И" (логическое умножение)

О бозначается

бозначается![]() .

Элемент имеет как минимум два входа и

один выход. Условное обозначение

элемента “И”:

.

Элемент имеет как минимум два входа и

один выход. Условное обозначение

элемента “И”:

Таблица истинности операции «И» имеет вид:

-

X1

X2

Y

0

0

0

0

1

0

1

0

0

1

1

1

Схема двухходового элемента «И» на биполярных транзисторах показана на рис 12-13.

Рис 12-13. Электронная схема, реализующая логический элемент «И».

Из схемы (рис 3-13) видно, что транзисторы VT1 и VT2 соединены последовательно и электрический ток может протекать тогда, когда открыты оба транзистора. В том случае, когда один из транзисторов будет закрыт, то на входе напряжение будет равно «0», что соответствует таблице истинности. Этот логический элемент называется конъюктор.

Логический элемент «ИЛИ» (логическое сложение)

Обозначается

.

.

Таблица истинности операции «или» имеет вид:

-

X1

X2

Y

0

0

0

0

1

1

1

0

1

1

1

1

Схема двухходового логического элемента «ИЛИ» показаны на рис 12-14.

Рис 12-14. Электронная схема, реализующая логический элемент «ИЛИ».

Схема элемента

«ИЛИ» выполнена на биполярных транзисторах

(технология транзисторно-транзисторной

логики). Если на входы

и

и

не подается напряжение, то TV1

и TV2 заперты и на

не подается напряжение, то TV1

и TV2 заперты и на

(на выходе) нет напряжения, и это

соответствует тому, что на выходе

логический «0». Если на один вход или на

оба входа подается положительное

напряжение (логическая «1»), то один или

оба транзистора открываются и на выходе

появляется положительное напряжение,

отображающее «1», что соответствует

таблице истинности. Этот логический

элемент еще называют дизъюнкцией.

(на выходе) нет напряжения, и это

соответствует тому, что на выходе

логический «0». Если на один вход или на

оба входа подается положительное

напряжение (логическая «1»), то один или

оба транзистора открываются и на выходе

появляется положительное напряжение,

отображающее «1», что соответствует

таблице истинности. Этот логический

элемент еще называют дизъюнкцией.

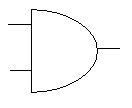

Логический элемент «И-НЕ» (отрицание умножения, штрих Шеффера)

Условное обозначение в схемах.

Таблица истинности операции “И-НЕ” имеет вид:

X1 |

X2 |

Y |

0 |

0 |

1 |

0 |

1 |

1 |

1 |

0 |

1 |

1 |

1 |

0 |

Рассмотрим схему «И-НЕ» (элемент Шеффера, рис 12-15)

Рис 12-15. Электронная схема, реализующая логический элемент «И-НЕ» (выполнена в ТТЛ).

Данная схема предназначен для работы от сигналов в виде напряжений, отрицательной полярности в отрицательной логике. (рис 3-15)

При отсутствии

сигналов на входах схемы,

и

заперты

положительным смещением

,

тока нет и на выходе

,

тока нет и на выходе

(то

есть «I»).Когда на входы

одновременно будут поданы

(то

есть «I»).Когда на входы

одновременно будут поданы

(

то есть «I») и

(

то есть «I») и ,

то V

и V

откроются и на выходе

,

то V

и V

откроются и на выходе

.Если

на ВхI подать «0», а на Вх2

–«1», то

будет заперт, а

открыт, тока в цепи нет и

(логическая «1»). Если на ВХ1 подать «1»,

а на ВХ2 – «0», то на выходе также

(логическая

«1»)

.Если

на ВхI подать «0», а на Вх2

–«1», то

будет заперт, а

открыт, тока в цепи нет и

(логическая «1»). Если на ВХ1 подать «1»,

а на ВХ2 – «0», то на выходе также

(логическая

«1»)

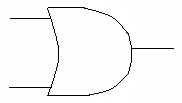

Логический элемент «ИЛИ-НЕ»(отрицание сложения, элемент Пирса)

Условное обозначение в схемах (логического элемента «ИЛИ-НЕ»

Таблица истинности логического элемента «ИЛИ-НЕ» :

-

X1

X2

Y

0

0

1

0

1

0

1

0

0

1

1

0

Рассмотрим схему элемента «ИЛИ-НЕ» (рис 12-16) :

Рис 12-16. . Электронная схема, реализующая логический элемент «ИЛИ-НЕ».

Схема (рис 12-16) работает от сигналов в виде напряжений отрицательной полярности в отрицательной логике. Схема выполнена на транзисторе и работает как логический элемент "НЕ" с несколькими входами (не менее двух).

При отсутствии на входах сигналов транзистор заперт положительным смещением +Еб на базе, тогда Iк=0 и Uвых = -Ек (т.е. "I"). Когда на любой из входов поступит сигнал Ubx = Uo (т.е. "I"), то транзистор отпирается и Uвых 0 (т.е. "О") и т.д. Здесь чаще всего используют МОП-транзисторы, т.к. у них высокая степень интеграции и повышенная помехоустойчивость.

Основываясь на законах алгебры логики можно любой логический элемент заменить устройством, собранных только на двухходовых элементах И-НЕ.

1). Операция НЕ,

,

,

РИС 12-17

Таблица истинности операции «НЕ».

-

у

0

0

1

1

1

0

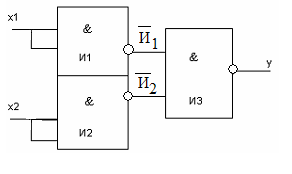

2). Операция И,

Таблица истинности операции «И».

Х1 |

Х2 |

И1 |

НЕ(у1) |

И2 |

НЕ (у) |

0 |

0 |

0 |

1 |

1 |

0 |

0 |

1 |

0 |

1 |

1 |

0 |

1 |

0 |

0 |

1 |

1 |

0 |

1 |

1 |

1 |

0 |

0 |

1 |

3). Операция «ИЛИ»,

Таблица истинности операции «ИЛИ».

Х1 |

Х2 |

И1 |

И2 |

И1 |

И2 |

И3 |

У(или) |

0 |

0 |

0 |

0 |

1 |

1 |

1 |

0 |

0 |

1 |

0 |

1 |

1 |

0 |

0 |

1 |

1 |

0 |

1 |

0 |

0 |

1 |

0 |

1 |

1 |

1 |

1 |

1 |

0 |

0 |

0 |

1 |

4). Операция сложения по модулю два (исключающее ИЛИ),

Таблица истинности операции «исключающее ИЛИ».

Х1 |

Х2 |

И1 |

И2 |

И1 |

И2 |

И3 |

И4 |

И3 |

И4 |

И |

НЕ(У) |

0 |

0 |

0 |

0 |

1 |

1 |

0 |

0 |

1 |

1 |

1 |

0 |

0 |

1 |

0 |

1 |

1 |

0 |

0 |

1 |

1 |

0 |

0 |

1 |

1 |

0 |

1 |

0 |

0 |

1 |

1 |

0 |

0 |

1 |

0 |

1 |

1 |

1 |

1 |

1 |

0 |

0 |

0 |

0 |

1 |

1 |

1 |

0 |

Триггеры в интегральном исполнении

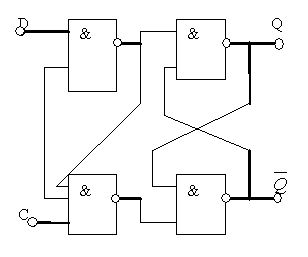

Обычно триггеры выполняют в виде интегральных микросхем. Такие триггеры состоят из логических элементов и блок-схема такого симметричного триггера со счетным входом изображена на рис. 12-18

Он состоит из алогических элементов «ИЛИ» (цепь запуска) и «НЕ» (однокаскадные усилители -инверторы), соединенных цепями перекрестной обратной связи.

Симметричный триггер работает следующим образом. Предположим, что на вход первого инвертора HE1 сигнал не подан - «О». В этом случае на его выходе появится сигнал «1». Этот сигнал, пройдя через логический элемент ИЛИ2, поступит на инвертор НЕ1. В результате на выходе инвертора НЕ2 установится напряжение, соответствующее «О». Сигнал «О» поступит на вход элемента ИЛИ1 а далее на вход инвертора HE1. Если учесть предположение, что входные сигналы триггера равны «О» то триггер все время будет находится в устойчивом состоянии. Это состояние изменится только тогда, когда на Bxl будет подан сигнал «1». Процесс перехода триггера в новое устойчивое состояние произойдет аналогично описанному выше.

Рис. 12-18 Блок-схема статического триггера.

Рис.123-19. Схема для установочного запуска триггеров.

Симметричные триггеры, применяемые в ЭВМ, должны отвечать следующим требованиям:

1.Триггер должен сохранять устойчивое состояние в реальных условиях эксплуатации ЭВМ, т.е. при суммарном воздействии всех дестабилизирующих факторов и помеховых импульсов.

2.При каждом воздействии запускающего импульса триггер должен бесперебойно срабатывать.

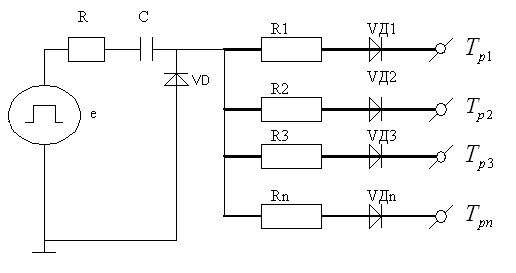

3.Триггер должен обладать заданной нагрузочной способностью, т.е. он должен нормально работать на нагрузку, включаемую по мере необходимости на выход триггера.В логических схемах ЭВМ, в устройствах памяти, регистрах, счетчиках, преобразователях кода и т.д. применяются цепочки из рядов последовательно - соединенных триггеров. Часто возникает необходимость возвратить всe триггеры данного ряда в исходное состояние, т.е. осуществить «сброс» триггеров. Это обычно производится при помощи одновременной подачи на входы всех триггеров данного ряда специального сбрасывающего (или установочного) импульса. Для этой цели используется один общий источник импульсов, работающий по схеме, приведенной на рис.3-19.

Резисторы R1, R2,..., Rn включаются для выравнивания токов во всех каналах запуска, диоды VД1,... VДn применяются для разделения цепей установочного запуска.

В случае применения триггеров со счетным входом установочный импульс может подаваться на коды триггеров после дифференцируемых емкостей.

Интегральная технология и использование методов алгебры логики позволили создать большое число различных триггеров на базе логических элементов, различающихся структурой цепей управления и режимами работы. Триггер состоит из цепей управления и запоминающих устройств и имеет один, два (или более) входа и два выхода. Каждый из входов имеет определенное функциональное назначение, которое отражается в обозначении данного входа (R, S, К, D и т. д.). Цепи управления, в которые поступают входные (информационные) сигналы, преобразуют их в сигналы для запоминания и считывания.

Запоминающие

устройства состоят из двух плеч, в каждом

из которых одновременно хранятся сколь

угодно долго два сигнала, один из которых

соответствует логической 1, другой —

логическому 0. Выход

триггера Q,

с которого в

исходном состоянии снимается высокий

потенциал, обычно называют прямым,

другой — инверсным (обозначается ).

).

Кроме симметричных триггеров в зависимости от выполняемых функций различают еще триггеры с раздельный запуском (RS-триггер), синхронный (RCS- триггер), со счетным запуском (Т-триггер), с элементами задержки или логическими переключающими схемами в цепях управления (D-триггер), универсальные JK-триггеры), на базе которых могут быть реализованы остальные типы триггеров.

По способу записи информации все триггеры подразделяют на асинхронные, в которых информация записывается непосредственно при поступлении входного сигнала, и тактируемые (синхронные), записывающие входную информацию только при поступлении разрешающего тактового импульса.

Названия триггеров составляют из типов входов. Синхронные триггеры бывают со статическими и динамическими входами. Динамическим называют такой вход, действие поданных уровней сигналов, на который прекращается после соответствующего переключения триггера. Рассмотрим примеры построения некоторых типов триггеров на базе логических элементов либо «ИЛИ — НЕ», либо «И — НЕ».

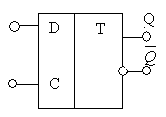

RC-триггер

Буквы R и S означают: R - раздельный вход установки в состояние О, S — раздельный вход установки в состоянии 1. Схема асинхронного RS триггера на двух логических элементах и его графическое обозначение в схемах показано на рисунке 12-20. Триггер имеет два прямых входа R и S и два выхода: прямой Q и инверсный . Перекрестная связь выхода каждого элемента ИЛИ — НЕ со входом другого обеспечивает схеме два устойчивых состояния. Предположим, что на входах R и S действуют уровни логического 0, не влияющие на состояние триггера. Примем для определенности, что на прямом выходе триггера Q имеет место уровень логического 0. Этот сигнал совместно с нулевым уровнем на входе S образуют на инверсном выходе триггера уровень логической 1. Уровень логической 1, в свою очередь, формирует совместно с 0,на входе R на прямом выходе Q уровень логического 0. Это устойчивое состояние триггера называют нулевым по уровню на прямом выходе.

Таблица истинности асинхронного RS триггера (С).

вход |

выход |

Режим работы |

|

||||

S |

R |

Q |

|

|

|||

0 |

0 |

0 |

1 |

хранение |

|

||

1 |

0 |

1 |

0 |

Запись 0 |

|

||

0 |

1 |

0 |

1 |

Запись 1 |

|

||

1 |

1 |

x |

x |

запрещено |

|

||

Рис12-20. Асинхронный RS триггер на двух логических элементах ИЛИ-НЕ, и его графическое обозначение.

Переключают триггер в другое состояние тподачей на один из входов сигнала логической 1, при подаче на вход R уровня 1, а на вход S уровня 0 на инверсном выходе устанавливается сигнал Q=0, который переводит триггер в состояние 1, соответствующее Q = 1. Аналогично происходит переключение триггера и при подаче уровня логической единицы на вход S.

Для RS-триггера существует запретная комбинация входных сигналов. Триггер теряет свойства (его состояние становится неопределенным) при одновременной подаче на входы R и S уровня логической 1. Если отпирающие импульсы действуют одновременно, то триггер оказывается временно в симметричном состоянии, из которого он может выйти равновероятно в любое из двух устойчивых состояний. Таким образом, результат неоднозначный, что недопустимо.

В схеме рис. 12-21 элементы «ИЛИ — НЕ» могут быть заменены элементами «И — НЕ». Свойства триггера при этом сохраняются, но управление им должно производиться уровнями логического 0. Такой триггер можно рассматривать как RS-триггер с инверсными входами. Более сложные триггеры D-, Т- и JK-типов выполняют на базе одного или двух RS-триггеров с использованием в цепях управления элементов задержки или логических переключающих схем. Наибольшее распространение получили триггеры с логическими переключающими схемами в цепях управления, поскольку интегральное исполнение элементов задержки затруднено.

Таблица истинности асинхронного RS триггера.

вход |

выход |

Режим работы |

|

|||

S |

R |

Q |

|

|

||

0 |

0 |

0 |

1 |

запрещено |

|

|

1 |

0 |

1 |

0 |

Запись 0 |

|

|

0 |

1 |

0 |

1 |

Запись 1 |

|

|

1 |

1 |

x |

x |

хранение |

|

|

рис. 12-21 Асинхронный RS триггер на двух логических элементах И-НЕ (a ) и его графическое изображение(б)

RCS-триггер (синхронный)

Если необходимо, чтобы триггер реагировал на изменение входного сигнала только в определённый интервал времени, то используют триггерные устройства с синхронизацией (рис.12-22).

Это - триггеры RSC - типа. Они имеют дополнительный синхронизирующий вход С.

Если С = 0 , то при любых значениях R и S сигналы на входах RS-триггера логические "1" и состояние RS-триггера не меняется.

Если C = 1,S=1,R = 0,to формируется нулевой сигнал на выходе Э1 и RS-триггер устанавливается в "1" (Q= 1, =0).

Если С = 1, S = 0, R = 1 , то появляется "0" на выходе Э2 и RS-триггер устанавливается в "0").

Значение входных сигналов S = 1,R=1,C=1 приводит к неопределенному состоянию устройства. Следовательно, такое состояние схемы является запрещенным.

в)

С |

S |

R |

Q |

|

Составляющие |

|

1 |

1 |

1 |

x |

x |

Запрещено |

|

1 |

1 |

0 |

0 |

1 |

Сост. 1 |

|

1 |

0 |

1 |

1 |

0 |

Сост . 2 |

|

0 |

1 |

0 |

0 |

1 |

не меняется |

|

0 |

0 |

1 |

0 |

1 |

не меняется |

|

Рис.12-22 Синхронный RCS-триггер (a) , графическое изображение(б) и таблица истинности(в)

D-триггер

D-триггер построен на логических элементах «И-НЕ» и изображен на рис 12-23.

Рис 12-23. Логическая схема D-триггер

D-триггер- это триггер, который повторяет на своем выходе состояние входа. Из рис 12-23 видно, что D-триггер можно образовать из RS-триггеров, если на их входы одновременно подавать инверсные сигналы. Информация в D-триггерах хранится за счет синхронизации и в этой связи D-триггеры имеют информационный вход D и вход синхронизации С. В описываемом триггере сигнал на входе передается на выход только по сигналу синхронизации и этот триггер называется триггером с запоминанием информации (триггер задержки).

Условное графическое обозначение D-триггера представлено на рис 12-24.

.

Рис 12-24. D-триггер в интегральном исполнении.

Таблица истинности D-триггера.

-

C

D

1

0

0

1

1

1

1

0

- логический уровень

на этом выходе после подачи импульса

синхронизации.

- логический уровень

на этом выходе после подачи импульса

синхронизации.

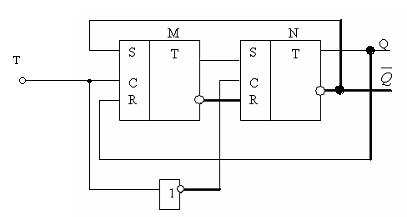

Т-триггер

Т-триггер состоит из двух синхронных RS-триггеров M и N, которые имеют синхронизирующие входы С и счетный вход Т и логический элемент НЕ (рис 12-25).

Рис 12-25. Т- триггер с синхронизирующим «С» входом в интегральном исполнении

Если ,

то на выходных триггера М будут такие

же сигналы, а на входе S

триггера М появится 1, (на выходе R=0).

При подаче сигнала «1» на Т автоматически

отключает триггер N от M

и в то же время обеспечивает запись в

него сигналов наS=1, наR=1.

При условии, что Т=0 обеспечивает

отключение триггера М и запись сигналов

с его выходов проходит в триггер N,

который переводится в состояние Q

= 0,

= 1. И тем самым переходит в состояние,

противоположное предыдущему.JK-триггер

,

то на выходных триггера М будут такие

же сигналы, а на входе S

триггера М появится 1, (на выходе R=0).

При подаче сигнала «1» на Т автоматически

отключает триггер N от M

и в то же время обеспечивает запись в

него сигналов наS=1, наR=1.

При условии, что Т=0 обеспечивает

отключение триггера М и запись сигналов

с его выходов проходит в триггер N,

который переводится в состояние Q

= 0,

= 1. И тем самым переходит в состояние,

противоположное предыдущему.JK-триггер

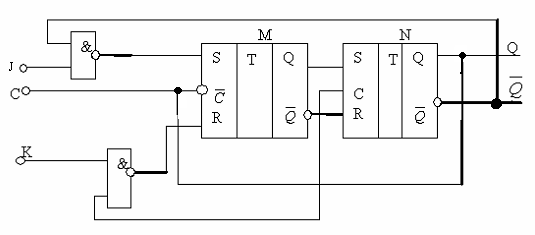

Э то

наиболее универсальный триггер, который

строится на основе двухступенчатого

RS-триггера и двух логических

элементов И-НЕ (рис 12-26).

то

наиболее универсальный триггер, который

строится на основе двухступенчатого

RS-триггера и двух логических

элементов И-НЕ (рис 12-26).

Рис 12-26. Схема JK-триггера в интегральном исполнении.

При комбинации сигналов если J=1 и K=0, то при Q=0 получают на S(триггер М) единицу. После подачи первого синхронизирующего импульса на С, триггер установится в состояние Q=1.

При комбинации сигналов J=1 и К=0,то при Q=1 на S и R (триггера М) будут равны “0” и при подаче синхронизирующего импульса на С, триггер не будет изменять своего состояния.

Таким же образом по отношению к состоянию Q=0 действует сигнал К=1 при J=0.

При комбинации сигналов J=K=1получают S=1 (триггер М) и R=0 (триггер М) при Q=0 и S=0(триггер М) и R=0 (триггер М) при Q=1. Таким образом триггер переключается в противоположное состояние при соответствующем фронте сигнала на С.

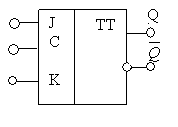

Условное графическое изображение JK-триггера показано на рис 12-27.

Рис 12-27. Условное графическое изображение JK-триггера

Таблица истинности JK-триггера.

-

J(t)

K(t)

Q(t+1)

Q(t+1)

Примечание

0

0

Q(t)

Q(t)

RS- режим

0

1

0

1

RS- режим

1

0

1

0

RS- режим

1

1

Q(t)

Q(t)

Режим Т триггера

Таблица получения из JK-триггерa. RS, T, D-триггеров

JK |

|

RS |

|

T |

|

D |

|