- •Список литературы………………………………………………………………………….

- •Тема 10. Транзисторные усилители электрических сигналов.

- •Тема 11. Нелинейные и параметрические преобразования сигналов.

- •Тема 12. Аналоговые и цифровые элементы и устройства. Аналоговые и цифровые ключи.

- •Тема 13. Комбинационные цифровые устройства.

- •Демультиплексор

- •Набор элементарных операций:

- •Тема 14. Дискретная и цифровая обработка сигналов.

- •Тема 15. Волоконно – оптические линии связи (волс)

- •Тема 9. Основы теории электронных приборов .

- •Тема 10. Транзисторные усилители электрических сигналов.

- •Тема 11. Нелинейные и параметрические преобразования сигналов.

- •Тема 12. Аналоговые и цифровые элементы и устройства. Аналоговые и цифровые ключи.

- •Тема 13. Комбинационные цифровые устройства.

- •Демультиплексор

- •Набор элементарных операций:

- •Тема 14. Дискретная и цифровая обработка сигналов.

- •Тема 15. Волоконно – оптические линии связи (волс)

- •Тема 9. Основы теории электронных приборов .

- •Тема 10. Транзисторные усилители электрических сигналов.

- •Тема 11. Нелинейные и параметрические преобразования сигналов.

- •Тема 12. Аналоговые и цифровые элементы и устройства. Аналоговые и цифровые ключи.

- •Тема 13. Комбинационные цифровые устройства.

- •Демультиплексор

- •Набор элементарных операций:

- •Тема 14. Дискретная и цифровая обработка сигналов.

- •Тема 15. Волоконно – оптические линии связи (волс)

Тема 13. Комбинационные цифровые устройства.

Передача и хранение информации проводится с помощью знаков, под которыми следует понимать совокупность признаков распознания какого-либо объекта или явления.

Сообщение – это последовательность знаков, которые содержат некоторую информацию.

Аналоговый сигнал – это такой сигнал, который принимает произвольные значения в любой момент времени

Импульсный сигнал – это такой сигнал, который в течение короткого промежутка времени изменяется от другого постоянного значения (дискретные значения).

С помощью импульсных сигналов можно составить сообщение, которое отображает дискретную или аналоговую информацию.

Кодирование информации – это представление сообщения в виде комбинаций из числа исходных знаков, а кодированные сигналы называют цифровыми сигналами.

В вычислительной технике используется код с основанием два, например, цифры 0 и 1 в двоичной системе счисления. Символу 1 соответствует положительный импульс напряжения, 0 – отрицательный или отсутствие импульса. В двоичных символах можно закодировать и передать любую информацию.

К математическим основам цифровой техники относятся системы счисления (СС). Системы счисления в зависимости от основания бывают: десятичные с основанием десять, восьмеричные с основанием восемь, двоичные с основанием два и т.д.

В цифровых устройствах используют элементы, которые имеют два устойчивых состояния и в этой связи двоичная система счисления чаще всего применяется для представления и обработки информации.

Все системы счисления разделяются на позиционные и непозиционные. Большое распространение для информационных систем получили позиционные системы счисления.

Позиционная

система счисления - это система

представления чисел, в которой

количественные значения каждой цифры,

входящий в запись числа зависит от

позиции в ряду цифр, представляющих

число. Позиционные системы счисления,

в которых для всех разрядов числа

используется одинаковое основание,

называются однородными. В однородной

позиционной системе счисления с

основанием «к» положительное число

М(к) записывают в виде последовательности

к-тых цифр:

,

где а – содержимое разряда; n-

номер разряда. Чтобы записать числа в

различных системах счисления используются

различные цифры: в 2СС (0;1), в 8СС

(0,1,2,3,4,5,6,7), в 16СС (0,1,2,3,4,5,6,7,8,9,A,B,C,D,E,F).

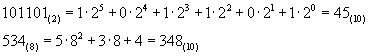

Согласно (1) приведём примеры записи

целых чисел в различных системах

счисления и перевода в десятичную

систему:

,

где а – содержимое разряда; n-

номер разряда. Чтобы записать числа в

различных системах счисления используются

различные цифры: в 2СС (0;1), в 8СС

(0,1,2,3,4,5,6,7), в 16СС (0,1,2,3,4,5,6,7,8,9,A,B,C,D,E,F).

Согласно (1) приведём примеры записи

целых чисел в различных системах

счисления и перевода в десятичную

систему:

Логические устройства подразделяются на комбинационные устройства и последовательные.

Комбинационные устройства – это устройства, в которых выходные сигналы в определённый момент времени определяются входными сигналами тот же момент времени.

Последовательное устройство – это устройство (конечный автомат) обязательно имеют элементы памяти.

Сумматоры

Сумматоры выполняют следующие операции:

сложение

вычитание

деление

умножение

вычисление тригонометрических функций

и т.д.

Различают последовательные и параллельные сумматоры.

Последовательные сумматоры производят суммирование разряд за разрядом.

Параллельные сумматоры производят суммирование по всем разрядам сразу.

В сумматоре предусматривается устройство, которое функционирует перенос в старший разряд.

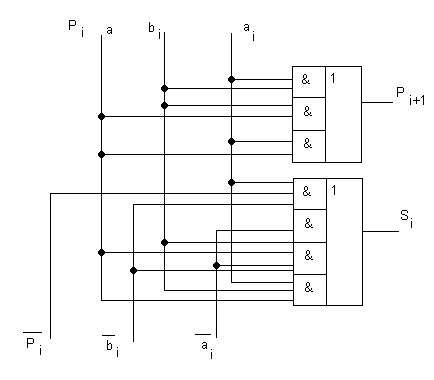

Рассмотрим схему полусумматора, представленного на рис 13-1.

Рис 13-1.Логическая схема полусумматора.

Этот

полусумматор обеспечивает существование

одноразрядных чисел при

и

=1.Значение младшего разряда сопровождается

переходом в старший разряд.

=1.Значение младшего разряда сопровождается

переходом в старший разряд.

Таблица истинности полусумматора

|

|

y(сумма) |

P(i + 1) |

0 |

0 |

0 |

0 |

0 |

1 |

1 |

0 |

1 |

0 |

1 |

0 |

1 |

1 |

0 |

1 |

Полный одноразрядный сумматор

Полный

одноразрядный сумматор складывает три

одноразрядных двоичных числа

,

, и

имеет два выхода (

и

имеет два выхода ( и

и

)

)

Действие этого сумматора можно описать следующими логическими функциями:

![]() (13

- 1)

(13

- 1)

Преобразуем (13-2) на основании законов алгебры логики.

(13-4)

(13-4)

Рис 13-2. Логическая схема полного одноразрядного сумматора.

Условное обозначение полного одноразрядного сумматора.

Таблица

истинности полного одноразрядного

сумматора.

Таблица

истинности полного одноразрядного

сумматора.

Pi |

ai |

bi |

S |

Pi+1 |

0 0 0 0 1 1 1 1 |

0 0 1 1 0 0 1 1

|

0 1 0 1 0 1 0 1 |

0 1 1 0 1 0 0 1 |

0 0 0 1 0 1 1 1 |

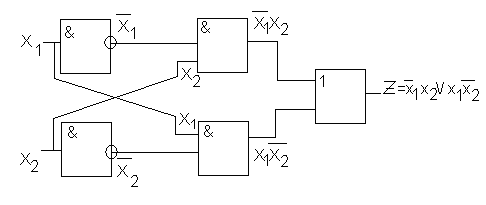

Сумматор по модулю два

Это устройство с двумя входами (x1, x2) и на выходе (Z) появится сигнал 1 в том случае, если на входы будут поданы сигналы 0 и 1. Этот Сумматор по модулю два называют схемой «исключающее ИЛИ!».

Рис13-3. Схема сумматора по модулю два.

Таблица истинности логической функции сумматора по модулю два.

X1 |

X2 |

Z |

0 0 1 1 |

0 1 0 1

|

0 1 1 0

|

(единица в следующий разряд)

Если составить функцию по единицам таблицы истинности, то можно получить

(13-5)

(13-5)

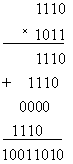

Умножители

Рассмотрим умножение двоичных чисел на конкретном примере:

Из примера видно, что умножение двоичных чисел выполняется достаточно просто, так как умножение производится на «1» и «0». При этом множитель сдвигается каждый раз влево на один разряд и затем они суммируются. Эту операцию можно реализовать с помощью регистра сдвига и сумматора.

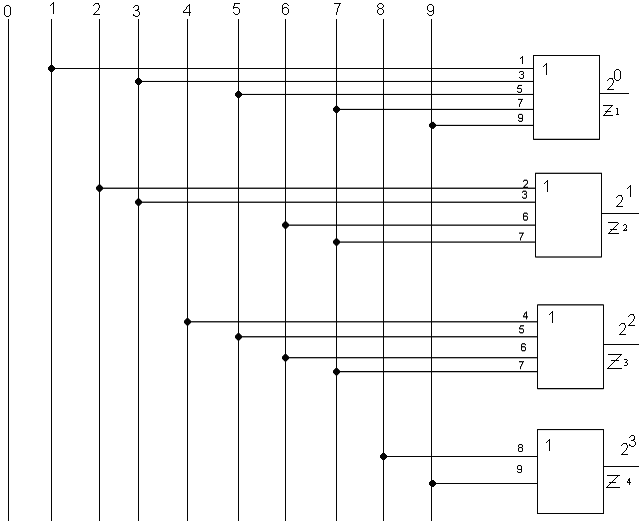

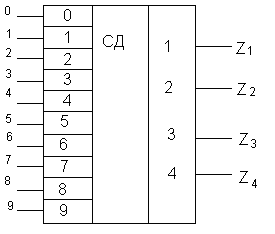

Шифраторы(СД)

Это комбинаторное цифровое устройство кодирования, преобразующие десятичные числа в двоичную систему счисления. Логически схема шифратора показана на рис. 13-3.

Допустим на пульте находится 10 клавиш (от 0 до 9) и при нажатии одной из клавиш подается единичный сигнал x0,x1,..,x9, а на входе появится двоичный код.

Следовательно необходим в данном случае преобразователь, имеющий 10 входов и 4 выхода.

На входе должна появится «1» при нажатии любой нечетной клавиши.

Для остальных цифр кодирование смотри логическую схему шифратора.

Если подать сигнал на один из входов шифратора, то на выходе должен появиться двоичный код.

В том случае, если число входов составляет 2 n, то число выходов должно быть «n»и равно числу разрядов двоичного кода. Этим кодом можно закодировать 2 n ситуаций. На рис. 13-3 показана логическая схема шифратора при n=3.

Рис 13-3. Логическая схема шифратора.

Действие шифратора можно описать следующими логическими функциями:

Как видно из (13-6) три функции реализуются тремя дизъюнкторами, на входах которых образуется трёхразрядный двоичный код.

Условное обозначение шифратора.

Таблица истинности шифратора

|

Z 4 |

Z 3 |

Z 2 |

Z 1 |

0 |

0 |

0 |

0 |

0 |

1 |

0 |

0 |

0 |

1 |

2 |

0 |

0 |

1 |

0 |

3 |

0 |

0 |

1 |

1 |

4 |

0 |

1 |

0 |

0 |

5 |

0 |

1 |

0 |

1 |

6 |

0 |

1 |

1 |

0 |

7 |

0 |

1 |

1 |

1 |

8 |

1 |

0 |

0 |

0 |

9 |

1 |

0 |

0 |

1 |

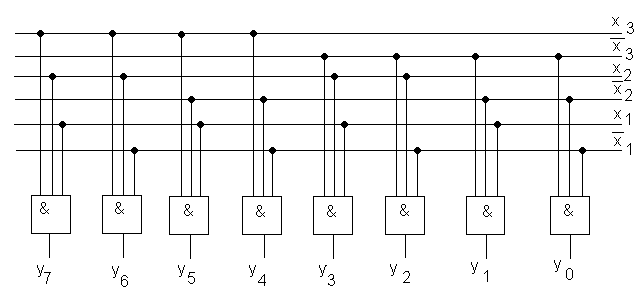

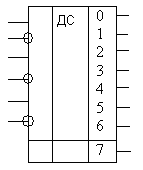

Дешифраторы

Дешифратор-это узел, преобразующий код, поступающий на его входы в сигнал только на одном из его выходов.

Дешифратор двоичного n-разрядного кода имеет 2 n-выходов в связи с тем, что каждому из двух значений входного кода должен соответствовать единичный сигнал на одном из выходов дешифратора.

Рассмотрим схему линейного дешифратора на три входа (рис 13-4)

Рис 13-4. Логическая схема дешифратора.

Таблица истинности для дешифратора сможет быть представлена такой же как для шифратора только наоборот. Распознавание дешифратора двоичных чисел состоит в том, что в зависимости от номера набора, поступившего на его вход сигнал «1», появится на одном определенном выходе (остальные выходы дадут «0»)

Таблица истинности для данного линейного дешифратора на 3 входа: (2 3 = 8 выходов)

(полный дешифратор 3-х разрядных чисел)

-

№

набора

Входы

Выходы

X1

X2

X3

Y0

Y1

Y2

Y3

Y4

Y5

Y6

Y7

0

1

2

3

4

5

6

7

0

0

0

0

1

1

1

1

0

0

1

1

0

0

1

1

0

1

0

1

0

1

0

1

1

0

0

0

0

0

0

0

0

1

0

0

0

0

0

0

0

0

1

0

0

0

0

0

0

0

0

1

0

0

0

0

0

0

0

0

1

0

0

0

0

0

0

0

0

1

0

0

0

0

0

0

0

0

1

0

0

0

0

0

0

0

0

1

Рассмотрение данной схемы (рис 13-4) показывает, что каждая из функций представляет конъюнкцию 3-х переменных и может быть реализована с помощью 3-х ходовых схем логического элемента «И».

Следует заместитель, что бывают дешифраторы с синхронизирующим входом, при котором дешифрация кода будет произведена во время подачи синхронимпулься, который поступает на вход синхронизации(обычно обозначается «с»). Кроме того, еще должен быть управляющий единичный сигнал.

Действие дешифратора можно описать следующими восьмью логическими функциями (трёхразрядный дешифратор имеет 2 3 = 8 выходов)

(13-7)

(13-7)

Очевидно, что в код входного числа входят сигналы «1» и «0», но логическое «И» не реагирует на сигнал «0». В этой связи в качестве источников сигналов «0» используют, например, сигналы с инверсных выходов триггеров.

Условное обозначение 3-х линейно дешифратора.

Преобразование кодов

Общие понятия:

Преобразователи кодов – это устройства для автоматического изменения по заданному алгоритму для соответствия между входными и выходными кодами без изменения их смыслового содержания.

1 тип:

Элементы входного кода соответствует элементу выходного кода.

Здесь эту роль выполняют последовательно-параллельные регистры. Такое устройство с объектом по двух проводному каналу на выходе передатчика строит преобразование параллельного кода в последовательный на выходе и наоборот.

2 тип:

Элементы выходного кода не соответствуют элементам входного. В этом случае процесс происходит в 2 этапа:

1)сначала входной n-разрядный код преобразовывается в промежуточный дешифратор

2)промежуточный дешифратор преобразуется в требуемый n-разрядный код шифратором.

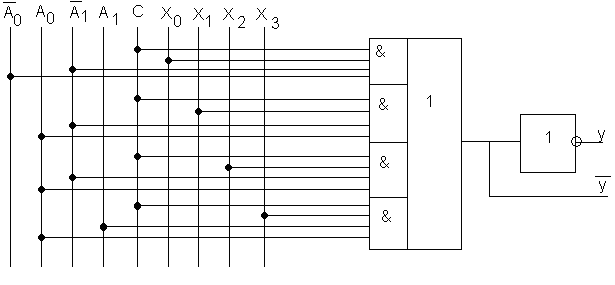

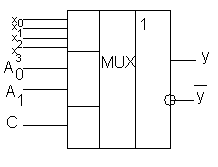

Мультиплексоры(коммутаторы)

Мультиплексор (MUX) – это комбинационное цифровое устройство, которое осуществляет коммутацию двоичного сигнала Хn с одного из n-входов на всего один выход. Процесс происходит в присутствии С-синхронизируещего импульса, а номер входа «n", подключаемого к выходу определяется сигналами А0, А1 и т.д. на так называемых адресных входах. (Адрес – это двоичная запись номера «n» коммутируемого входа).

Мультиплексор – это узел, осуществляющий преобразования параллельных цифровых кодов в последовательные.

Рассмотрим схему мультиплексора с синхронизирующим входом «С» (рис. 13-5)

Рис13-5. Логическая схема мультиплексора с синхронизирующим входом «С»

Условное обозначение мультиплексора

Таблица истинности мультиплексора

A1 |

A0 |

C |

Y |

любые |

0 1 1 1 1

|

0 x1 x2 x3 x4 |

|

0 0 1 1

|

0 1 0 1 |

||

Формула перехода мультиплексора для выхода y:

(13-8)

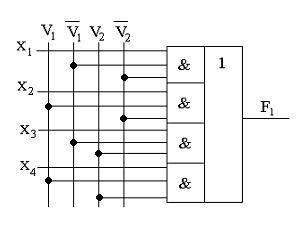

Мультиплексор – это узел, осуществляющий преобразование параллельных цифровых кодов в последовательные. Рассмотрим схему мультиплексора без синхронизирующего входа (рис 13-6).

Рис. 13-6 . Логическая схема мультиплексора без синхронизирующего входа.

Действие мультиплексора без синхронизирующего входа можно описать следующей логической функцией F1:

(13-9)

Таблица истинности мультиплексора без синхронизирующего входа

i |

V2 |

V1 |

X1 |

X2 |

X3 |

X4 |

F1 |

1 |

0 |

0 |

0 |

|

|

|

0 |

0 |

0 |

1 |

|

|

|

1 |

|

2 |

0 |

1 |

|

0 |

|

|

0 |

0 |

1 |

|

1 |

|

|

1 |

|

3 |

1 |

0 |

|

|

0 |

|

0 |

1 |

0 |

|

|

1 |

|

1 |

|

4 |

1 |

1 |

|

|

|

0 |

0 |

1 |

1 |

|

|

|

1 |

1 |