- •І.М. Черненко, о.І. Івон

- •Електронні елементи та вузли комп'ютерів

- •Дніпропетровськ, 2009

- •Передмова

- •Перелік вживаних скорочень

- •1.1. Загальні відомості, визначення

- •1.2. Способи представлення сигналів в обчислювальних пристроях. Системи числення.

- •Контрольні запитання

- •Розділ 2. Електронні ключі

- •2.1. Основні поняття. Класифікація, вимоги

- •2.2. Ключі на біполярних транзисторах

- •2.3 Ключі на польових (уніполярних) транзисторах

- •Контрольні запитання

- •Цифрової техніки

- •3.1 Математичні основи функціонування елементів та вузлів комп’ютерної електроніки

- •Контрольні запитання

- •4.1. Загальні поняття. Умовне зображення логічних елементів

- •4.2 Параметри елементів цифрової електроніки

- •4.3 Базові логічні елементи транзисторно-транзисторної логіки Шотткі (ттлш)

- •4.4 Базові логічні елементі на мон-транзисторах

- •4.5 Логічні елементи на польових транзисторах структури „метал-напівпровідник” з бар’єром Шотткі

- •Контрольні запитання

- •5.1 Загальні поняття і класифікація тригерів

- •5.2 Параметри тригерів

- •5.3 Асинхронні і синхронні rs-тригери

- •5.4 Асинхронні і синхронні d-тригери

- •5.5. Асинхронні і синхронні jk-тригери

- •5.7. Несиметричний тригер (тригер Шмітта)

- •5.8 Приклади використання тригерів

- •Контрольні запитання

- •Цифрових пристроїв

- •6.1. Інтегрувальні та диференціювальні

- •Сигналів на логічні елементи

- •6.2. Формувачі

- •6.3. Генератори поодиноких імпульсів (одновібратори)

- •6.4. Генератори (мультивібратори)

- •Контрольні запитання

- •7.1 Основні поняття, класифікація

- •7.2 Комбінаційні функціональні вузли

- •7.3. Комбінаційні арифметичні вузли

- •7.4. Послідовнісні вузли

- •Контрольні запитання

- •Та їх елементи

- •8.1 Основні поняття, класифікація

- •8.2 Параметри запам’ятовуючих пристроїв

- •8.3 Структури адресних запам’ятовуючих пристроїв

- •8.4. Динамічні запам’ятовуючі пристрої та їх елементи

- •8.5. Статичні запам’ятовуючі пристрої та їх елементи

- •8.6. Постійні запам’ятовуючі пристрої та їх елементи

- •Контрольні запитання

- •Список літератури Список основної літератури

- •Список рекомендованої літератури

5.5. Асинхронні і синхронні jk-тригери

5.5.1. Асинхронний JK-тригер. Цей тригер подібно до асинхронного RS-тригера має два інформаційні входи J, K і перемикається згідно таблиці справжності RS-тригера з прямими входами (рис. 5.4а), якщо J ≡ S, а K ≡ R, але на відміну від RS-тригера не має невизначеного стану. Виключення невизначеного стану у JK-тригері забезпечується його перемиканням при комбінації сигналів J = K = 1 у стан інверсний тому, який він мав до надходження цієї комбінації сигналів. Таблиці справжності JK-тригера у скороченому і розширеному вигляді, його умовне зображення на принципових електричних схемах і діаграма Вейча наведені на рис. 5.29.

Як випливає з діаграми Вейча (рис. 5.29г), побудованої на підставі розширеної таблиці справжності (рис. 5.29б), після склеювання одиниць, можна отримати наступне логічне рівняння для асинхронного JK-тригера:

Qn+1

= Jn![]() +

+

![]() Qn. (5.28)

Qn. (5.28)

Для визначення його логічної структури в базисі Шеффера ІНЕ, як і у випадку асинхронного DV-тригера (див. підрозділ 5.4.1), використаємо в якості бістабільної комірки асинхронний RS-тригер з інверсними входами , (рис. 5.7а). Для такого тригера методами алгебри логіки синтезуємо схему пристрою керування, яка забезпечує перемикання RS-тригер згідно таблиці справжності асинхронного JK-тригера (рис. 5.29а,б).

Jn

Kn

Qn+1

0

0

Qn

0

1

0

1

0

1

1

1

|

|

|||||||||||||||||||||||||||||||||||||||||||||||||||

а |

б |

|||||||||||||||||||||||||||||||||||||||||||||||||||

|

|

|||||||||||||||||||||||||||||||||||||||||||||||||||

в |

г |

|||||||||||||||||||||||||||||||||||||||||||||||||||

Рис. 5.29. Асинхронний JK-тригер: а – скорочена таблиця справжності; б – розширена таблиця справжності; в – умовне графічне зображення; г – діаграма Вейча

|

||||||||||||||||||||||||||||||||||||||||||||||||||||

Таблиця справжності для функцій виходу пристрою керування , , яка побудована з урахуванням таблиць справжності асинхронних RS-тригера (рис. 5.7в) і JK- тригера (рис. 5.29б), наведена на рис. 5.30. Мінімізація булевих функцій , методом діаграм Вейча (рис. 5.31) приводе до наступних рівнянь:

Jn

|

|||||||||||||||||||||||||||||||||||||||||||||

Рис. 5.30. Таблиця справжності пристрою керування асинхронного JK-тригера в базисі ІНЕ |

= + Jn . (5.30)

З (5.29), (5.30) випливає, що функції виходу пристрою керування асинхронного JK-тригера залежать від його вихідних змінних Qn та , а це означає, що в схемі такого тригера має місце зворотний зв’язок між його виходами і входами.

Для переходу до базису Шеффера ІНЕ застосуємо до (5.29) та (5.30) закон де Моргана. В результаті отримаємо наступні логічні рівняння:

![]() , (5.31)

, (5.31)

![]() . (5.32)

. (5.32)

З них випливає, що для побудови схеми пристрою керування потрібні чотири елемента 2ІНЕ, а схема асинхронного JK-тригера має вигляд показаний на рис. 5.32.

|

Рис.

5.31. Результати мінімізації функцій

виходів

|

|

Рис. 5.32. Схема асинхронного JK-тригера в базисі Шеффера ІНЕ |

Нехай початково

на входах JK-тригера сигнали J=0, K=1, які

забезпечують нульовий стан тригера Q =

0,

= 1, а в точках його схеми на рис. 5.32

встановлюють наступні рівні сигналів:

![]() = 1,

= 1,

![]() = 1,

= 1,

= 0. Зазначимо, що при незмінних у часі

сигналах J=0, K=1 цей стан тригера є

стабільним, оскільки вихідні сигнали

тригера, що надходять по зворотним

зв’язкам не змінюють сигнали

= 1,

= 0 на входах бістабільної комірки

(RS-тригер на логічних елементах DD3, DD6).

= 1,

= 1,

= 0. Зазначимо, що при незмінних у часі

сигналах J=0, K=1 цей стан тригера є

стабільним, оскільки вихідні сигнали

тригера, що надходять по зворотним

зв’язкам не змінюють сигнали

= 1,

= 0 на входах бістабільної комірки

(RS-тригер на логічних елементах DD3, DD6).

|

Рис. 5.33. Часові діаграми асинхронного JK-тригера |

Коли в момент часу t0 на вхід J надходить сигнал логічної одиниці J = 1 (при збереженні K = 1) в схемі тригера, з затримками на інтервал часу tзп, починається перемикання логічних елементів 2ІНЕ. Послідовність і напрямок таких перемикань на рис. 5.33 показані лініями зі стрілками. Першими з затримкою на tзп перемикаються елементи DD2, DD4, на входах яких в момент часу t0 з’являються одиниці, що забезпечує стан виходів цих елементів = 0, = 0. Ці рівні логічних сигналів у свою чергу з затримкою на tзп викликають перемикання елементів DD3, DD5, що забезпечує Q = 1, = 1. Встановлення JK-тригера у стан Q = 1 = 0, завершується у момент часу t1 перемиканням логічного елемента DD6 в нульовий вихідний стан ( = 0), оскільки на його входах з моменту часу t1 tзп діють сигнали логічної одиниці. Однак, як можна бачити з часових діаграм на рис. 5.33 перемикання JK-тригера на цьому не завершується, тобто новий, інверсний попередньому, стан тригера не фіксується. Це обумовлено тим, що логічна одиниця з виходу елемента DD3 (Q = 1), що надходить по зворотному зв’язку на вхід елемента DD1, викликає в момент часу t1 перемикання = 0, наслідком чого є подальша низка перемикань логічних елементів 2ІНЕ схеми JK- тригера, яка завершується в момент часу t3 встановленням нового стану тригера.

Таким чином, при комбінації сигналів J = K = 1 стан асинхронного JK-тригера, схема якого наведена на рис. 5.32, змінюється на інверсний через інтервали часу, що дорівнюють тривалості затримки перемикання тригера tз.пер = 4tзп. На виході JK-тригера має місце паразитна генерація, частота якої дорівнює f = 1/(8tзп). Звернемо увагу ще на одну особливість перемикання асинхронного JK-тригера, яка випливає з часових діаграм (рис. 5.33). Це явище ризику збою, що спостерігається у інтервалах часу t2t3, t4t5, t6t7, як однакові рівні сигналу на прямому і інверсному виходах тригера Q = = 1.

Отже завдяки паразитній генерації асинхронні JK-тригери можна використовувати лише при керуванні імпульсами, тривалість яких задовольняє певній умові. У цьому випадку, для запобігання паразитної генерації, після перемикання тригера сигналами J = K = 1 у стан інверсний попередньому, його треба перевести у стан зберігання інформації сигналами J = 0, K = 0. Це накладає обмеження на тривалість імпульсних сигналів високого рівня напруги (логічної „1”) tім.JK на інформаційних входах JK-тригера. Зокрема для схеми JK-тригера наведеної на рис. 5.32, з урахуванням часових діаграм на рис. 5.33, такі обмеження визначає умова: 4tзп < tім.JK < 7tзп.

Жорсткі часові співвідношення, які накладаються на тривалість керуючих імпульсних сигналів у асинхронних JK-тригерах, ускладнюють схеми на їх основі. Тому асинхронні JK-тригери в інтегральному виконанні не випускають. До складу серій інтегральних мікросхем входять лише синхронні JK-тригери, для яких знайдені схемотехнічні реалізації, що дозволяють подолати паразитну генерацію.

Сn

|

|

||||||||||||||||||||||||

а |

б |

||||||||||||||||||||||||

Рис. 5.34. Синхронний JK-тригер зі статичним керуванням: а – таблиця справжності; б – умовне графічне зображення |

|||||||||||||||||||||||||

Qn+1 = Qn + CnJn + Cn Qn. (5.33)

В комп’ютерній електроніці JK-тригери зі статичним керуванням не використовують завдяки їх підвищеній чутливості до перешкод і паразитній генерації, що виникає при наявності на входах сигналів C = 1, J = 1, K = 1. Використовуються синхронні JK-тригери з динамічним керуванням, які створюють за двоступеневою схемою або з внутрішніми затримками, що дозволяють подолати паразитну генерацію.

Схема двоступеневого синхронного JK-тригера, який має так звані заборонні зв’язки, показана на рис. 5.35. В цій схемі ведучий тригер на елементах DD2, DD6 має схему пристрою керування на елементах DD1, DD5, а ведений тригер на елементах DD4, DD8 – схему керування на елементах DD3, DD7. Заборонні зв’язки організовані між виходами схеми керування ведучого тригера і входами схеми керування веденого тригера.

При

наявності на вході С сигналу низького

рівня напруги U0

(С = 0) на виходах схеми керування ведучого

тригера (елементи DD1,

DD5),

не залежно від стану входів J

і K,

діють сигнали високого рівня напруги

U1

логічної одиниці (

= 1,

= 1). Тому ведучий тригер знаходиться у

стані зберігання інформації і запис

інформації у JK-тригер

блокований. Пасивні для елемента ІНЕ

сигнали логічної одиниці надходять

через заборонні зв’язки на входи схеми

керування веденого тригера (елементи

DD3,

DD7)

і дозволяють перезапис інформації з

ведучого у ведений тригер. Дійсно, якщо

ведучий тригер знаходиться у стані,

= 1,

![]() = 0, то на всіх входах елемента DD3

є логічні одиниці, що забезпечує на його

виході

= 0, а активний сигнал

логічний нуль з виходу DD6

забезпечує

= 1. На входах веденого тригера комбінація

сигналів

= 0,

= 1, яка (див.

таблицю справжності на рис. 5.7в)

встановлює цей тригер, а тому і JK-тригер

у стан Q

= 1,

= 0, тобто ведений тригер повторює стан

ведучого тригера.

= 0, то на всіх входах елемента DD3

є логічні одиниці, що забезпечує на його

виході

= 0, а активний сигнал

логічний нуль з виходу DD6

забезпечує

= 1. На входах веденого тригера комбінація

сигналів

= 0,

= 1, яка (див.

таблицю справжності на рис. 5.7в)

встановлює цей тригер, а тому і JK-тригер

у стан Q

= 1,

= 0, тобто ведений тригер повторює стан

ведучого тригера.

|

Сn

Jn

Kn

Qn+1

0

1

Qn

0

0

Qn

0

1

0

1

0

1

1

1

|

||||||||||||||||||||||||

а |

б |

||||||||||||||||||||||||

Рис. 5.35. Синхронний JK-тригер з керуванням зрізом імпульсу: а схема; б – таблиця переходів

|

|||||||||||||||||||||||||

Нехай тепер при одиничному стані JK-тригера Q = 1, = 0 ( = 1, = 0) та сигналах на інформаційних входах J = 1, K = 1, на вхід синхронізації надходить сигнал високого рівня С = 1 (перепад напруги від U0 до U1). Тоді логічні одиниці на входах елемента DD5 забезпечують на його виході логічний нуль, тобто = 0. Логічний нуль з виходу , що надходить по зворотному зв’язку на відповідний вхід елемента DD1, забезпечує = 1. На входах ведучого тригера комбінація сигналів = 1, = 0, яка перемикає його у нульовий стан = 0, = 1. При цьому стан веденого тригера (Q = 1, = 0) не змінюється оскільки логічний нуль ( = 0) з виходу DD5 надходить через заборонний зв’язок на входи пристрою керування веденого тригера (елементи DD3, DD7) і забороняє перезапис інформації з ведучого тригера в цей тригер, переводячи його сигналами = 1, = 1 у стан зберігання інформації. З вищевикладеного випливає, що при статичному рівні сигналу на вході синхронізації C = 1, стан JK-тригера остається незмінним при зміні сигналів на інформаційних входах J і K, оскільки перезапис інформації із ведучого тригера у ведений блокована логічним нулем, який надходить на входи схеми керування веденим тригером. Для перезапису інформації необхідно на вхід С подати логічний нуль, тобто перепад напруги від високого U1 до низького U0 рівня. Тому двоступенева схема синхронного JK-тригера (рис. 5.35а) має зворотне динамічне керування – керування зрізом імпульсу. Таблиця переходів для такого тригера наведена на рис. 5.35б.

Зазначимо, що у синхронному JK-тригері з двоступеневою структурою запобігання паразитної генерації при подачі сигналів J = 1, K = 1 на інформаційні входи тригера забезпечується блокуванням перезапису інформації із ведучого тригера до веденого при статичному рівні сигналу на вході синхронізації С = 1 і блокуванням запису інформації у ведучий тригер при С = 0.

Електрична принципова схема двоступеневого синхронного JK-тригера КМОНТЛ показана на рис. 5.36. В цій схемі ведучий RS-тригер з інверсними входами , реалізовано на базових логічних елементах 2ІНЕ за схемою показаною на рис. 5.8 (транзистори VT8, VT12VT14, VT18VT20, VT22), а ведений тригер зі входами , реалізовано за такою ж схемою на транзисторах VT7, VT9VT11, VT15VT17, VT21.

Схему пристрою керування ведучого тригера утворюють два базових логічних елемента 3ІНЕ (транзистори VT1, VT4VT6, VT26VT29, VT31, VT32), які мають спільний КМОН-ключ на транзисторах VT29 і VT32. Відповідно до схеми ці логічні елементи формують керуючі сигнали на інформаційних входах , ведучого тригера згідно сигналам, які надходять на входи двоступеневого синхронного JK-тригера J, K, C і сигналам з виходів тригера Q, , що приходять по зворотним зв’язкам. Схема пристрою керування веденого тригера реалізована на двох логічних елемента 2ІНЕ (транзистори VT2, VT3, VT23VT25, VT30), які також мають спільний ключ на транзисторах VT25, VT30. На входи цієї схеми надходять сигнали з виходів , ведучого тригера і інверсне значення сигналу синхронізації , що формується інвертором КМОНТЛ, який на схемі рис. 5.36 не показано.

|

Рис. 5.36. Електрична принципова схема двоступеневого синхронного JK-тригера комплементарної МОН-транзисторної логіки

|

Отже в схемі синхронного JK-тригера на рис. 5.36 перезаписом інформації від ведучого до веденого тригера керують не заборонні зв’язки, як в схемі JK-тригера розглянутій вище (рис. 5.35), а інвертор, подібно до схеми синхронного RS-тригері на рис. 5.14. При наявності на вході низького рівня напруги U0 ( = 0) логічні елементи схеми пристрою керування веденого тригера формують на його входах , сигнали високого рівня напруги U1 ( = 1, = 1), які не залежно від сигналів , з виходів ведучого тригера відкривають транзистори VT10, VT16 і закривають VT7, VT21. В результаті стан веденого тригера не змінюється, тобто сигнал низького рівня на вході = 0 „від’єднує ” ведений тригер від ведучого.

Розглянемо роботу схеми синхронного двоступеневого JK-тригера (рис. 5.36), коли на його інформаційних входах J і K діють сигнали високого рівня U1 (J = 1, K = 1), критичні з точки зору виникнення паразитної генерації. Припустимо, що початково ведучий і ведений тригери встановлені у нульовий стан, тобто = 0 (U0), = 1 (U1), Q = 0 (U0), = 1 (U1). При надходженні сигналу високого рівня U1 на вхід синхронізації (С = 1) сигнал низького рівня U0 ( = 0) „від’єднує” ведений тригер від ведучого і він зберігає записану в нього інформацію Q = 0 (U0), = 1 (U1). Сигнали високого рівня напруги U1 на входах J, C і сигнал такого ж рівня, що надходить по зворотному зв’язку з виходу , відкривають транзистори VT27, VT28, VT29 і закривають транзистори VT26, VT31, VT32. Вхід ведучого тригера підключається до землі і від’єднується від шини живлення. На ньому встановлюється низькій рівень напруги U0 ( = 0). Одночасно, хоча K = 1 (U1), низький рівень напруги U0, що надходить по зворотному зв’язку з виходу веденого тригера Q закриває транзистор VT5 і відкриває VT4. Це, за рахунок підключення входу ведучого тригера до шини живлення і відключення його від землі, забезпечує високий рівень напруги U1 ( = 1).

На інформаційних входах ведучого тригера встановлюється комбінація сигналів = 0, = 1, яка перемикає цей тригер у стан = 1, = 0. Дійсно, низький рівень напруги U0 зі входу закриває транзистор VT19 і відкриває VT22, що підключає до шини живлення і відключає від землі, тобто на цьому виході встановлюється напруга високого рівня U1 ( = 1). Одночасно високий рівень напруги U1 зі входу закриває VT8 і відкриває VT13, а високий рівень U1, що надходить зі стоку VT19 по зворотному зв’язку ведучого тригера закриває VT12 і відкриває VT14. На виході , відключеному від шини живлення закритими транзисторами VT8, VT12 і підключеному до землі відкритими VT13, VT14, встановлюється низький рівень напруги логічного нуля U0, тобто = 0.

Після перемикання ведучого тригера у стан інверсний попередньому, ведений тригер залишається у попередньому стані Q = 0 (U0), = 1 (U1), оскільки перезапис інформації до нього з ведучого тригера блоковано сигналом низького рівня U0 на вході . Будь-які зміни сигналів на інформаційних входах J, K при С = 1 (U1) змінюють тільки стан ведучого тригера, а стан веденого тригера, а тому і стан виходів Q, JK-тригера залишається незмінним. Тому при статичному рівні сигналу U1 на вході синхронізації С (С = 1) JK-тригер, принципова схема якого наведена на рис. 5.36, знаходиться у стані зберігання інформації.

Для перезапису інформації з ведучого до веденого тригера на вхід С треба подати сигнал низького рівня U0 (С = 0), тобто перепад напруги від U1 до U0. При цьому сигнал високого рівня U1 на вході ( = 1) відкриває транзистор VT25 і закриває VT23, а сигнал високого рівня U1, який надходить з прямого виходу ведучого тригера відкриває VT24 і закриває VT23. На вході , відключеному від шини живлення і підключеному до землі, встановлюється низький рівень напруги U0 ( = 0). Одночасно сигнал низького рівня U0, який надходить з інверсного виходу ведучого тригера відкриває транзистор VT2 і закриває VT3, що створює на вході веденого тригера високий рівень напруги U1 ( = 1). Комбінація сигналів = 0, = 1, таким же чином, як було вище показано для ведучого тригера, перемикає ведений тригер, а тому й синхронний JK-тригер у той же стан, що має ведучий тригер, тобто Q = 1, = 0. Відзначимо, що при низькому статичному рівні напруги U0 логічного сигналу на вході С (С = 0), як було показано вище, ведучий тригер знаходиться у стані зберігання інформації, оскільки на його інформаційних входах діють сигнали високого рівня U1 ( = 1, = 1). Тому синхронний JK-тригер, (рис. 5.36) не змінює свій стан при статичному рівні сигналу С = 0 для будь-якої комбінації сигналів на його інформаційних входах J і K.

З урахуванням викладеного вище можна зробити висновок, що розглянутий синхронний JK-тригер не змінює стан при статичних рівнях нуля і одиниці, а також при перепаді напруги від U0 до U1 на вході синхронізацій С і перемикається при наявності на цьому вході перепаду напруги від U1 до U0 . Тому такий тригер має зворотне динамічне керування (керування зрізом імпульсу) і описується таблицею переходів наведеною на рис. 5.35б.

Двоступеневі синхронні JK-тригери входять до складу серій мікросхем ТТЛШ і КМОНТЛ. Їх випускають, як комбіновані JKRS-тригери. Входи попередньої установки в них створюють шляхом організації безпосередніх зв’язків з входами веденого тригера. На рис. 5.35а такі зв’язки показані пунктирними лініями. Входи попередньої установки , (або S, R) мають більш високий пріоритет ніж інші входи комбінованого тригера і дають можливість керувати його станом незалежно від сигналів на інших входах.

Прикладом комбінованого JKRS-тригера КМОНТЛ з двоступеневою структурою є мікросхема КР1561ТВ1 (функціональний аналог CD4027BM) (рис. 5.37а).

|

Sn

Rn

Cn

Jn

Kn

Qn+1

Режим

0

1

0

Асинхронний

1

0

1

1

1

н/в

0

0

0

1

Qn

Зберігання

0

0

0

0

Qn

0

0

0

1

0

Синхронний

0

0

1

0

1

0

0

1

1

|

||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

а |

б |

||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

Рис. 5.37. Мікросхема КР1561ТВ1: а – умовне зображення; б – таблиця переходів

|

|||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

До складу мікросхеми входять два синхронних JK-тригера з керуванням фронтом імпульсу і прямими входами попередньої установки. З таблиці переходів (рис. 5.37б) випливає, що мікросхема може працювати у трьох режимах. У асинхронному режимі, незалежно від стану входів J, K і С тригер перемикається логічною одиницею на входах S, R, як асинхронний RS-тригер. Синхронний режим реалізується при S = R = 0, коли тригер перемикається перепадом напруги згідно таблиці справжності асинхронного JK-тригера, а при статичних рівнях сигналу 0, 1 або при перепаді на вході синхронізації С тригер зберігає занесену до нього інформацію (режим зберігання).

JK-тригери, реалізовані за двоступеневою схемою (рис. 5.35а), мають на шляху розповсюдження сигналу від входів до виходів більшу кількості логічних елементів, ніж JK-тригери, що реалізовані за одноступеневою схемою (рис. 5.32). Як наслідок для них характерна більша тривалість затримок і менша швидкодія. Тому останнім часом у комп’ютерній електроніці переважно застосовують одноступеневі JK-тригери з внутрішніми затримками. Схема такого комбінованого JKRS-тригера показана на рис. 5.38.

Ланцюги, що забезпечують попередню установку тригера показані на рис. 5.38 пунктирними лініями. Такою установкою керують сигнали низького рівня напруги (логічного „0”) на входах попередньої установки , . Якщо, наприклад, на ці входи подано сигнали = 0, = 1, то на виходах елементів І DD2, DD3 установлюється логічний „0”, а на виході елемента ІНЕ DD7 логічна „1”. Сигнали логічного нуля, що надходять з виходів DD2, DD3 на входи елемента АБОНЕ DD1, установлюють Q = 1. Логічна одиниця, що з’являється при цьому на виході DD5 (на всіх входах логічного елемента І DD5 в цьому випадку логічна „1”), надходить на вхід DD8 і установлює = 0. Таким чином, тригер перемикається у стан Q = 1, = 0 не залежно від сигналів, які діють на його входах J, K і C.

|

Рис. 5.38. Схема синхронного JKRS-тригера з внутрішніми затримками |

У синхронних JK-тригерах з внутрішніми затримками динамічне керування забезпечується за рахунок певного співвідношення між затримками поширення сигналу tзп логічних елементів, які входять до складу схеми тригера. Зокрема для тригера на рис. 5.38 час затримки поширення сигналу в елементах DD4, DD7 повинен перевищувати сумарну затримку поширення сигналу в логічних елементах DD3 (DD2), DD5 (DD6), DD1 і DD8, тобто між затримками повинні виконуватися наступні співвідношення: tзпDD4 > tзпDD3+tзпDD1+tзпDD5+tзпDD8; tзпDD7 > tзпDD2+tзпDD1+tзпDD6+tзпDD8.

Розглянемо

роботу JKRS-тригера

(рис. 5.38) у синхронному режимі (

= 1,

= 1), коли на входах J,

K

діє комбінація логічних сигналів

високого рівня U1

(J

= 1, K

= 1), яка є критичною для JK-тригерів

з точки зору виникнення паразитної

генерації. Припустимо, що логічні

елементи DD4,

DD7

мають час затримки поширення сигналу,

який не менш ніж у чотири рази перевершує

такий час для інших логічних елементів

схеми на рис. 5.38. Для спрощення при

побудові часових діаграм JK-тригера

з внутрішніми затримками (рис. 5.38) будемо

вважати, що всі елементи схеми окрім

DD4,

DD7

мають однакове значення часу затримки

поширення сигналу

![]() .

.

Нехай початково тригер (рис. 5.38) знаходиться у нульовому стані, тобто на його виході Q низький рівень напруги U0 (Q = 0), а на виході високий U1 ( = 1). Тоді при відсутності тактового сигналу на вході С (С = 0) на виходах логічних елементів ІНЕ DD4, DD7 високий рівень напруги U1 (логічна „1”), а на виході елементів І DD3, DD6 низький рівень напруги U0 (логічний „0”). Логічний нуль, що надходить по зворотному зв’язку з виходу Q на входи елементів І DD5, DD6 також забезпечує на їх виходах напругу низького рівня U0 (логічний „0”), а логічні одиниці з виходів DD4, DD8 і входу попередньої установки ( = 1) забезпечують на виході DD2 напругу високого рівня U1 (логічна „1”). Це початковий стан схеми JKRS-тригера, який має місце до моменту часу t0 (рис. 5.39), коли на вхід синхронізації С надходить тактовий імпульс.

Часові діаграми, що ілюструють динаміку перемикання синхронного JKRS-тригера з внутрішніми затримками показані на рис. 5.39. Після надходження в момент часу t0 сигналу С = 1 (перепад напруги на вході С від U0 до U1), спочатку, з затримкою , перемикається у стан логічної одиниці на виході елемент DD3, а потім, з затримкою tзпDD4, у стан логічного нуля елемент DD4, оскільки на всіх входах цих ЛЕ з моменту часу t0 діє логічна „1”. Логічний „0” на виході DD4 в момент часу t3 викликає перемикання DD2 у стан низького рівня напруги на виході U0 (логічного „0”). Зазначимо, що описані вище перемикання не змінюють вихідний стан тригера, оскільки активні сигнали високого рівня (логічної „1”), які надходять з виходів DD3, DD2 у цей проміжок часу (рис. 5.39) на входи логічного елемента АБОНЕ DD1 підтверджують вихідний стан тригера Q = 0, а сигнали низького рівня (логічний „0”) з виходів DD5, DD6 на входах DD8, пасивні для АБОНЕ, підтверджують стан інверсного виходу тригера = 1.

|

Рис. 5.39. Часові діаграми сигналів синхронного JKRS-тригера з внутрішніми затримками |

Зміна в момент часу t4 сигналу на вході С на логічний нуль (перепад напруги від U1 до U0) викликає перемикання DD3 у стан логічного нуля з затримкою і елемента DD4 у стан логічної одиниці з затримкою tзпDD4. Однак, як можна бачити з часових діаграм, оскільки tзпDD4 > 4 інші елементи з затримкою перемикаються, коли елемент DD4 ще має на виході низький рівень напруги U0 (логічний „0”), а елемент DD7 з такою ж затримкою tзпDD7 > 4 високий рівень напруги U1 (логічна „1”). Це і є внутрішня затримка, яка дозволяє JK-тригеру перемкнутися і запобігає виникненню паразитної генерації. Дійсно, перемикання DD3 у стан логічного нуля веде до появи на входах DD1 логічних нулів, що в момент часу t5 змінює напругу на виході DD1 на високий рівень U1, тобто встановлює прямий вихід тригера у стан Q = 1. Ця одиниця по зворотному зв’язку надходить на вхід елемента І DD5 і, за рахунок того, що тепер на всіх його входах логічна одиниця встановлює на вході DD8 напругу високого рівня U1, яка перемикає DD8 (момент часу t6) у стан логічного нуля, тобто = 0.

Таким чином, синхронний JK-тригер з внутрішніми затримками керується зрізом імпульсу і тому перемикається згідно таблиці переходів наведеній на рис. 5.35б.

Прикладом

комбінованого JKRS-тригера,

реалізованого за схемою з внутрішніми

затримками (рис. 5.38) є мікросхема

КР1531ТВ11 (функціональний аналог 74F114),

яка належить до швидкодіючої серії ТТЛШ

1531. Її умовне зображення і нумерація

виводів наведені на рис. 5.40. Мікросхема

містить два JKRS-тригера

з інверсними входами попередньої

установки

,

(установка логічним нулем), причому

входи попередньої установки у одиничний

стан (Q

=1,

= 0)

![]() ,

,

![]() роздільні,

а вхід установки у нульовий стан (Q

=0,

= 1)

є загальним для обох тригерів. Тригери

мікросхеми мають також загальний вхід

синхронізації С з керуванням зрізом

імпульсу.

роздільні,

а вхід установки у нульовий стан (Q

=0,

= 1)

є загальним для обох тригерів. Тригери

мікросхеми мають також загальний вхід

синхронізації С з керуванням зрізом

імпульсу.

|

Рис. 5.40. Умовне зображення мікросхеми КР1531ТВ11 |

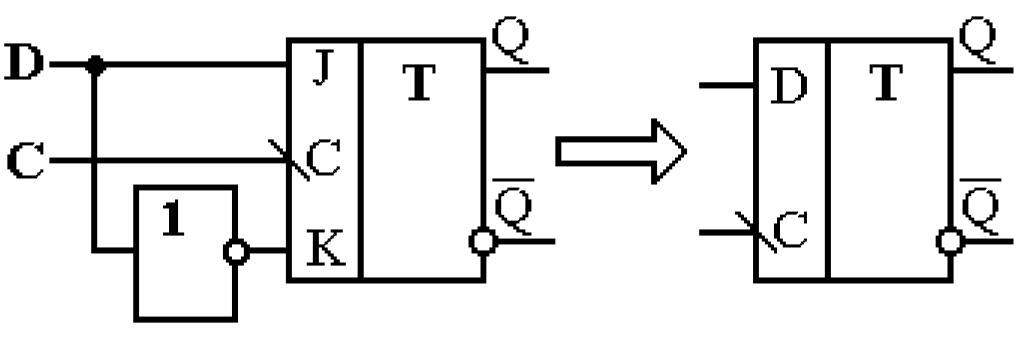

Синхронний JK-тригер має дещо більшу універсальність, порівняно з синхронним D-тригером, оскільки останній можна реалізувати на його основі. Дійсно, якщо у рівнянні JK-тригера (5.33) виконати підстановку:

Jn = Dn, = Dn, (5.34)

то отримаємо

Qn+1 = Qn + CnDn + CnDnQn = Qn + CnDn( +Qn) =

= Qn + CnDn1 = Qn + CnDn,

тобто логічне рівняння синхронного JK-тригера переходить у логічне рівняння синхронного D-тригера (5.27). Це означає, у відповідності до (5.34), що для реалізації синхронного D-тригера на основі синхронного JK-тригера інформаційні входи останнього слід об’єднати через інвертор і використати об’єднаний вхід, як інформаційний вхід синхронного D-тригера (рис. 5.41).

|

Рис. 5.41. Реалізація синхронного D-тригера на основі синхронного JK-тригера

|

5.6. Т-тригер

T-тригер має один інформаційний вхід, при наявності на якому керуючого сигналу (логічної „1” для Т-тригера зі статичним керуванням), перемикається у стан інверсний попередньому, а при відсутності такого сигналу (наявності логічного „0”) зберігає попередній стан. З урахуванням сказаного логіка роботи T-тригера описується таблицею справжності наведеною на рис. 5.42а. Умовне зображення T-тригера показано на рис. 5.42в.

Tn

Qn+1

0

Qn

1

|

|

|

|||||||||||||||||||||

а |

б |

в |

|||||||||||||||||||||

Рис. 5.42. T-тригер: а – скорочена таблиця справжності; б – розширена таблиця справжності; в – умовне графічне зображення

|

|||||||||||||||||||||||

Логічне рівняння T-тригера можна одержати, якщо на підставі скороченої таблиці справжності (рис. 5.42а) побудувати його розширену таблицю справжності (рис. 5.42б), з якої випливає, що логіка роботи T-тригера у ДДНФ описується рівнянням:

Qn+1

=

![]() Qn

+ Tn

. (5.35)

Qn

+ Tn

. (5.35)

Це рівняння має вигляд подібний до алгебраїчного виразу елементарної логічної функції двох змінних „сума за модулем 2” (див. вираз для функції f7(х1,x2) у табл. 3.4). Через цю особливість Т-тригери називають лічильними, а їх інформаційний вхід і режим роботи лічильними.

З таблиці справжності на рис. 5.42а випливає, що Т-тригер єдиний з вище розглянутих тригерів, поточний стан якого визначається не інформацією на вході, а його станом на попередньому такті.

Для реалізації Т-тригерів звичайно використовують універсальні синхронні JK- і D-тригери. Спосіб увімкнення таких тригерів для реалізації Т-тригера зі зворотним або прямим динамічним керуванням можна визначити шляхом аналізу рівнянь, що описують логіку роботи тригерів.

Порівняння співвідношень (5.27) і (5.35) показує, що логічне рівняння D-тригера переходить у логічне рівняння Т-тригера, якщо у співвідношення (5.27) підставити Cn = Tn і Dn = . Рівність Dn = фактично означає, що у D-тригері, схема якого не має зворотних зв’язків між входами і виходами (див. підрозділ 5.4.2), треба створити зворотний зв’язок для урахування поточного стану тригера для організації його перемикання керуючим сигналом у наступному такті у стан, що є інверсним поточному.

Таким чином, для реалізації T-тригера на основі синхронного D-тригера інформаційний вхід D треба підключити до інверсного виходу , а вхід синхронізації С використати, як лічильний вхід Т. На рис. 5.43 показано реалізацію Т-тригера, керованого фронтом імпульсу, на основі синхронного D-тригера з прямим динамічним керуванням.

|

Tn

Qn+1

0,

1,

Qn

|

||||||

а |

б |

||||||

Рис. 5.43. Реалізація Т-тригера керованого фронтом імпульсу на основі синхронного D-тригера з прямим динамічним керуванням (а) і таблиця переходів такого Т-тригера (б)

|

|||||||

Логічне рівняння синхронного JK-тригера (5.33) переходить у логічне рівняння Т-тригера (5.35), якщо у (5.33) підставити Cn = Tn, Jn = Kn = 1:

Qn+1

=

Qn

+ Tn1

+ Tn![]() Qn

=

Qn

+ Tn

+ Tn0Qn

= =

Qn

+ Tn

.

Qn

=

Qn

+ Tn

+ Tn0Qn

= =

Qn

+ Tn

.

Таким чином, для реалізації T-тригера на основі синхронного JK-тригера треба об’єднати входи J і K і подати на них логічну одиницю, а вхід синхронізації С використати, як лічильний вхід Т. На рис. 5.44 показано реалізацію Т-тригера, керованого зрізом імпульсу, на підставі синхронного JK-тригера зі зворотним динамічним керуванням.

|

Tn

Qn+1

0,

1,

Qn

|

|||||||

а |

б |

|||||||

Рис. 5.44. Реалізація Т-тригера керованого зрізом імпульсу на основі синхронного JK-тригера зі зворотним динамічним керуванням (а) і таблиця переходів такого Т-тригера (б)

|

||||||||

|

|

|||||||

|

||||||||

|

Рис. 5.45. Часові діаграми Т-три-гера керованого зрізом імпульсу |

По-перше, Т-тригер є дільником частоти з коефіцієнтом ділення два. По-друге, за один цикл своєї роботи, який дорівнює двом тактам, Т-тригер формує два значення однорозрядного двійкового числа 0 і 1, тобто підраховує два імпульси, що надійшли на його вхід. Вказані властивості Т-тригерів дозволяють будувати на їх основі такі вузли комп’ютерної електроніки як лічильники і дільники частоти, про які мова піде далі.

Vn

|

|

||||||||||||

а |

б |

||||||||||||

Рис. 5.46. TV-тригер: а – таблиця справжності; б – реалізація |

|||||||||||||

Qn+1

=

Qn

+ Vn![]() Qn

+ VnTn

. (5.36)

Qn

+ VnTn

. (5.36)

Можлива реалізація TV-тригера показана на рис. 5.46б.

У табл. 5.1 дано параметри деяких мікросхем тригерів.

Таблиця 5.1

Параметри інтегральних мікросхем тригерів

Параметр |

RS-тригер |

D-тригер |

JK-тригери |

|

564ТР2 |

КР1533ТМ2 |

КР1531ТВ11 |

КР1561ТВ1 |

|

Напруга живлення Uсс, В |

3 15 |

4,5 – 5,5 |

4,5 – 5,5 |

3 15 |

Максимальний струм споживання Iсс, мА |

0,02 (5 В) 0,08 (15 В) |

16 (5 В) |

19 (5 В) |

0,001 (5 В) 0,004 (15 В) |

Максимальна напруга низького рівня на виході U0max, В |

0,05 (5 В 15 В) |

0,5 (Uсс=4,5 В, IOL=8 мА) |

0,5 (Uсс=4,5 В, IOL=20 мА) |

0,05 (5 В 15 В) |

Мінімальна напруга високого рівня на виході U1min, В |

4,95(5 В) 14,95 (15 В) |

2,5 (Uсс=4,5 В, IOH=2 мА) |

2,5 (Uсс=4,5 В, IOH=1 мА) |

4,95 (5 В) 14,95 (15 В) |

Вихідний струм високого рівня I1вих (IОH), мА |

0,3 (5 В) 2,4 (15 В) |

0,4 |

1 |

0,88 (5 В) 8,8 (15 В) |

Вихідний струм низького рівня I0вих (IОL), мА |

0,88 (5 В) 6,0 (15 В) |

8 |

20 |

0,88 (5 В) 8,8 (15 В) |

Максимальний вхідний струм IIL, мА |

0,0003 |

0,5 (С, D) 2

( |

0,6 (J, K) 4,8 (С) |

0,0001 |

tзп1,0 (tPHL), tзп0,1 (tPLH), нс |

175 (5 В) 60 (15 В) |

518, 516 (C) |

37,5, 36,5 (C) |

110 (5 В) 40 (15 В) |

tвм1,0(tTHL), tвим0,1(tTLH), нс |

100 (5 В) 40 (15 В) |

|

|

100 (5 В) 40 (15 В) |

Час поперед-нього установ-лення сигналу tSU, нс |

|

16 (D) 10 ( , ) |

3 (J, K) |

(J, K) 135 (5 В) 45 (15 В) |

Час утримання tH, нс |

|

2 (D) |

0 (J, K) |

|

tZL, tLZ, нс |

100 (5 В) 40 (15 В) |

|

|

|

tZH, tHZ, нс |

115 (5 В) 40 (15 В) |

|

|

|

Мінімальна тривалість вхідного імпульсу tW, нс |

80 (5 В) 20 (15 В) |

15 ( , ) 17,5 (C) |

4,5 ( , ) 4,5 (C) |

(C) 100 (5 В) 32 (15 В) |

Робоча частота, Мгц |

|

34 |

95 |

5 (5 В) 15,5 (15 В) |

Вхідна ємність, пФ |

5,0 |

|

|

5,0 |

В дужках вказані значення напруги живлення, при яких були виміряні параметри, а також входи мікросхеми тригера, на яких відповідний параметр вимірювався.