- •І.М. Черненко, о.І. Івон

- •Електронні елементи та вузли комп'ютерів

- •Дніпропетровськ, 2009

- •Передмова

- •Перелік вживаних скорочень

- •1.1. Загальні відомості, визначення

- •1.2. Способи представлення сигналів в обчислювальних пристроях. Системи числення.

- •Контрольні запитання

- •Розділ 2. Електронні ключі

- •2.1. Основні поняття. Класифікація, вимоги

- •2.2. Ключі на біполярних транзисторах

- •2.3 Ключі на польових (уніполярних) транзисторах

- •Контрольні запитання

- •Цифрової техніки

- •3.1 Математичні основи функціонування елементів та вузлів комп’ютерної електроніки

- •Контрольні запитання

- •4.1. Загальні поняття. Умовне зображення логічних елементів

- •4.2 Параметри елементів цифрової електроніки

- •4.3 Базові логічні елементи транзисторно-транзисторної логіки Шотткі (ттлш)

- •4.4 Базові логічні елементі на мон-транзисторах

- •4.5 Логічні елементи на польових транзисторах структури „метал-напівпровідник” з бар’єром Шотткі

- •Контрольні запитання

- •5.1 Загальні поняття і класифікація тригерів

- •5.2 Параметри тригерів

- •5.3 Асинхронні і синхронні rs-тригери

- •5.4 Асинхронні і синхронні d-тригери

- •5.5. Асинхронні і синхронні jk-тригери

- •5.7. Несиметричний тригер (тригер Шмітта)

- •5.8 Приклади використання тригерів

- •Контрольні запитання

- •Цифрових пристроїв

- •6.1. Інтегрувальні та диференціювальні

- •Сигналів на логічні елементи

- •6.2. Формувачі

- •6.3. Генератори поодиноких імпульсів (одновібратори)

- •6.4. Генератори (мультивібратори)

- •Контрольні запитання

- •7.1 Основні поняття, класифікація

- •7.2 Комбінаційні функціональні вузли

- •7.3. Комбінаційні арифметичні вузли

- •7.4. Послідовнісні вузли

- •Контрольні запитання

- •Та їх елементи

- •8.1 Основні поняття, класифікація

- •8.2 Параметри запам’ятовуючих пристроїв

- •8.3 Структури адресних запам’ятовуючих пристроїв

- •8.4. Динамічні запам’ятовуючі пристрої та їх елементи

- •8.5. Статичні запам’ятовуючі пристрої та їх елементи

- •8.6. Постійні запам’ятовуючі пристрої та їх елементи

- •Контрольні запитання

- •Список літератури Список основної літератури

- •Список рекомендованої літератури

7.3. Комбінаційні арифметичні вузли

7.3.1. Загальна характеристика арифметичних вузлів. Арифметично-логічний пристрій (АЛП) процесора виконує арифметичні і логічні операції над багаторозрядними двійковими словами. До складу АЛП входять блоки призначені для виконання арифметичних операцій над числами в форматах з фіксованою крапкою, плаваючою крапкою та десятковому форматі. Важливою частиною цих блоків є цифрові вузли, що виконують елементарні математичні операцій: додавання, віднімання, множення, ділення і порівняння двійкових чисел. Такі вузли будують на основі логічних елементів, як комбінаційні схеми, тому вони мають назву комбінаційні арифметичні вузли.

Особливістю двійкової арифметики є те, що чотири арифметичні дії в ній можна звести до двох операцій додавання і зсуву. Тому основу арифметичних вузлів складають суматори. Суматором називають функціональний вузол комп’ютера, призначений для додавання двох n-розрядних двійкових слів (чисел). Такі вузли будують на базі елементарних цифрових вузлів, здатних виконувати операцію додавання в одному розряді двійкового числа, тобто додавати два однобітових числа. До таких однорозрядних арифметичних вузлів відносяться напівсуматор і повний суматор

За способом додавання суматори поділяють на паралельні, послідовні та паралельно-послідовні. У паралельних n-розрядних суматорах значення всіх розрядів операндів надходять у паралельному коді одночасно на відповідні входи суматора, кількість яких визначає розрядність двійкових чисел, що додаються. Послідовні суматори виконують операцію додавання операндів представлених у послідовному коді. Для виконання операції додавання вони використовують один однорозрядний суматор, на входи якого, в кожному такті, поступають значення розрядів операндів послідовно в напрямку від молодших розрядів до старших, а перенесення, що запам’ятовується у попередньому такті за допомогою тригера, враховується при формуванні значення однорозрядної суми в поточному такті. Складовою частиною послідовних n-розрядних суматорів є регістри зсуву, тому такі суматори не є комбінаційними цифровими вузлами. В паралельно-послідовних суматорах n-розрядні числа розбиваються на частини по k розрядів. Кожна з цих частин подається у паралельному коді на входи k-розрядного суматора (одночасно у всіх розрядах), а самі частини – послідовно, роздільно у часі, в напрямку від молодших частин до старших з урахуванням перенесення, яке запам’ятовується.

За схемотехнічними ознаками і особливостями формування результату операції додавання суматори поділяють на комбінаційні і накопичувальні. Комбінаційні суматори не містять елементів пам’яті і реалізуються, як комбінаційні схеми. Накопичувальні суматори являють собою поєднання комбінаційного суматора і регістра. Такі суматори працюють згідно співвідношенню S := S+A („:=” – символ присвоювання), тобто до попереднього значення суми S, що зберігається у регістрі, додається черговий доданок А і результат заміщає старе значення суми у регістрі.

За способом організації перенесення між розрядами суматори поділяють на суматори з послідовним, паралельним, наскрізним та груповим перенесеннями. Спосіб перенесення визначає час виконання операції додавання. Суматори з послідовним перенесенням схемотехнічно організовані досить просто, але мають низьку швидкодію порівняно з суматорами з паралельним перенесенням, які схемотехнічно організовані значно складніше.

За системою числення суматори поділяють на двійкові і десяткові. Двійкові суматори виконують операцію складання двійкових операндів представлених у знаковому і беззнаковому форматі з фіксованою крапкою (див. підрозділ 7.2.8). В десяткових суматорах для подання операндів використовується двійково-десятковий код (див. підрозділ 1.2). Такі суматори будують з урахуванням правил десяткової арифметики на основі двійкових суматорів, які виконують операцію додавання двійкових тетрад, які відображують десяткові цифри в двійково-десятковому коді.

При побудові арифметичних вузлів комп’ютера на основі двійкових суматорів враховують, що операція віднімання може бути замінена додаванням двійкових операндів у оберненому або доповняльному коді, а операції множення та ділення можна звести до багаторазового додавання та зсування. Отже розглянемо принципи побудови арифметичних вузлів комп’ютерної електроніки.

7.3.2. Однорозрядні двійкові суматори. Такі суматори виконують додавання однорозрядних двійкових чисел. В залежності від можливості враховувати перенесення в результаті операції їх поділяють на напівсуматор і повний суматор.

|

|

||||||||||||||||||||

а |

б |

||||||||||||||||||||

Рис. 7.29. Напівсуматор: умовне графічне зображення (а); таблиця справжності (б) |

|||||||||||||||||||||

S

=

![]() B

+ A

B

+ A![]() = AB;

P

= AB. (7.34)

= AB;

P

= AB. (7.34)

Схеми напівсуматора в булевому базисі і базисі Жегалкіна, побудовані на підставі (7.34), показані на рис. 7.30.

|

Рис. 7.30. Схеми напівсуматора в булевому базисі (а) та базисі Жегалкіна (б)

|

Повний суматор враховує перенесення, тому має три входи: А і B для однорозрядних операндів і вхід перенесення P0. Як й напівсуматор, повний суматор на двох своїх виходах формує значення суми S і перенесення P від операції додавання, яку він виконує. Умовне зображення повного суматора показано на рис. 7.31а. Завдяки здатності враховувати перенесення повний суматор при побудові на його основі n-розрядних суматорів може бути використаний у будь-якому i-тому розряді такого суматора. В цьому випадку функції виходів повного суматора i-того розряду Si і Pi залежать від значення розрядів Ai, Bi багаторозрядних операндів і значення перенесення Pi-1 з сусіднього молодшого i-1-го розряду (рис. 7.31а).

|

|

||||||||||

а |

б |

||||||||||

Рис. 7.31. Повний суматор: умовне графічне зображення (а); таблиця справжності (б)

|

|||||||||||

Таблиця справжності для функцій Pi(Ai,Bi,Pi-1), Si(Ai,Bi,Pi-1), побудована з урахуванням правил двійкової арифметики, наведена на рис. 7.31б, а результати мінімізації методом Вейча показані на рис. 7.32а. З них випливає, що склеювання одиниць має місце тільки для функції Pi(Ai,Bi,Pi-1). Її логічне рівняння, отримане за результатами склеювання, має вигляд:

Pi = AiBi + BiPi-1 + AiPi-1, (7.35)

а логічне рівняння для функції виходу Si повного суматора у ДДНФ можна записати як

![]() . (7.36)

. (7.36)

|

|

а |

б |

Рис. 7.32. Результати мінімізації методом Вейча функцій виходів повного суматора (а) і функції його виходу S, як булевої функції чотирьох змінних (б)

|

|

Із співвідношень (7.35), (7.36) випливає, що для побудови схеми повного суматора в булевому базисі потрібні 3 інвертори, чотири елемента 3І, три елемента 2І, один елемент 4АБО і один 3АБО, тобто всього 12 елементів. Схему повного суматора можна спростити, скоротивши кількість логічних елементів, якщо виконати мінімізацію Si, розглянувши цю функцію як частково визначену БФ чотирьох змінних Si(Ai,Bi,Pi-1,Pi). Результати такої мінімізації представлені на рис. 7.32б. З них випливає наступне логічне рівняння:

![]() . (7.37)

. (7.37)

В цьому випадку, з урахуванням (7.35), для побудови схеми повного суматора потрібен тільки один інвертор, шість елементів 2І, один 3І, один елемент 4АБО і один 3АБО, тобто всього 10 логічних елементів. Така схема наведена на рис. 7.33. Її особливістю є наявність зворотного зв’язку між виходом перенесення Pi і схемою формування однорозрядної суми Si. Наслідком цього є те, що швидкодія формування суми менша за швидкодію формування перенесення, оскільки час затримки сигналу Pi визначається тільки сумою затримок поширення сигналу елемента І та АБО, а час затримки формування суми Si сумою затримок перенесення Pi і поширення сигналу в логічних елементах НЕ, І та АБО. Тому параметри швидкодії повного суматора визначаються співвідношеннями:

tзпP = tзпI + tзпАБО; tзпS = 2tзпI + 2tзпАБО + tзпНЕ. (7.38)

|

Рис. 7.33. Схема повного суматора в булевому базисі |

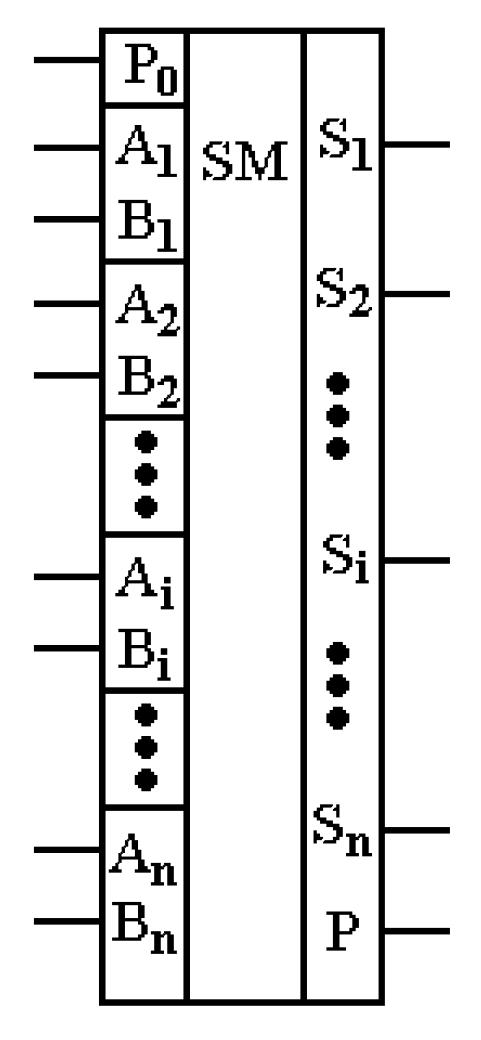

Найпростішим за схемотехнічною організацією є паралельний суматор з послідовним перенесенням, схема якого та умовне зображення показані на рис. 7.34.

Значення всіх розрядів чисел A і B поступають на входи відповідних однорозрядних суматорів одночасно, а сигнал перенесення передається від розряду до розряду послідовно у часі, починаючи від молодшого розряду суми S1 до її старшого розряду Sn.

У паралельних суматорах з послідовним перенесенням час виконання операції складання t у найгіршому випадку, коли сигнал перенесення послідовно розповсюджується від першого до n-того розряду, визначається співвідношенням:

t = (n-1)tзпP + tзпS, (7.39)

де значенням tзпP і tзпS для повних суматорів реалізованих за схемою на рис. 7.33 задаються співвідношеннями (7.38).

|

|

а |

б |

Рис. 7.34. Схема паралельного суматора з послідовним перенесенням (а) і умовне зображення n-розрядних суматорів(б) |

|

Схеми прискорених переносів виробляють сигнали перенесення Pi одночасно для всіх розрядів суматора. Сигнал Pi для даного розряду формується такими схемами з урахуванням всіх змінних необхідних для вироблення перенесення, тобто тих, від яких залежить його наявність або відсутність. Такими змінними є зовнішнє перенесення P0 та значення всіх розрядів доданків, які є молодшими відносно даного розряду. З урахуванням цього структура n-розрядного суматора з паралельним перенесенням має вигляд, показаний на рис. 7.35. Тут схеми прискорених переносів позначені як CR (від англійського слова carry перенесення), а для повних суматорів SM вихід переносу не показаний, оскільки він не приймає участі у формуванні значення суми.

Для визначення логічної структури схем прискореного переносу CRi використовують дві допоміжні функції: генерації і прозорості.

Функція генерації приймає одиничне значення, коли перенесення на виході даного розряду з’являється незалежно від наявності або відсутності вхідного перенесення. Це має місце колі обидва доданки Ai і Bi дорівнюють одиниці, тому функцію генерації можна представити кон’юнкцією gi = AiBi.

|

Рис. 7.35. Структура суматора з паралельним перенесенням

|

Функція

прозорості

приймає одиничне значення, коли

перенесення в даному розряді з’являється

тільки при наявності сигналу перенесення

на вході повного суматора цього розряду.

Це має місце, коли хоча б один з доданків

Ai

чи Bi

приймає одиничне значення, тобто функцію

прозорості можна представити у вигляді

виключального АБО (суми за модулем 2) hi

=

![]() = Ai

Bi.

Аналіз можна спростити, якщо виключальне

АБО замінити диз’юнкцією, тобто функцію

прозорості записати у вигляді hi

= Ai

+ Bi.

Підставою для такої заміни є те, що

перенесення буде виникати і у випадку,

коли обидва доданки дорівнюють одиниці.

= Ai

Bi.

Аналіз можна спростити, якщо виключальне

АБО замінити диз’юнкцією, тобто функцію

прозорості записати у вигляді hi

= Ai

+ Bi.

Підставою для такої заміни є те, що

перенесення буде виникати і у випадку,

коли обидва доданки дорівнюють одиниці.

З урахуванням викладеного вище вираз для функції перенесення Pi в будь-якому i-тому розряді суматора можна записати у вигляді:

Pi = gi + hiPi-1. (7.40)

На підставі (7.40) для функцій перенесення різних розрядів суматора можна отримати наступну систему рівнянь:

P1 = g1 + h1P0;

P2 =g2 +h2(g1 + h1P0) = g2 +h2g1 + h2h1P0;

P3 = g3 + h3(g2 + h2(g1 + h1P0)) =

= g3 + h3g2 + h3h2g1 + h3h2h1P0;

![]() (7.41)

(7.41)

Pi = gi + higi-1 + hihi-1gi-2 + hihi-1h i-2gi-3 +…+hihi-1…h2g1 +

+hihi-1…h2h1P0,

де P0 – значення вхідного перенесення суматора.

Побудову схеми суматора з паралельним перенесенням розглянемо на прикладі чотирьохрозрядного суматора. Функції перенесення такого суматора описуються першими трьома рівняннями системи (7.41). На підставі закону де Моргана приведемо ці рівняння до базису ІНЕ:

(7.42)

(7.42)

На рис. 7.36 показано варіант схеми паралельного суматора з паралельним перенесенням, яка побудована згідно (7.42), з урахуванням, що hi = Ai + Bi (i = 1, 2, 3).

|

Рис. 7.36. Схема чотирьохрозрядного суматора з паралельним перенесенням

|

Хоча кількість логічних елементів схеми прискореного перенесення зростає в старших розрядах суматора, в будь-якому розряді вона має три рівня затримки. Це означає, що на відміну від суматора з послідовним перенесенням значення бітів суми формуються одночасно для всіх двійкових розрядів, тому час виконання операції складання t не залежить від кількості розрядів суматора і визначається співвідношенням:

t = 3tзп + tзпS, (7.43)

де tзп час затримки поширення сигналу логічних елементів АБО та ІНЕ схеми прискореного перенесення (для спрощення прийнято, що ці елементи мають однакову затримку поширення сигналу, яка дорівнює tзп), tзпS – час затримки поширення повного суматора.

Отже перевагою суматорів з паралельним перенесенням є висока швидкодія, що не залежить від кількості розрядів суматора. Недолік полягає в ускладненні схеми, порівняно з суматорами з послідовним перенесенням (рис. 7.34а). Окрім того із зростанням кількості розрядів суматора, зростає кількість входів логічних елементів ІНЕ схеми прискореного перенесення, а оскільки вона обмежена значенням Kоб = 8, суматори, побудовані за схемою, яка наведена на рис. 7.36, не можуть мати більше восьми розрядів. При побудові суматорів з більшою розрядністю використовують комбіноване паралельно-послідовне перенесення.

Один з можливих способів нарощування розрядності суматорів показано на рис. 7.37. У випадку, коли для нарощування використані суматори з паралельним перенесенням, схема, що наведена на рис. 7.37, є суматором з паралельно-послідовним перенесенням, у випадку використання суматорів з послідовним перенесенням ця схема суматор с послідовним перенесенням.

|

Рис. 7.37. Нарощування розрядності суматорів

|

При нарощуванні розрядності для організації паралельного перенесення між суматорами можуть бути використані схеми прискореного перенесення, які випускаються як самостійні вироби у складі деяких серій інтегральних мікросхем. Для прикладу наведемо чотирьохрозрядні мікросхеми прискореного перенесення КР1533ИП4 (SN74LS182), КР1531ИП4 (74F182).

|

Рис. 7.38. Умовне графічне зображення мікросхеми КР1594ИМ6 |

Таблиця 7.7

Параметри інтегральних мікросхем суматорів ТТЛШ і КМОПТЛ

Параметр |

Мікросхеми та їх функціональні аналоги |

||||

КР1531ИМ6 (74F283) |

К561ИМ1 (CD4008BMS) |

КР1554ИМ6 (HD74AC283) |

КР1594ИМ6 (HD74ACT283) |

||

Uсс, В |

4,5÷5,5 |

5÷20 |

2÷6 |

2÷6 |

|

I1сп, (IccH), мА |

36 |

0,01 (15 В) |

0,008 (5,5 В) |

0,008 (5,5 В) |

|

I0сп, (IccL), мА |

36 |

||||

U0вих, (UОL), В |

≤ 0,5 |

≤ 0,05 |

≤ 0,1 |

≤ 0,1 |

|

U1вих, (UОH), В |

2,5 |

Uсс 0,05 |

Uсс 0,1 |

Uсс 0,1 |

|

I1вх (IIH), мкА |

5 |

0,1 |

0,1 |

0,1 |

|

I0вх (IОL), мА |

1,2 |

110-4 |

110-4 |

110-4 |

|

I0вих (IОL), мА |

≤ 60 |

≤ 2,4 |

≤ 50 |

≤ 50 |

|

tPLH, нс |

P0Si |

7,0 7,0 |

310 (10 В) |

9,5 (5 В) 8,5 (5 В) |

11,5 (5 В) 10,0 (5 В) |

tPHL, нс |

|||||

tPLH, нс |

Ai або BiSi |

7,0 7,0 |

320 (10 В) |

11,5 (5 В) 11,0 (5 В) |

13,0 (5 В) 12,0 (5 В) |

tPHL, нс |

|||||

tPLH, нс |

P0P |

5,7 5,4 |

100 (10 В) |

7,5 (5 В) 8,0 (5 В) |

9,0 (5 В) 10,0 (5 В) |

tPHL, нс |

|||||

Нагадаємо, що значення напруги, вказані в табл. 7.7 в дужках, відповідають напрузі живлення, при якій був виміряний відповідний параметр інтегральної мікросхеми.

7.3.4. Двійково-десятковий суматор. Суматори багаторозрядних десяткових чисел будують на основі елементарних однорозрядних двійково-десяткових суматорів, що виконують операцію складання двійкових тетрад, які відображують десяткові цифри в двійково кодованій десятковій системі числення (див. підрозділ 1.2). Тому однорозрядний двійково-десятковий суматор можна реалізувати на основі чотирьохрозрядних двійкових суматорів. Такий однорозрядний двійково-десятковий суматор повинен формувати значення однорозрядної десяткової суми в двійково-десятковому коді і значення десяткового перенесення P10 з урахуванням правил десяткової арифметики.

Оскільки при додаванні тетрад двійково-десяткового коду значення суми може перевищувати число 910 = 10012, потрібна корекція результату. Така корекція повинна виконуватись при виникненні десяткового перенесення (P10 = 1), шляхом віднімання від тетради результату числа 1010 = 10102. Оскільки в двійковій арифметиці віднімання заміняється додаванням у доповняльному коді, корекція результату може бути здійснена шляхом додавання до результату доповняльного коду числа мінус десять, тобто [10102]д = 01102. Отже для побудови однорозрядного десяткового суматора потрібні два чотирьохрозрядних двійкових суматори, один з яких буде додавати двійкові тетради десяткових цифр, а другий – здійснювати корекцію результату.

Для визначення схеми формування десяткового перенесення розглянемо P10, як функцію змінних S4, S3, S2, S1 на виході суматора, який додає тетради десяткових цифр. Цю функцію описує таблиця справжності на рис. 7.39а, а її мінімізація методом діаграм Вейча показана на рис. 7.39б.

S4

|

|

||||||||||||||||||||||||||||||||||||||||||||||||||

а |

б |

||||||||||||||||||||||||||||||||||||||||||||||||||

Рис. 7.39. Таблиця справжності для функції десяткового перенесення P10 (а) і результати її мінімізації методом діаграм Вейча (б) |

|||||||||||||||||||||||||||||||||||||||||||||||||||

Результат мінімізації можна записати у вигляді логічного рівняння:

P10 = S4S3 + S4S2. (7.44)

Слід зазначити, що десяткове перенесення виникає також при значеннях суми тетрад 1610, 1710 і 1810, коли на виході P чотирьохрозрядного двійкового суматора, який додає тетради виникає двійкове перенесення P = 1, тому співвідношення (7.44) треба доповнити:

P10

= S4S3

+ S4S2

+ P

=

![]() . (7.45)

. (7.45)

З урахуванням вище викладеного та співвідношення (7.45) можна побудувати схему однорозрядного двійково-десяткового суматора (рис. 7.40). Тетради двійкового коду десяткових цифр подаються на входи A1A4 і B1B4 суматора DD1. Якщо при додаванні тетрад P10 = 0, то суматор DD2 додає до результату число 00002 і він передається на вихід без зміни. При виникненні десяткового перенесення P10 = 1 до результату складання тетрад додається число 01102, тобто відбувається десяткова корекція суми.

|

Рис. 7.40. Схема однорозрядного двійково-десяткового суматора

|

На базі однорозрядних двійково-десяткових суматорів (рис. 7.40) нескладно побудувати багаторозрядний паралельний десятковий суматор з послідовним перенесенням шляхом об’єднання виходів P10 і входів P0 суматорів сусідніх розрядів у напрямку від молодших десяткових розрядів до старших. В такому суматорі тетради двійково-десяткового коду одночасно подаються на входи відповідних однорозрядних двійково-десяткових суматорів.

7.3.5. Реалізація операції віднімання на двійкових суматорах. В двійковій арифметиці операція віднімання чисел А = AnAn-1…Ai…A2A1, B = BnBn-1…Bi…B2B1 може бути замінена операцією додавання, якщо від’ємник представити у оберненому або доповняльному коді. Дійсно, різницю двох чисел можна записати як A B = A + (B), звідкіля випливає, що різниця може бути замінена алгебраїчною сумою зменшуваного і негативного від’ємника. Оскільки для подання від’ємних чисел в цифровій техніці використовують обернений і доповняльний коди (див. підрозділ 7.2.8), то у загальному випадку різницю двох чисел можна записати як

A – B = A + [B]з = A + [B]д =

=

AnAn-1…Ai…A2A1

+

![]() = (7.46)

= (7.46)

= AnAn-1…Ai…A2A1 + +1.

При виконанні операції віднімання в оберненому коді треба враховувати циклічне перенесення, тобто при наявності перенесення зі старшого біту суми до результату треба додати одиницю, у доповняльному коді циклічне перенесення не враховують. Зазначимо також, що при поданні чисел у знаковому форматі з фіксованою крапкою, операція порозрядного складання виконується однаковим чином, як над цифровими бітами, так і над знаковим бітом формату. Результат операції віднімання буде у тому коді, який використовується для подання від’ємника.

З урахуванням викладеного вище і (7.46) для реалізації на суматорах арифметичної операції віднімання біти зменшуваного треба подати на входи суматора безпосередньо, а від’ємника – через інвертори. Якщо операція виконується у оберненому коді, вихід перенесення суматора P з’єднують з його входом P0 для реалізації циклічного перенесення. При виконанні операції віднімання в доповняльному коді на вхід перенесення суматора P0 подають логічну одиницю, підсумовування якої до оберненого коду, що надходить з виходів інверторів, забезпечує доповняльний код від’ємника.

На рис. 7.41 наведені схеми увімкнення суматорів для реалізації віднімання чотирьохрозрядних двійкових чисел A = A4A3A2A1 і B = B4B3B2B1.

Зазначимо, що числа A і B, що надходять на входи суматорів (рис. 7.41) можуть бути представлені, як у беззнаковому, так і у знаковому форматі з фіксованою крапкою. У випадку знакового формату біти чисел A4 і B4 будуть знаковими, а знак результату буде відображати біт суми S4.

|

|

а |

б |

Рис. 7.41. Схеми увімкнення суматора для виконання операції віднімання в оберненому (а) і доповняльному (б) кодах

|

|

Якщо в схемах на рис. 7.41 інвертори замінити на логічні елементи сума за модулем 2, то можна реалізувати арифметичний вузол, який в залежності від керуючого сигналу виконує або операцію складання або операцію віднімання. Схема такого вузла показана на рис. 7.42.

|

Рис. 7.42. Схема арифметичного вузла для виконання операцій складання і віднімання |

7.3.6. Матричні помножувачі. Арифметично-логічні пристрої сучасних комп’ютерів виконують арифметичну операцію множення не мікропрограмним, а апаратним шляхом. Добуток двійкових чисел апаратним шляхом можна отримати за допомогою матричних помножувачів. Такі цифрові вузли будують на основі суматорів і елементарних помножувачів, що формують добуток M однорозрядних двійкових чисел Aі B.

Для визначення схеми однорозрядного помножувача розглянемо арифметичний добуток M, як булеву функцію логічних змінних A, B. Таблиця справжності функції M, побудована з урахуванням правил двійкової арифметики для операції множення, наведена на рис. 7.43а. З неї випливає, що арифметична операція множення однорозрядних двійкових чисел співпадає з логічною операцією кон’юнкція. Саме тому кон’юнкцію називають логічним множенням.

A

|

|

||||||

а |

б |

||||||

Рис. 7.43. Таблиця справжності однорозрядного двійкового помножувача (а) і його схема (б) |

|||||||

Структура матричних помножувачів тісно пов’язана зі структурою математичних виразів, що описують операцію множення, зокрема з відомою схемою „множення стовпчиком”. Така схема у випадку чотирьохрозрядного множеного A = A4A3A2A1 і двохрозрядного множника B = B2B1. має вигляд:

A4 A3 A2 A1

B2 B1

![]()

A4B1 A3B1 A2B1 A1B1

+

A4B2 A3B2 A2B2 A1B2

![]()

M6 M5 M4 M3 M2 M1

Звідкіля для значень розрядів добутку Mі (і = 1, 2,...,6) випливають наступні співвідношення:

, (7.47)

, (7.47)

де знаком „+” позначена арифметична операція складання, а P1 P4 значення перенесень, що виникають при додаванні розрядів часткових добутків.

Оскільки однорозрядні арифметичні добутки AiBi, як показано вище, можна отримати за допомогою логічних елементів 2І, для побудови матричного помножувача згідно (7.47) потрібно вісім таких елементів. З співвідношення (7.47) також випливає, що для порозрядного складання добутків AiBi для отримання добутку багаторозрядних чисел A і B потрібен чотирьохрозрядний двійковий суматор, у схемі якого формуються і враховуються внутрішні перенесення P1 P4 (див. підрозділ 7.3.3). Схема матричного помножувача показана на рис. 7.44.

|

Рис. 7.44. Схема матричного помножувача двійкових чисел |

tM = tзп кон + t, (7.48)

де tзп кон – час затримки поширення сигналу кон’юнктора, t час виконання операції додавання суматором. Матричні помножувачі мають високу швидкодію і виконують операцію множення за один такт, що вигідно відрізняє їх від арифметичних блоків множення мікропроцесорів перших поколінь, які виконували цю операцію мікропрограмним способом за декілька тактів, шляхом виконання послідовності операцій додавання і зсуву.

7.3.7. Цифрові компаратори. Ці комбінаційні цифрові вузли призначені для порівняння двох двійкових чисел (слів). Їх назва походить від англійської compare – порівнювати. Результат порівняння чисел, який реалізує компаратор, можна представити у вигляді функції F, що приймає одиничне значення при виконанні умови, яка указана в її індексі. Наприклад, функція FA=B дорівнює одиниці коли A = B і приймає нульове значення при A ≠ B. У загальному випадку компаратори мають три виходи, на яких реалізуються три булеві функції: FA=B – рівність чисел, FA>B – число A більше за B, FA<B – число A менше за число B.

Ai

|

||||||||

Рис. 7.45. Таблиця справжності функцій порівняння однорозрядних чисел „на рівність” Ei та „на менше” Li |

З таблиці справжності випливає, що Ei є булевою функцією еквівалентності (див. підрозділ 4.1), яка описується логічним рівнянням:

Ei

=![]() =

=![]() =

=![]() =

=![]() . (7.49)

. (7.49)

Цю функцію реалізує логічний елемент еквівалентності, умовне графічне зображення якого наведено в табл. 4.1.

З таблиці справжності (рис. 7.45) випливає, що функція порівняння „на менше” Lі описується рівнянням

Li

=

![]() . (7.50)

. (7.50)

На підставі співвідношень (7.49) і (7.50) можна побудувати схему компаратора однорозрядних двійкових чисел, яка наведена на рис. 7.46.

Порівняння багаторозрядних двійкових чисел A = AnAn-1…Ai…A2A1 і B = BnBn-1…Bi…B2B1 виконують шляхом порозрядного порівняння значень їх бітів Ai і Bi. Для цієї мети використовують схеми однорозрядних компараторів (рис. 7.46). Очевидно, рівність чисел A і B буде мати місце, тобто FA=B = 1, у випадку, коли значення всіх однойменних розрядів цих чисел Ai і Bi співпадають, тобто Ei = 1 для всіх розрядів чисел i = 1, 2, ..., n. З урахуванням означеного, функція FA=B є кон’юнкцією елементарних функцій порівняння „на рівність” Ei, тобто FA=B = EnEn-1…Ei…E2E1. Останнє співвідношення на підставі закону де Моргана запишемо у вигляді:

FA=B=![]() =

=![]() . (7.51)

. (7.51)

|

Рис. 7.46. Схема порівняння однорозрядних чисел „на рівність” та „на менше”

|

Порівняння багаторозрядних чисел A і B „на менше” починають з їх старших розрядів An та Bn. Очевидно, A буде менше за B, якщо однорозрядна функція порівняння старших розрядів „на менше” дорівнює одиниці Ln = 1. У випадку коли An = Bn, число A менше за B при умові, що кон’юнкція EnLn-1 = 1. При рівності розрядів An = Bn і An-1 = Bn-1 виконання умови A < B забезпечується, коли кон’юнкція EnEn-1Ln-2 = 1 і так далі. Таким чином, якщо узагальнити всі випадки виконання умови, при якій A < B, то функцію порівняння багаторозрядних двійкових чисел A = AnAn-1…Ai…A2A1 і B = BnBn-1…Bi…B2B1 „на менше” FA<B можна записати як диз’юнкцію кон’юнкцій однорозрядних функцій порівняння „на рівність” Ei та „на менше” Lі у наступному вигляді:

FA<B=Ln + EnLn-1 + … + EnEn-1…Ei+1Li + … + EnEn-1…E2L1.

На підставі закону де Моргана перетворимо це співвідношення до вигляду:

FA<B=![]() =

=

=

![]() . (7.52)

. (7.52)

У співвідношеннях (7.51) і (7.52) стоять інверсні значення функцій Ei і Li. Це дає можливість спростити схему компаратора однорозрядних чисел, наведену на рис. 7.46 при її використанні в компараторах багаторозрядних двійкових чисел. З неї можна вилучити елемент DD3, а елемент 2І DD6 замінити на логічний елемент 2ІНЕ.

З (7.51)

та (7.52) також випливає, що при зростанні

розрядності n

зростає кількість входів логічних

елементів ІНЕ,

АБО в схемі багаторозрядного компаратора.

Тому компаратори, звичайно, будують з

розрядністю не більше чотирьох, а при

потребі створення компараторів на

більшу розрядність, їх нарощують шляхом

використання декількох компараторів

з меншою розрядністю. Для нарощування

розрядності в компараторах створюють

спеціальні входи, до яких при нарощуванні

підключаються виходи FA>B,

FA=B,

FA<B

компаратора сусідніх молодших розрядів.

Позначимо логічні змінні, що діють на

входах нарощування, як

![]() ,

,

![]() ,

,

![]() .

Вони задають результат порівняння

молодших розрядів багаторозрядних

чисел, який можна врахувати у співвідношеннях

(7.51), (7.52) таким чином:

.

Вони задають результат порівняння

молодших розрядів багаторозрядних

чисел, який можна врахувати у співвідношеннях

(7.51), (7.52) таким чином:

FA=B

=

![]() ; (7.53)

; (7.53)

FA<B

=

![]() . (7.54)

. (7.54)

Функцію виходу компаратора FA>B можна визначити на підставі функцій FA=B, FA<B. Очевидно, FA>B =1, коли FA=B = FA<B =0. Це свідчить про те, що булеву функцію FA>B можна визначити, як заперечення диз’юнкції булевих змінних FA=B, FA<B, тобто

FA>B

=

![]() . (7.55)

. (7.55)

Схему компаратора, яку можна побудувати на підставі співвідношень (7.53) (7.55), розглянемо на прикладі компаратора чотирьохрозрядних двійкових чисел. Логічні рівняння (7.53) (7.54) у випадку чотирьохрозрядного компаратора приймають вигляд

FA=B

=

![]() ;

;

FA<B

=![]() .

.

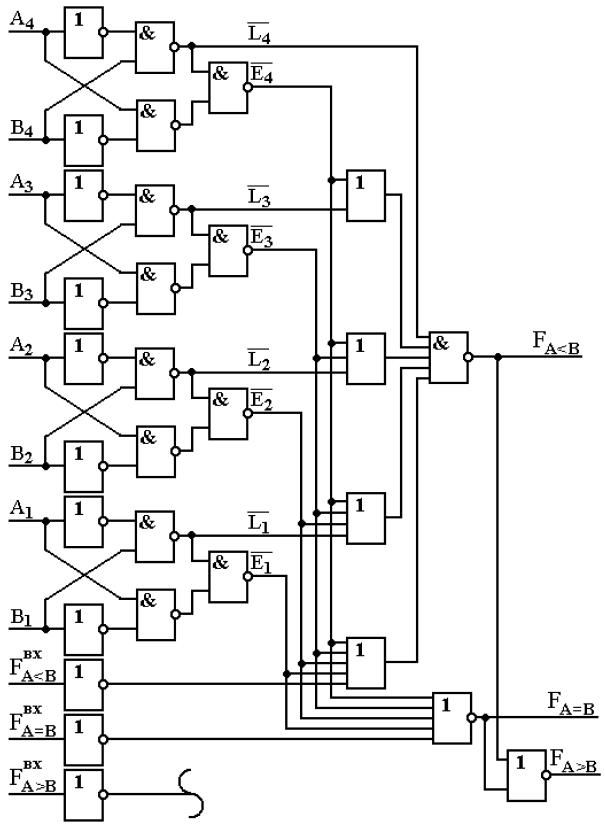

З них і співвідношення (7.55) випливає, що для побудови компаратора чотирьохрозрядних двійкових чисел потрібно чотири схеми однорозрядних компараторів (рис. 7.46), модифікованих з урахуванням інверсних значень функцій однорозрядного порівняння Ei і Li, два інвертори, а також логічні елементи 2АБОНЕ, 5АБОНЕ, 5ІНЕ, 2АБО, 3АБО, 4АБО і 5 АБО. Схема чотирьохрозрядного компаратора двійкових чисел показана на рис. 7.47.

Зазначимо, що в

цій схемі вхід

![]() нікуди не підключено, оскільки функція

виходу компаратора FA>B згідно

співвідношенню (7.55) реалізується як

заборона диз’юнкції вихідних функцій

FA=B і FA<B логічним елементом

2АБОНЕ.

нікуди не підключено, оскільки функція

виходу компаратора FA>B згідно

співвідношенню (7.55) реалізується як

заборона диз’юнкції вихідних функцій

FA=B і FA<B логічним елементом

2АБОНЕ.

|

Рис. 7.47. Схема чотирьохрозрядного компаратора

|

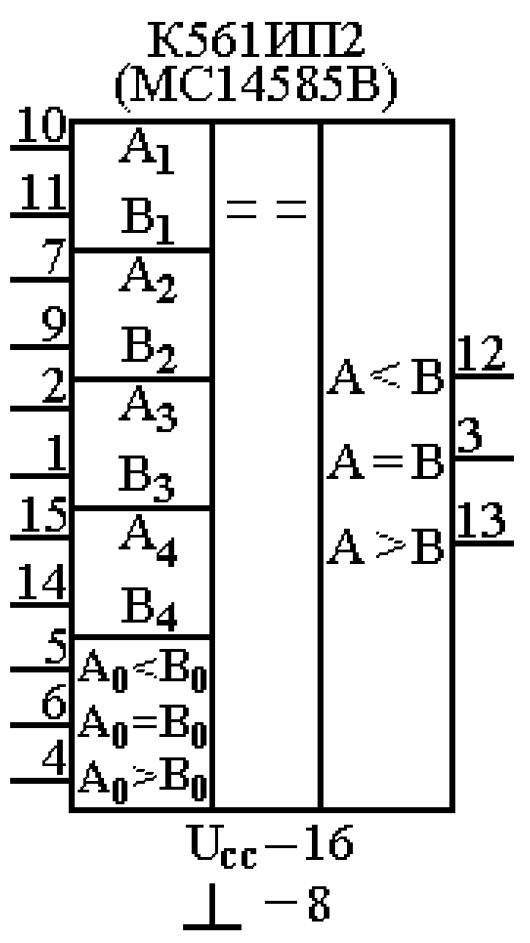

Прикладом компаратора, реалізованого за схемою показаною на рис. 7.47, є мікросхема К561ИП2 (функціональний аналог MC14585B). Її умовне графічне зображення і нумерація виводів показані на рис. 7.48а.

|

|

а |

б |

Рис. 7. 48. Умовне графічне зображення мікросхеми К561ИП2 (а), нарощування розрядності компараторів (б) |

|

В табл. 7.8. наведені параметри мікросхеми К561ИП2 при температурі 25 оС

Таблиця 7.8

Параметри інтегральної мікросхеми

компаратора К561ИП2

Позначення параметра |

Параметр |

Значення |

Одиниця виміру |

Ucc |

Напруга живлення |

2 – 18 |

В |

Icc |

Струм споживання у стані спокою |

600 (15 В) |

мкА |

TA |

Робочий діапазон температури |

55 – +125 |

оС |

U0вих (UOL) |

Вихідна напруга логічного нуля |

≤0,5 (5 В) ≤0,5 (15 В) |

В |

U1вих (UOH) |

Вихідна напруга логічної одиниці |

4,95 (5 В) 14,95 (15 В) |

В |

Iвх, Iin |

Вхідний струм |

0,1 |

мкА |

I0вих (IОL) |

Вихідний струм низького рівня |

0,88 (5 В) 8,8 (15 В) |

мА |

I1вих (IОH) |

Вихідний струм високого рівня |

0,88 (5 В) 8,8 (15 В) |

мА |

tзп1,0 (tPHL), tзп0,1 (tPLH) |

Час затримки поширення сигналу |

430 (5 В) 130 (15 В) |

нс |

tвм1,0(tTHL), tвим0,1(tTLH) |

Час вмикання і вимикання |

100 (5 В) 40 (15 В) |

нс |

Для нарощування розрядності компараторів їх вмикають так, як показано на рис. 7.48б. Виходи A<B, A=B, A>B компараторів молодших розрядів з’єднують з відповідними входами A0<B0, A0=B0, A0>B0 компараторів сусідніх старших розрядів. При цьому на входи нарощування A0<B0, A0=B0, A0>B0 компаратора самих молодших розрядів треба подати напругу низького рівня U0 (логічний „0”), тобто підключити їх до землі (рис. 7.48б).

7.3.8. Використання двійкових суматорів для порівняння чисел. Компаратори, що виконують порівняння чисел „на рівність та менше” (FA≤B) і „на більше” (FA>B) можуть бути побудовані на основі двійкових суматорів. Розглянемо принципи створення таких компараторів на прикладі чотирьохрозрядних цілих чисел A = A4A3A2A1 і B = B4B3B2B1, представлених в беззнаковому форматі з фіксованою крапкою (всі біти Ai, Bi є цифровими).

Нехай A < B, наприклад, A = 510 = 01012, а число B = 1310 = 11012. Виконаємо операцію віднімання A – B шляхом додавання до зменшуваного A від’ємника B, представленого у оберненому коді (без врахування циклічного перенесення):

![]() .

.

Як видно, при виконанні операції складання перенесення зі старшого біта результату дорівнює нулю P = 0. Нескладно переконатися, що P = 0 також при умові A = B.

Нехай тепер A > B, наприклад, A = 710 = 01112, а число B = 510 = 01012. Тоді при виконанні операції A – B означеним вище шляхом

![]()

виникає перенесення P = 1.

Таким чином, виникнення перенесення зі старшого біта результату при складанні числа A з оберненим кодом числа B (P = 1) свідчить про виконання умови A > B і, навпаки, коли таке перенесення відсутнє (P = 0) – про виконання умови A ≤ В. Тому суматор, на входи якого число B подається через інвертори, може виконувати функцію порівняння двійкових чисел. Результат порівняння формується на виході перенесення суматора P. Схема чотирьохрозрядного компаратора на суматорі, який виконує порівняння цілих двійкових чисел у беззнаковому форматі з фіксованою крапкою „на більше” і „на рівність та менше” показана на рис. 7.49.

|

Рис. 7.49. Використання суматора для порівняння цілих двійкових чисел, що представлені у беззнаковому форматі |