- •І.М. Черненко, о.І. Івон

- •Електронні елементи та вузли комп'ютерів

- •Дніпропетровськ, 2009

- •Передмова

- •Перелік вживаних скорочень

- •1.1. Загальні відомості, визначення

- •1.2. Способи представлення сигналів в обчислювальних пристроях. Системи числення.

- •Контрольні запитання

- •Розділ 2. Електронні ключі

- •2.1. Основні поняття. Класифікація, вимоги

- •2.2. Ключі на біполярних транзисторах

- •2.3 Ключі на польових (уніполярних) транзисторах

- •Контрольні запитання

- •Цифрової техніки

- •3.1 Математичні основи функціонування елементів та вузлів комп’ютерної електроніки

- •Контрольні запитання

- •4.1. Загальні поняття. Умовне зображення логічних елементів

- •4.2 Параметри елементів цифрової електроніки

- •4.3 Базові логічні елементи транзисторно-транзисторної логіки Шотткі (ттлш)

- •4.4 Базові логічні елементі на мон-транзисторах

- •4.5 Логічні елементи на польових транзисторах структури „метал-напівпровідник” з бар’єром Шотткі

- •Контрольні запитання

- •5.1 Загальні поняття і класифікація тригерів

- •5.2 Параметри тригерів

- •5.3 Асинхронні і синхронні rs-тригери

- •5.4 Асинхронні і синхронні d-тригери

- •5.5. Асинхронні і синхронні jk-тригери

- •5.7. Несиметричний тригер (тригер Шмітта)

- •5.8 Приклади використання тригерів

- •Контрольні запитання

- •Цифрових пристроїв

- •6.1. Інтегрувальні та диференціювальні

- •Сигналів на логічні елементи

- •6.2. Формувачі

- •6.3. Генератори поодиноких імпульсів (одновібратори)

- •6.4. Генератори (мультивібратори)

- •Контрольні запитання

- •7.1 Основні поняття, класифікація

- •7.2 Комбінаційні функціональні вузли

- •7.3. Комбінаційні арифметичні вузли

- •7.4. Послідовнісні вузли

- •Контрольні запитання

- •Та їх елементи

- •8.1 Основні поняття, класифікація

- •8.2 Параметри запам’ятовуючих пристроїв

- •8.3 Структури адресних запам’ятовуючих пристроїв

- •8.4. Динамічні запам’ятовуючі пристрої та їх елементи

- •8.5. Статичні запам’ятовуючі пристрої та їх елементи

- •8.6. Постійні запам’ятовуючі пристрої та їх елементи

- •Контрольні запитання

- •Список літератури Список основної літератури

- •Список рекомендованої літератури

8.6. Постійні запам’ятовуючі пристрої та їх елементи

Запам’ятовуючі пристрої типу ROM (пам’ять тільки для читання) зберігають інформацію, яка або зовсім не змінюється, або змінюється рідко і не в оперативному режимі роботи. Такі пристрої пам’яті, як відмічалось вище, використовують у комп’ютерній техніці для зберігання системних програм, наприклад BIOS, таблиць типових функцій (синуса, квадратичної функції та інших), кодів букв алфавітів тощо.

Постійні запам’ятовуючі пристрої як правило мають організацію 2DM, а при невеликій інформаційній ємності 2D. Тому програмування ПЗП полягає в тому чи іншому розміщенні елементів зв’язку між горизонтальними (адресними) і вертикальними (розрядними) лініями двомірної матриці запам’ятовуючих елементів.

8.6.1 Масочні і одноразово програмовані ПЗП. Найбільш прості ЗЕ використовують у постійних запам’ятовуючих пристроях, які програмують при виготовленні мікросхем пам’яті на промислових підприємствах. Програмування відбувається за допомогою шаблону (маски), тому такі запам’ятовуючі пристрої мають абревіатурне позначення МПЗП або ROM(M).

Елементом зв’язку між адресними і розрядними лініями в масочних ЗП можуть бути діоди, біполярні транзистори, МОН-транзистори тощо.

В матриці запам’ятовуючого масиву діодного ROM(M) з восьмибітовою організацією (рис. 8.14а) елементами зв’язку є діоди. Восьмибітове двійкове слово, яке зчитується з вертикальних (розрядних) ліній матриці, визначається наявністю або відсутністю зв’язку через діод між лініями адреси (ЛА) і розрядними лініями матриці. При наявності діоду високий рівень напруги U1, що надходить на вибрану ЛА відкриває діод, струм якого створює на резисторі напругу, що передається на розрядну лінію, і в даному розряді слова з’являється сигнал логічної „1” U1. Коли діод відсутній на розрядній лінії низький рівень напруги U0 (сигнал логічного „0”), оскільки ця лінія через резистор зв’язана з землею. В матриці, яка показана на рис. 8.14а, сигнал високого рівня напруги U1, що відповідно до адреси слова надійшов з виходу дешифратора на відповідну лінію ЛАj, забезпечує зчитування слова 11010001.

|

|

а |

б |

Рис. 8.14. Матриця діодних запам’ятовуючих елементів (а) і запам’ятовуючі елементи матричних ЗП на МОН-транзисторах (б)

|

|

У якості ЗЕ матричних ПЗП можуть бути використані також МОН-транзистори. Можлива така організація матриці ПЗП, в якій зв’язок між ЛА і розрядною лінією для тих розрядів слова, значення яких дорівнює одиниці, здійснюється через МОН-транзистор (рис. 8.14б). Для розрядів слова, значення яких дорівнює нулю, зв’язок між ЛА і розрядною лінією через транзистор відсутній. У цьому випадку при зверненні до ЗП МОН-транзистори, затвори яких з’єднані з адресними лініями, що знаходяться під рівнем напруги U0, закриті і не впливають на потенціал розрядних ліній, а МОН-транзистори, затвори котрих з’єднані з ЛА, на яку прийшов сигнал високого рівня U1, відкриваються і передають на розрядні лінії рівень напруги логічної „1” (U1 = Ucc). При відсутності зв’язку між ЛА і розрядною лінією через МОН-транзистор, на розрядній лінії, як і у діодній матриці (рис. 8.14а), сигнал логічного нуля U0 при будь-якому рівні сигналу на ЛА.

Часто матричні ПЗП на МОН-транзисторах організовують таким чином, що всі вузли матриці ЗМ мають зв’язки між лініями адреси і розрядними лініями (рис. 8.14б). Однак для МОН-транзисторів, які відповідають за зберігання нуля, збільшують товщину підзатворного оксиду (на рис. 8.14б заштрихована область). Це веде до збільшення порогової напруги транзистора. Тому матриця ПЗП містить МОН-транзистори з двома значеннями порогової напруги U01 для транзисторів з тонким шаром оксиду і U02 – для транзисторів з товстим шаром оксиду (U02 > U01). Високий рівень напруги зчитування UR, що надходить з виходу дешифратора на ЛА, вибирають в діапазоні U01 < UR < U02. В цьому випадку напруга UR не в змозі відкрити МОН-транзистор з товстим шаром оксиду. Тому такий транзистор постійно знаходиться у закритому стані і на розрядній лінії, з якою він утворює зв’язок, рівень напруги логічного „0” (U0). Транзистор з тонким шаром оксиду при цьому відкривається і передає на розрядну лінію сигнал логічної „1” (U1 = Ucc).

В одноразово програмованих постійних запам’ято-вуючих пристроях типу ППЗП або PROM програмування відбувається усуненням або створенням спеціальних перемичок. Початково в матриці ЗМ таких ППЗП всі ЗЕ мають (або не мають) перемички. Після програмування зостаються або виникають тільки необхідні перемички. Використовують різноманітні елементи пам’яті ППЗП. Приклади деяких з них показані на рис. 8.15.

|

|

|

а |

б |

в |

Рис. 8.15. Елементи пам’яті ППЗП з плавкими перемичками (а, б) і діодними парами (в)

|

||

Усунення частини перемичок при одноразовому програмуванні відбувається в ППЗП з плавкими перемичками. ЗЕ таких запам’ятовуючих пристроїв (рис. 8.15а,б) початково мають перемичку у вигляді тонкої плівки виготовленої з ніхрому, титановольфрамових сплавів або полікремнію. При програмуванні відповідна частина перемичок ліквідується шляхом розплавлення імпульсами струму достатньо великої амплітуди і тривалості.

Як видно зі схем ЗЕ на рис. 8.15а,б плавка перемичка створює зв’язок між лінією адреси ЛА і розрядною лінією. Сигнал вибірки високого рівня U1 на ЛА передається через відкритий діод і перемичку безпосередньо на розрядну лінію (рис. 8.15а) або він відкриває транзистор і на розрядну лінію через перемичку передається напруга U1 = Uсс (рис. 8.15б). Тому при наявності перемички ЗЕ зберігає логічну одиницю, при усуненні перемички зв’язок між ЛА і розрядною лінією зникає, і ЗЕ зберігає логічний нуль.

В ЗЕ з діодними парами (рис. 8.15в) початково електричний зв’язок між ЛА і розрядною лінією відсутній, оскільки вони з’єднані зустрічно увімкненими діодами. Тому початково такі ЗЕ зберігають логічний нуль. При програмуванні, коли на ЛА відносно розрядної лінії подається достатньо високий рівень напруги, зворотно зміщений діод пробивається з утворенням короткого замикання. Після цього ЛА має зв’язок з розрядною лінією тільки через один діод, оскільки інший діод після пробою перетворюється в провідникову перемичку. Сигнал вибірки високого рівня U1 передається на розрядну лінію через відкритий діод. Тому ЗЕ з пробитим зворотно зміщеним діодом зберігає логічну одиницю (рис. 8.15в).

|

Рис. 8.16. Конструкція ЗЕ на основі структури оксид- нітрид-оксид (ОНО) |

У початковому стані тонкі діелектричні шари структури ОНО мають високий опір близько 1015 Ом. Тому ЗЕ на основі такої структури, увімкнений між ЛА і розрядною лінією, не створює електричний зв’язок і з розрядної лінії при надходженні на ЛА сигналу вибірки U1 зчитується рівень логічного нуля U0. Якщо при програмуванні до елемента треба занести логічну одиницю на нього подають напругу, яка викликає пробій діелектричних шарів. При цьому полікремній дифундує в місті пробою крізь діелектричні шари ОНО, досягає другого електрода і створює коротке замикання. У такому стані ЗЕ на основі структури ОНО має опір близько 100 – 500 Ом і може перебувати у такому стані без зміни до 40 років. ЗЕ з пробитим шаром ОНО створює зв’язок між ЛА і розрядною лінією, тому він зберігає логічну одиницю. Мікросхеми ППЗП на ЗЕ зі структурою ОНО, порівняно з ППЗП на основі ЗЕ з плавкими перемичками і зустрічно увімкнутими діодами, є найбільш компактними і досконалими. Однак природно вони допускають тільки одноразове програмування. В сучасній комп’ютерній техніці масочні і одноразово програмовані постійні ЗП не використовують. Їм на зміну прийшли репрограмовані ПЗП (РПЗП), які дозволяють багаторазове перепрограмування.

В репрограмованих ЗП типів EPROM і EEPROM можливе стирання старої інформації і заміна її новою шляхом використання спеціального процесу, для проведення якого ЗП виводиться з робочого режиму. Робочий режим (зчитування даних) виконується з великою швидкістю, тоді як перепрограмування потребує виконання суттєво більш тривалих операцій. Основою ЗЕ пам’яті типу EPROM і EEPROM є МОН-транзистори з плаваючим затвором і МНОН-транзистори. Для розуміння принципу дії ЗЕ на таких транзисторах розглянемо їх структуру і фізичні принципи функціонування.

8.6.2. МОН-транзистори з плаваючим затвором. МОН-транзистор з плаваючим затвором (ПЗ) відрізняється від звичайного МОН-транзистора наявністю додаткового затвора (floating gate – плаваючий затвор), розташованого в шарі діелектрика, що відділяє керуючий затвор (control gate – керуючий затвор) від каналу транзистора. Наявність плаваючого затвору надає МОН-транзистору нові властивості, завдяки яким він може використовуватися в елементах пам’яті енергонезалежних ЗП. Структура n-канального МОН-транзистора з плаваючим затвором показана на рис. 8.17а. Як і в звичайних n-канальних МОН-транзисторах (рис. 2.11) в пластині кремнію p-типу створюють області n+-типу збагачені електронами. На ці області наносять металеві електроди – вивід стоку і вивід витоку транзистора. В підзатворному шарі діелектрика SiO2 створюють область з полікремнію легованого фосфором плаваючий затвор. Ця область має високу електропровідність і ізольована з усіх боків діелектриком SiO2. Тому заряд електронів (або дірок), захоплених на ПЗ може довгий час, не менше десяти років зберігатися на ньому. Зазначимо, що товщина шару SiO2 між плаваючим затвором і пластиною p-кремнію дуже мала і складає 5 – 10 нм, а товщина ПЗ повинна бути достатньо великою, щоб інжектовані електрони перед тим, як вони досягнуть другого шару SiO2 мали енергію близьку до енергії дна зони провідності полікремнію. Товщина шару SiO2 між ПЗ і керуючим затвором також повинна бути достатньо великою, щоб не допустити переносу носіїв заряду у ньому. Вивід керуючого затвора створюють нанесенням металевого шару (звичайно алюмінію або полікремнію) на шар SiO2 з плаваючим затвором (рис. 8.17а).

|

|

|

а |

б |

в |

Рис. 8.17. Структура n-канального МОН-транзистора з плаваючим затвором (а) та його умовне зображення (б) і стоко-затворні характеристики (в)

|

||

Для МОН-транзисторів з n-каналом (умовне зображення на рис. 8.17б) негативний заряд, захоплений на плаваючому затворі, екранує дію позитивної напруги прикладеної між керуючим затвором і витоком або підкладкою транзистора, тому порогова напруга, що відкриває транзистор, зростає порівняно з випадком, коли на ПЗ негативний заряд електронів відсутній.

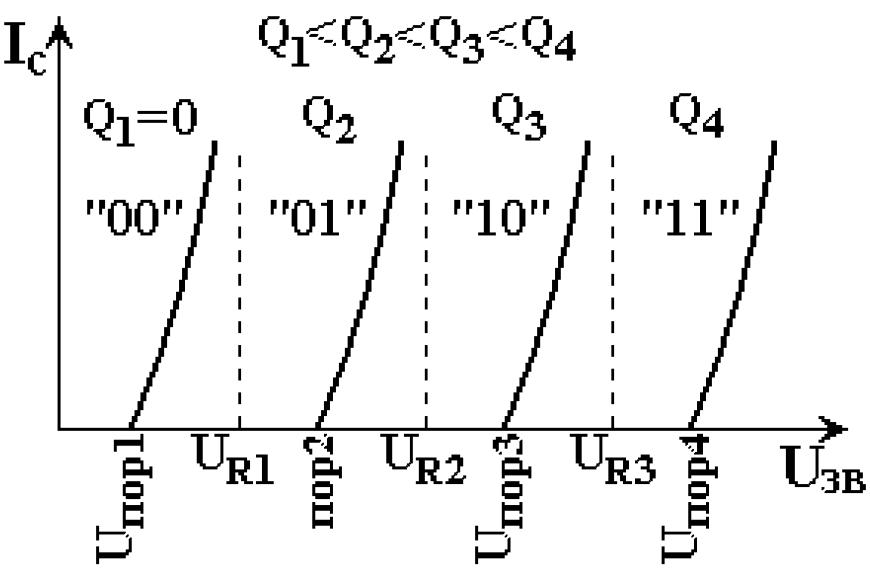

Таким чином, МОН-транзистор з ПЗ може знаходитися у двох станах: стані, коли на ПЗ заряд електронів відсутній і транзистор має порогову напругу Uпор1 і стані, коли ПЗ заряджений, і порогова напруга транзистора Uпор2 > Uпор1. Стоко-затворні характеристики МОН-транзистора з плаваючим затвором для двох його станів показані на рис. 8.17в (UR – напруга зчитування).

Як і у випадку запам’ятовуючого елемента DRAM, стан якого визначається наявністю або відсутністю заряду на запам’ятовуючому конденсаторі (див. підрозділ 8.4), будемо далі вважати, що МОН-транзистор зберігає логічну „1” при наявності негативного інформаційного заряду на його плаваючому затворі і зберігає логічний „0” при його відсутності (рис. 8.17в). Слід зазначити, що в деяких літературних джерелах, зокрема, присвячених флеш-пам’яті, приймається навпаки: за стан логічного „0” наявність інформаційного заряду на ПЗ, за стан „1” його відсутність. У такому випадку зчитування стану запам’ятовуючого елемента відбувається у негативній логіці (рис. 1.1), тобто при виконанні операції зчитування логічна „1” буде передаватися на розрядну лінію ЗМ як низький рівень напруги, а логічний „0” – як високий.

Запам’ятовуючий масив сучасних мікросхем РПЗП, зокрема, флеш-пам’яті, містить мільйони МОН-транзисторів з плаваючим затвором. Завдяки випадковим факторам, обумовленим варіацією для різних транзисторів розмірів, товщини діелектричних шарів, концентрації домішок, кількості електронів, захоплених на ПЗ і тому подібного, має місце розподіл порогової напруги, який ілюструє рис. 8.18а для флеш-пам’яті ємністю 1 Гбіт.

|

|

а |

б |

Рис. 8.18. Розподіл порогової напруги транзисторів у ЗМ флеш-пам’яті NOR ємністю 1 Гбіт (а): після стирання ультрафіолетовим світлом (1) та електричним шляхом (2); після програмування (на плаваючому затворі транзистора негативний заряд електронів) (3). Схема запам’ятовуючого елемента на МОН-транзисторі з ПЗ (б) |

|

При зчитуванні інформації з запам’ятовуючого елемента на МОН-транзисторі з ПЗ, один з варіантів схеми якого показано на рис. 8.18б, напруга зчитування UR на керуючому затворі транзистора, повинна задовольняти умові Uпор2 > UR >Uпор1 (рис. 8.18а). У цьому випадку при відсутності заряду на плаваючому затворі (UR > Uпор1) транзистор відкриється і підключає розрядну лінію до землі, що створює на ній рівень напруги логічного нуля U0, при наявності заряду на ПЗ, транзистор закритий (UR < Uпор2) і на розрядній лінії утримується високий рівень напруги логічної одиниці U1 = Uсс. Так працює ЗЕ в робочому режимі РПЗУ, тобто в режимі зчитування інформації.

Занесення заряду на плаваючий затвор МОН-тран-зисторів відбувається в режимі програмування. Розглянемо цей процес більш докладніше з залученням зонної діаграми МОН-транзистора з ПЗ, коли напруги на його виводах відсутні, а плаваючий затвор не заряджений (рис. 8.19а).

|

Рис.

8.19. Зонна діаграма МОН-транзистора з

плаваючим затвором при нульовій

напрузі на його виводах, плаваючий

затвор не заряджений (а). EcSi,

EvSi

– енергії дна зони провідності і

стелі валентної зони кремнію;

|

а |

|

|

|

б |

|

|

|

в |

З

енергетичної діаграми видно, що неосновний

носій заряду в p-кремнії

електрон, який знаходиться поблизу дна

зони провідності EcSi,

для переходу

на плаваючий

затвор повинен подолати енергетичний

бар’єр висотою

![]() .

Цей бар’єр він може подолати двома

шляхами, а саме: шляхом надбар’єрної

емісії і тунельного переходу (рис.

8.19б).

.

Цей бар’єр він може подолати двома

шляхами, а саме: шляхом надбар’єрної

емісії і тунельного переходу (рис.

8.19б).

У випадку надбар’єрної емісії для подолання бар’єру електрон повинен отримати енергію W > Eб. Це використовується в МОН-транзисторі з лавинною інжекцією заряду (ЛІЗ МОН - транзистор). Для занесення заряду на плаваючий затвор між стоком і витоком транзистора прикладається напруга Uсв ( +(5 – 6) В), а на затвор відносно витоку позитивна напруга близька до 2Uсв ( +12В). В транзисторі виникає n-канал і він відкривається. Оскільки довжина каналу мала ( 1 мкм) при вказаних напругах створюється сильне електричне поле з напруженістю близькою до 107 В/м. Тому електрони, що рухаються від витоку до стоку транзистора, набувають значну кінетичну енергію, достатню не тільки для подолання енергетичного бар’єру, але й для іонізації атомів каналу, тобто розвинення лавинного пробою. Такі електрони називають гарячими, оскільки їх дрейфова швидкість досягає або навіть перевищує теплову швидкість електрона (VТ ≈ 105 м/с). Гарячі електрони з енергію W > Eб, що здатні подолати бар’єр, який створює SiO2 (рис. 8.19а), втягуються позитивною напругою на керуючому затворі ( +12В) до області підзатворного діелектрика і захоплюються на плаваючому затворі. Після зняття напруги ці електрони зберігаються на ПЗ тривалий час. Слід зазначити, що в робочому режимі для зчитування інформації з ЗЕ використовуються напруги менші ніж при програмуванні (не більше +5 В), які практично не впливають на заряд, що зберігається на ПЗ МОН-транзистора.

Інший спосіб подолання електроном енергетичного бар’єру полягає в явищі квантово-механічного тунелювання. Це явище пов’язано з тим, що рух електрона в квантовій механіці описується за допомогою хвильової функції, яка є результатом розв’язання рівняння Шредингера. В загальному випадку хвильова функція є функцією часу і координат, а її квадрат дозволяє визначити ймовірність знайти електрон у точці простору з заданими координатами. Як випливає з рис. 8.19б завдяки просторової протяжності хвильової функції існує відмінна від нуля ймовірність знайти електрон з енергією W < Eб з іншого боку бар’єру. В цьому й полягає ефект тунельного переходу електрона з енергію W < Eб крізь енергетичний бар’єр. Слід зазначити, що ймовірність такого переходу має суттєву величину тільки для тонких бар’єрів з товщиною Lб 1 нм (10 Ǻ) або менше. Для бар’єрів з товщиною більше 5 – 10 нм вона дуже мала, але якщо до такого бар’єру прикласти напругу U (рис. 8.19в), то на рівні енергії вільного електрона Ec, товщина бар’єру Lб(U) зменшується і ймовірність тунельного переходу електрона зростає, вона стає тим більшою, чим більша величина напруги U. Через бар’єр, до якого прикладена напруга, потече тунельний струм Iт, що залежить від напруженості електричного поля в бар’єрі E = U/Lб згідно формулі Фаулера-Нордгейма:

![]() . (8.4)

. (8.4)

Сталі A і B в (8.4) залежать від типу напівпровідника і висоти бар’єру.

Механізм запису інформаційного заряду шляхом тунельної інжекції електронів з напівпровідника на плаваючий затвор МОН-транзистора пояснює зонна діаграма на рис. 8.20а. При позитивній напрузі Uзп ( +20 В) на керуючому затворі відносно підкладки p-Si виникає тунельний струм Iт електронів з напівпровідника крізь перший шар SiO2 між ПЗ і p-кремнієм. Електрони долають енергетичний бар’єр і накопичуються на ПЗ. Це відбувається завдяки тому, що за рахунок розсіяння на атомах полікремнію енергія електронів знижується до рівня, який відповідає дну зони провідності полікремнію. Тому електрони, що досягають другого шару SiO2 між плаваючим і керуючим затворами, не здатні подолати його ні шляхом надбар’єрної емісії ні шляхом тунельного переходу, оскільки їх енергія W < Eб, а товщина другого шару SiO2 більша за товщину першого шару. Величину заряду Q, що накопичується на плаваючому затворі за час , визначає співвідношення:

![]() , (8.5)

, (8.5)

де Iт(t) – величина тунельного струму крізь бар’єр у момент часу t.

Негативний заряд електронів Q(), захоплених на плаваючому затворі, створює електричне поле, яке направлене зворотно до електричного поля, що створює позитивна напруга на керуючому затворі МОН-транзистора. Тому величина напруженості поля Е в першому шарі діелектрика SiO2 зменшується з часом по мірі накопичення заряду на ПЗ. Це у відповідності з (8.4) веде до зменшення тунельного струму Iт. Тому через деякий час відбувається насичення накопичення заряду Q() на плаваючому затворі.

|

Рис. 8.20. Зонні діаграми МОН-транзистора з плаваючим затвором: а при записуванні інформаційного заряду імпульсом напруги +Uзп; б – при нульовій напрузі на затворі в режимі зберігання інформації Uзп = 0 В; в – при стиранні інформаційного заряду імпульсом напруги Uзп |

а |

|

|

|

б |

|

|

|

в |

Після зняття напруги програмування накопичений інформаційний заряд зберігається на плаваючому затворі. Цьому випадку відповідає зонна діаграма на рис. 8.20б. Час зберігання заряду визначається часом діелектричної релаксації структури, і як було зазначено вище, складає близько десяти років. Заряд на ПЗ впливає на порогову напругу МОН-транзистора. Зв’язок між пороговою напругою і величиною заряду Q на плаваючому затворі можна знайти на підставі еквівалентної схеми МОН-транзистора, яка наведена на рис. 8.21.

|

Рис. 8.21. Еквівалентна схема МОН-транзистора з плаваючим затвором |

![]() . (8.6)

. (8.6)

Коли на плаваючому затворі заряд відсутній, транзистор відкривається при напрузі на керуючому затворі UC = Uпор1. У цьому випадку згідно (8.6) напругу UF0 на плаваючому затворі визначає співвідношення:

![]() . (8.7)

. (8.7)

При наявності заряду Q на плаваючому затворі між ним і підкладкою транзистора виникає різниця потенціалів UF0 = Q/CFS, яка додається до різниці потенціалів, що визначається формулою (8.6). У цьому випадку

![]() . (8.8)

. (8.8)

З (8.8) випливає, що при наявності на ПЗ заряду Q, для досягнення напруги UF0, при якій формується n-канал, треба змінити напругу на керуючому затворі на значення UC = Uпор2. Тоді з урахуванням (8.7) і (8.8) можна записати:

![]() , (8.9)

, (8.9)

звідкіля отримаємо зв’язок між напругами Uпор1 і Uпор2:

![]() . (8.10)

. (8.10)

З (8.10) випливає, що при зарядженні плаваючого затвору МОН-транзистора негативним зарядом електронів (Q) порогова напруга зростає

![]() , (8.11)

, (8.11)

а коли ПЗ заряджений позитивно (+Q) зменшується.

Таким чином, відповідно до (8.10), (8.11) порогова напруга на керуючому затворі, при якій відкривається n-канальний МОН-транзистор з ПЗ, лінійно залежить від величини інформаційного заряду, захопленого на ПЗ. Така особливість дає можливість створити багаторівневий запам’ятовуючий елемент, здатний зберігати не один, а два й більше бітів інформації. Для цього при програмуванні ЗЕ треба забезпечити можливість розміщувати на плаваючому затворі транзистора дозовані за величиною заряди, а при зчитуванні інформації можливість розрізняти декілька рівнів порогової напруги.

|

Рис. 8.22. Стоко-затворні характеристики n-канального МОН-тран-зистора з ПЗ для зберігання двох бітів інформації |

Перед репрограмуванням попередня інформація, яку зберігає РПЗП, стирається, тобто інформаційні заряди вилучаються з плаваючих затворів МОН-транзисторів. Ця процедура виконується за допомогою операції стирання, яка може здійснюватися двома шляхами.

В РПЗП типу EPROM (РПЗП-УФ), побудованих на ЛІЗ МОН-транзисторах, заряд з плаваючого затвору видаляється шляхом опромінювання ультрафіолетовим (УФ) світлом. Високоенергетичні фотони УФ світла викликають внутрішній фотоефект у діелектричних шарах SiO2, оточуючих плаваючий затвор. Це на декілька порядків зменшує їх питомий опір і, як наслідок, на стільки ж порядків сталу часу діелектричної релаксації М = 0. Тому електрони з плаваючого затвору за не досить тривалий проміжок часу, близько 10 – 15 хвилин, стікають через перший шар SiO2 на напівпровідникову пластину p-кремнію, де рекомбінують з дірками.

В сучасних РПЗП типу EEPROM (РПЗП-ЕС) використовують електричний спосіб стирання інформації. Принцип стирання таким способом ілюструє зонна діаграма, показана на рис. 8.20в. Для швидкого розрядження плаваючого затвору на керуючий затвор транзистора відносно підкладки подають негативну напругу Uзп приблизно таку ж за абсолютною величиною, яка використовується при зарядженні ПЗ ( 20 В). За рахунок ефекту Фаулера-Нордгейма виникає тунельний струм електронів, і вони з ПЗ інжектуються крізь енергетичний бар’єр у пластину напівпровідника. Плаваючий затвор розряджається.

Слід зазначити, що при підборі придатної за величиною і тривалістю негативної напруги на керуючому затворі МОН-транзистора з n-каналом на його плаваючому затворі, за рахунок тунельної інжекції Фаулера-Нордгейма, можна накопичити позитивний заряд дірок. Такий заряд сприяє утворенню n-каналу в пластині кремнію p-типу. На відміну від розглянутих вище випадків (рис. 8.17в, рис. 8.22), коли на ПЗ накопичується негативний заряд електронів, порогова напруга МОН-транзистора з позитивно зарядженим ПЗ знижується, що випливає також із співвідношення (8.10). Спосіб стирання інформаційного заряду з накопиченням на плаваючому затворі транзисторів позитивного заряду дірок, використовується у флеш-пам’яті з архітектурою NAND (див. підрозділ 8.6.4).

Як можна бачити з рис. 8.18а (криві 1, 2) два способи стирання інформаційного заряду ведуть до різного розподілу порогової напруги Uпор1 запам’ятовуючих транзисторів. При стиранні шляхом опромінювання УФ світлом півширина функції розподілу Uпор1 менша ніж при використанні для цієї мети ефекту Фаулера-Нордгейма. Це пов’язано з тим, що у останньому випадку залежність Uпор1 від випадкових факторів суттєво більша.

8.6.3. МНОН-транзистори. МНОН-транзистор створюють у вигляді структури „металнітрид кремнію–оксид кремнію–напівпровідник” (МНОН-структура). На відміну від МОН-транзисторів, в яких інжектований інформаційний заряд захоплюється на плаваючому затворі, в МНОН-транзисторах він захоплюється на глибокі пастки в підзатворному діелектрику – нітриді кремнію Si3N4. Конструкція МНОН-транзистора показана на рис. 8.23.

|

Рис. 8.23. Структура МНОН-транзистора з n-каналом |

Зонна діаграма МНОН-структури при відсутності напруги на виводах транзистора і вільних пастках показана на рис. 8.24а. Запис інформаційного заряду відбувається шляхом тунельної інжекції електронів крізь шар SiO2 при прикладенні до затвору транзистора позитивної напруги (рис. 8.24б). Більша частина електронів, що подолала шар SiO2, захоплюється на глибокі пастки в області контакту нітриду кремнію з оксидом кремнію. Висока ефективність захоплення електронів обумовлена великим перерізом захоплення пасток ( 510-13 см2) і великою їх концентрацією в Si3N4 ( 31019 см -3). Частина електронів приймає участь у струмі наскрізної провідності Iн нітриду кремнію. Як і в МОН-транзисторі з плаваючим затвором по мірі накопичення заряду електронів поле в шарі SiO2 зменшується, що веде до насичення процесу накопичення заряду.

Після зняття напруги +Uзп нерівноважний заряд електронів, захоплених поблизу контакту оксиду з нітридом кремнію, зберігається тривалий час. Цьому випадку відповідає зонна діаграма на рис. 8.24в. Час зберігання інформаційного заряду в МНОН-транзисторі обмежує термічна емісія електронів з глибоких пасток. В нормальних умовах цей час складає близько 10 років.

|

|

а |

б |

|

Рис. 8.24. Зонні діаграми МНОН-транзистора: а при нульовій напрузі на його виводах і вільних глибоких пастках; б при записуванні інформаційного заряду імпульсом напруги +Uзп; в– при нульовій напрузі на затворі в режимі зберігання інформації Uзп = 0 В;г – при стиранні інформаційного заряду імпульсом Uзп |

в |

|

|

|

г

|

Стирання інформації, тобто повернення МНОН-структури транзистора в початковий стан, як і в МОН-транзисторі з плаваючим затвором можна здійснити двома шляхами:

опромінюванням ультрафіолетовим світлом з енергією фотонів більшою за ширину забороненої зони нітриду кремнію 5,1 еВ;

подачею на структуру імпульсу напруги, що має полярність протилежну за знаком напрузі, яка була використана при записуванні інформації.

Зонна діаграма МНОН-транзистора при стиранні інформації електричним шляхом показана на рис. 8.24г. При прикладенні негативної напруги до затвору транзистора електрони, захоплені на пастки, тунельним шляхом долають енергетичний бар’єр, створений шаром SiO2, і переходять у напівпровідник (p-Si) де рекомбінують з дірками.

Інформаційний заряд, що зберігається в МНОН-транзисторі з n-каналом, впливає на стоко-затворну характеристику цього транзистора таким же чином, як подібний заряд, захоплений на плаваючому затворі МОН-транзистора з n-каналом (див. підрозділ 8.6.2). Кількість електричних циклів „записування-стирання”, як для МНОН-транзисторів, так і для МОН-транзисторів з плаваючим затвором не менше 105.

8.6.4. Флеш-пам’ять. Розглянуті вище МОН-тран-зистори з плаваючим затвором і МНОН-транзистори є основою сучасних енергонезалежних репрограмованих запам’ятовуючих пристроїв з електричним перезаписом інформації. До таких пристроїв, зокрема, відноситься флеш-пам’ять. Флеш-пам’ять знайшла широке використання для зберігання програм BIOS комп’ютерів, у флеш нагромаджувачах, мікроконтролерах, засобах мобільного зв’язку, цифрових фотоапаратах тощо.

Назва флеш-пам’ять походить від англійського слова flash – спалах, що відображає не побудову, а особливість функціонування пристрою пам’яті. Ця особливість полягає в тому, що стирання інформації електричним шляхом у флеш-пам’яті відбувається досить швидко, але не для окремих слів, а повністю для всього пристрою або для окремих його блоків. Одночасне стирання всієї інформації в ЗП реалізується просто, але має той недолік, що навіть заміна одного слова потребує стирання і нового записування інформації повністю для всього пристрою пам’яті. Для багатьох використань це незручно. Тому поряд зі схемами одночасного стирання всього вмісту флеш-пам’яті існують схеми з блочною структурою, в яких запам’ятовуючий масив поділяється на блоки, які можна стирати незалежно один від одного. Інформаційна ємність таких блоків може складати від 128 Кбайт до 512 Кбайт.

При стиранні або занесенні заряду до МОН або МНОН транзисторів прикладається досить велика напруга, тому запам’ятовуючи елементи на їх основі з часом „спрацьовуються”. Для збільшення довговічності флеш-пам’яті в її роботі використовують спеціальні алгоритми керування, які забезпечують вирівнювання кількості перезаписів для різних блоків пам’яті. Сучасні мікросхеми флеш-пам’яті допускають від 105 до 106 перезаписів.

Перші мікросхеми флеш-пам’яті були похідними від мікросхем EPROM, які мали інтерфейс, що забезпечував довільний прямий доступ до комірок пам’яті. Це давало можливість безпосередньо з’єднувати мікросхеми флеш-пам’яті з шиною мікропроцесора і забезпечувало сумісність з його циклами записування та зчитування. Такий тип пам’яті відомий як флеш-память з архітектурою NOR. На сьогоднішній день існують два базових типи архітектури флеш-пам’яті NOR і NAND. У флеш-пам’яті обох типів використовують МОН-транзистори з ПЗ, але характер їх з’єднання в схемі запам’ятовуючого масиву є різним.

Запам’ятовуючий масив флеш-пам’яті з архітектурою NOR звичайно має структуру 2DM. Його організація показана на рис. 8.25. Функцію запам’ятовуючих елементів у матриці ЗМ виконують n-канальні МОН-транзистори з плаваючим затвором. По рядках матриці керуючі затвори транзисторів зв’язані лініями адреси (ЛАj, 0 j 2k–1), по стовпцях їх стоки об’єднані розрядними лініями (лініями біт), а витоки – лініями витоків. Лінії адреси, як і в інших типах ПЗП розглянутих вище служать для вибірки рядка ЗМ відповідно адресі, а слово даних Dn-1…D0 зчитується з розрядних ліній. Особливістю NOR архітектури є те, що кожен стовпець матриці ЗМ являє собою сукупність паралельно з’єднаних МОН-транзисторів з плаваючим затвором (рис. 8.25). В однорівневій флеш-пам’яті з архітектурою NOR кожен МОН-транзистор зберігає біт інформації, а сукупність транзисторів у рядку матриці запам’ято-вуючого масиву зберігає слово даних.

|

Рис. 8.25. Організація запам’ятовуючого масиву флеш-пам’яті з архітектурою NOR |

Назва NOR (скорочення від англійської Not OR АБОНЕ) походить від схожості за принципом дії стовпця матриці запам’ятовуючих елементів цього типу архітектури флеш-пам’яті з логічним елементом АБОНЕ (див. підрозділ 4.4.2). У такому елементі вихідне значення логічної змінної дорівнює 0, коли хоча б на одному вході елемента логічна 1. За аналогією для ЗМ флеш-пам’яті з архітектурою NOR (рис. 8.25), коли всі лінії витоків з’єднані з загальною шиною (землею), а розрядні лінії через резистор з шиною живлення (зовнішні елементи на схемі (рис. 8.25) не показані), низький рівень напруги логічного нуля U0 з’являється на розрядній лінії, якщо хоча б один з МОН-транзисторів, з’єднаних з нею відкритий, тобто на затвор такого транзистора подано високий рівень напруги логічної одиниці U1.

Базовими операціями флеш-пам’яті є стирання, записування (програмування) і зчитування інформації. Розглянемо як ці операції здійснюються у флеш-пам’яті з архітектурою NOR.

Перед занесенням нової інформації до флеш-пам’яті попередня інформація одночасно стирається у всіх комірках запам’ятовуючого масиву, для чого використовується ефект Фаулера-Нордгейма. Сутність операції стирання для флеш-пам’яті з архітектурою NOR пояснює рис. 8.26

|

|

а |

б |

Рис. 8.26. Увімкнення МОН-транзистора з ПЗ (а) і напруги на лініях матриці ЗМ при стиранні інформації у флеш-пам’яті з архітектурою NOR (б)

|

|

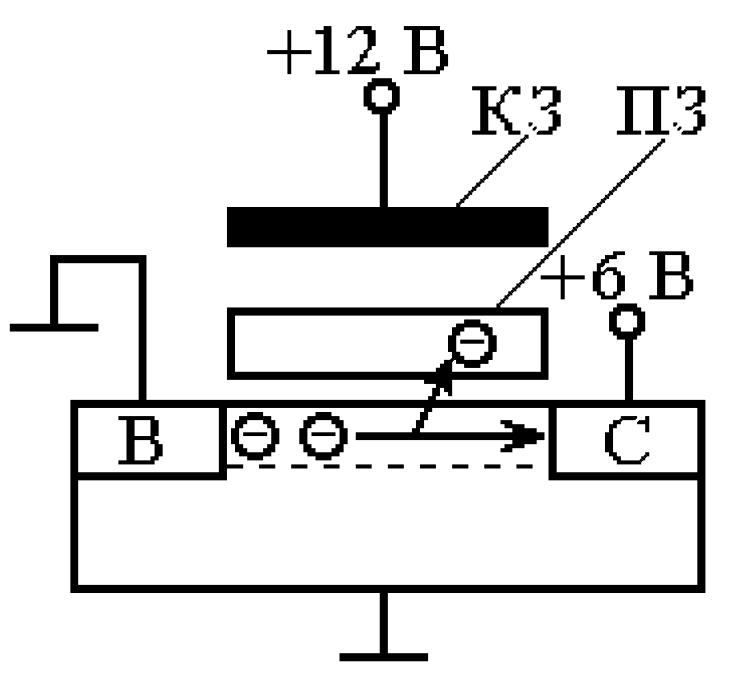

На всі лінії витоків запам’ятовуючого масиву подається напруга +12 В (зазначимо, що для різних мікросхем флеш-пам’яті ця напруга може бути різною, але вона приблизно у два рази перевищує напругу, що використовується при зчитуванні), а на лінії адреси і підкладки транзисторів низький рівень напруги U0 = 0 В (рис. 8.26б). Розрядні лінії залишаються вільними. За рахунок виникнення в транзисторах зустрічної тунельної інжекції електронів, накопичених на ПЗ, і дірок з p-кремнію та їх рекомбінації (рис. 8.26а), плаваючі затвори транзисторів розряджаються. Час стирання інформації в мікросхемах NOR флеш-пам’яті з інформаційною ємністю до 1 Гбіт не перевищує 1 с.

Існують також різновиди флеш-пам’яті з архітектурою NOR, в яких операція стирання здійснюється подачею на керуючий затвор транзистора негативної напруги ( 8,5÷ 10 В), а на витік позитивної напруги ( +5 В).

При програмуванні флеш-пам’яті з архітектурою NOR використовують режим лавинної інжекції для накопичення заряду на плаваючому затворі транзисторів (рис. 8.27а). Для цього на вибрану ЛА запам’ятовуючого масиву подається напруга +12 В, на інші ЛА та всі лінії витоків і підкладки транзисторів низький рівень напруги U0 = 0 В. На розрядних лініях, у залежності від значення біту слова, яке потрібно записати, встановлюються напруги U1 = + 6 В або U0 = 0 В (рис. 8.27б). В транзисторах, керуючий затвор яких підключено до ЛА з напругою +12 В, а стік до розрядної лінії з напругою U1 = + 6 В, утворюється n-канал з гарячими електронами, які долають енергетичний бар’єр, створений шаром SiO2 (див. підрозділ 8.6.2), і накопичуються на плаваючому затворі транзистора (рис. 8.27а). В транзисторах, на стік яких з розрядної лінії надходить сигнал U0 = 0 В, гарячі електрони не утворюються і заряд на ПЗ не накопичується. На рис. 8.27б МОН-транзистор, плаваючий затвор якого заряджається при програмуванні, обведено пунктирним колом.

|

|

а |

б |

Рис. 8.27. Увімкнення МОН-транзистора з ПЗ (а) і напруги на лініях матриці ЗМ при програмуванні флеш-пам’яті з архітектурою NOR (б)

|

|

Слід зазначити, що програмування флеш-пам’яті з архітектурою NOR за рахунок використання для цієї мети гарячих електронів, потребує досить великого електричного струму близько 110-4 А на один запам’ятовуючий транзистор. Типове значення швидкості програмування флеш-пам’яті з архітектурою NOR 0,5 Мбайт/с.

Сутність операції зчитування для NOR флеш-пам’яті пояснює рис. 8.28 На рис. 8.28б для фрагменту запам’ятовуючого масиву показано його комутацію при виконанні операції зчитування. В цьому випадку всі лінії витоків і підкладки транзисторів підключаються комутаційними транзисторами (на схемі не показані) до землі. На розрядні лінії через відкриті МОН-транзистори з p-каналом подається сигнал високого рівня напруги U1 = Ucc. Канали цих транзисторів виконують функцію стокових резисторів запам’ятовуючих транзисторів, підключених до розрядних ліній.

|

|

а |

б |

Рис. 8.28. Увімкнення МОН-транзистора з ПЗ (а) і напруги на лініях матриці ЗМ при зчитуванні інформації у флеш-пам’яті з архітектурою NOR (б)

|

|

В режимі зчитування, коли на всіх лініях адреси сигнал низького рівня U0, транзистори запам’ятовуючого масиву (рис. 8.25) закриті, і на всіх розрядних лініях ЗМ Di (0 ≤ i ≤ n-1) сигнал високого рівня напруги U1 = Uсс логічна одиниця. Вибірка слова в ЗМ при зчитуванні відбувається подачею з дешифратора на одну з ліній адреси сигналу вибірки UR +5 В (рис. 8.28б). Цей сигнал надходить на керуючі затвори запам’ятовуючих транзисторів рядка матриці ЗМ, в якому зберігається слово даних. Відкриваються МОН-транзистори рядка, плаваючий затвор яких незаряджений (для них UR >Uпор1, рис. 8.18а) і залишаються у закритому стані транзистори, що зберігають заряд на ПЗ (для них UR < Uпор2, рис. 8.18а), на рис. 8.28б такий транзистор обведено пунктирним колом). Всі транзистори, затвори яких підключені до не вибраних ЛА залишаються у закритому стані і не впливають на потенціал розрядних ліній. Відкриті транзистори підключають розрядні лінії до землі і на них встановлюється низький рівень напруги U0 = 0 В логічний „0” (рис. 8.28б). Транзистори вибраного рядка матриці ЗМ, що залишились у закритому стані не змінюють напругу розрядних ліній. На таких лініях високий рівень напруги U1 = Uсс – логічна „1” (рис. 8.28б). Таким чином з розрядних ліній ЗМ (рис. 8.25) зчитується слово даних Dn-1…Di…D0. Типове значення швидкості зчитування для флеш-пам’яті з архітектурою NOR 100 Мбайт/с.

Позитивною якістю флеш-пам’яті з архітектурою NOR є висока швидкість зчитування і довільний доступ до інформації. Тому інтерфейс флеш пам’яті з архітектурою NOR призначено для прямого доступу до пам’яті: окремі адреси, дані і керуючі лінії. Це дає можливість безпосередньо з’єднувати таку флеш-пам’ять з процесором для виконання програмного коду, який зберігається в ній. Тому в сучасних комп’ютерах флеш-память з архітектурою NOR використовується для зберігання BIOS.

Недоліками флеш пам’яті з архітектурою NOR є досить повільна швидкість стирання і записування інформації та досить великий розмір ЗЕ, наслідком чого є погане масштабування. Це пов’язано з тим, що спосіб організації матриці ЗЕ в архітектурі NOR потребує підведення окремого ізольованого індивідуального електроду до кожного запам’ятовуючого транзистора, а це не дає можливості нарощувати ступінь інтеграції мікросхем пам’яті шляхом зменшення розмірів транзисторів. Зазначимо, що на сьогоднішній день освоєно випуск мікросхем флеш-пам’яті з архітектурою NOR ємністю до 1 Гбіт.

Розвиток NAND архітектури флеш-пам’яті почався після опанування архітектури NOR. У флеш-пам’яті з архітектурою NAND МОН-транзистори вмикаються в стовпцях матриці ЗМ не паралельно, як в архітектурі NOR, а послідовно-паралельно і дані зчитуються та записуються сторінками (ємність сторінки сотні байт або декілька кілобайт). Це не дає можливість зчитувати або програмувати інформацію індивідуально, окремими словами, як в NOR, тому інтерфейс вводу-виводу флеш-пам’яті з архітектурою NAND не дозволяє безпосередній довільний доступ до одиниць інформації, що зберігаються в запам’ятовуючому масиві. Така особливість NAND флеш-пам’яті робить проблематичним її використання, наприклад, в мікроконтролерах, де потрібен швидкий довільний доступ до даних за адресою, але вона добре пристосована для використання в нагромаджувачах даних, де успішно конкурує з нагромаджувачами на гнучких і жорстких магнітних дисках.

Структура матриці запам’ятовуючого масиву флеш-пам’яті з архітектурою NAND показана на рис. 8.29.

|

Рис. 8.29. Організація запам’ятовуючого масиву флеш-пам’яті з архітектурою NAND

|

Запам’ятовуючі МОН-транзистори з ПЗ (VT2 – VTm+1) в такій структурі утворюють послідовний ланцюг, який з’єднується з розрядною лінією і лінією витоків через ключеві МОН-транзистори VT1, VTm+2. Тому назва NAND (скорочення від англійської Not AND ІНЕ) походить від схожості за принципом дії такого ланцюга транзисторів з логічним елементом ІНЕ (див. підрозділ 4.4.2). На виході елемента ІНЕ логічний 0, коли на всіх його входах логічна 1. За аналогією для архітектури запам’ятовуючого масиву типу NAND (рис. 8.29), якщо його розрядні лінії з’єднані через резистор з шиною живлення, а лінія витоків з землею, напруга логічного нуля U0 має місце на будь-якій з розрядних ліній тільки тоді, коли хоча б в одному послідовному ланцюзі транзисторів, підключених до неї, всі транзистори будуть відкриті, тобто на їх затворах високий рівень напруги логічної одиниці U1. Завдяки послідовному увімкненню МОН-транзисторів з ПЗ немає потреби створювати окрему ізольовану лінію зв’язку до кожного транзистора, як у випадку флеш-пам’яті з архітектурою NOR. Тому ЗМ флеш-пам’яті з архітектурою NAND при тій же інформаційній ємності займає на кристалі меншу площу, ніж у випадку архітектури NOR, а його елементи добре масштабуються. Оскільки для флеш-пам’яті з архітектурою NAND запам’ятовуючі транзистори підключаються до розрядних ліній ЗМ у вигляді послідовного ланцюга, принципи організації запам’ятовуючого масиву і звернення до нього при зчитуванні та записуванні інформації значно відрізняються від відповідних принципів, що використовуються у флеш-пам’яті з архітектурою NOR.

Головна відмінність полягає в тому, що запам’ятовуючий масив флеш-пам’яті з архітектурою NAND не має ліній адреси (ЛА), за допомогою яких відбувається прямий доступ до будь-якої комірки пам’яті, що містить слово даних. Для ЗМ характерна сторінкова організація. Сторінка це найменша область флеш-пам’яті з архітектурою NAND, яка підтримує операції зчитування та записування інформації. Керуючі затвори МОН-транзисторів з ПЗ, що належать до однієї сторінки, об’єднані між собою лініями слів (сторінок) ЛС (рис. 8.29). Сторінка містить множину одиниць інформації – двійкових слів даних, тому її довжина може складати від 512 байт до 4 Кбайт. Сторінки об’єднані в блоки. Блок це найменша область флеш-пам’яті, яка може бути стерта за одну операцію стирання. Кількість сторінок у блоці дорівнює числу m послідовно увімкнутих МОН-транзисторів з плаваючим затвором (рис. 8.29), а інформаційна ємність блоку дорівнює добутку кількості сторінок на їх довжину. Для звернення до окремих блоків у запам’ятовуючому масиві при виконанні базових операцій флеш-пам’яті використовуються лінії вибірки (ЛВ). Кожен блок має дві такі лінії ЛВj і ЛВj, які з’єднують між собою затвори комутаційних МОН-транзисторів рядка матриці ЗМ. При наявності сигналу високого рівня напруги U1 на ЛВj відкриваються комутаційні транзистори, які підключають послідовні ланцюги запам’ятовуючих транзисторів вибраного блоку до розрядних ліній. При високому рівні напруги на ЛВj ці ланцюги з’єднуються з лінією витоків блоку (рис. 8.29).

Розміри сторінок і блоків різняться в мікросхемах флеш-пам’яті NAND різних виробників і поколінь. Так, наприклад, ЗМ флеш-пам’яті з інформаційною ємністю 8 Гбіт, яка реалізована за 50 нм технологією, має розмір сторінки 4 Кбайт, а кожен її блок ємністю 256 Кбайт містить m = 64 сторінки. Зазначимо, що в кожній сторінці NAND флеш-пам’яті поряд з даними записується інформація, призначена для контролю і корекції помилок. Так, сторінки 50 нм NAND флеш-пам’яті, які мають розмір 4 Кбайт поряд з 4096 байтами даних містять 128 байт для кодів контролю і корекції помилок.

Для стирання і програмування флеш-пам’яті з архітектурою NAND в запам’ятовуючих транзисторах використовується ефект Фаулера-Нордгейма. Тому струм програмування для такої пам’яті набагато менший, ніж у випадку NOR архітектури, де для програмування використовуються гарячі електрони. Величина струму через запам’ятовуючий транзистор при програмуванні флеш-пам’яті з архітектурою NAND складає 510-9 А, але напруга для стирання і записування інформації суттєво більша ніж для флеш-пам’яті з NOR архітектурою і складає 20 В. Використання у флеш-пам’яті з архітектурою NAND підвищеної напруги при виконанні операції стирання приводить до того, що плаваючі затвори МОН-транзисторів не тільки звільнюються від негативного заряду електронів, але й набувають позитивний заряд. Це відбувається за рахунок того, що при підвищеній напрузі ПЗ тунельним шляхом втрачає більше електронів, ніж було захоплено на ньому при програмуванні. Як наслідок, на плаваючому затворі залишається позитивний заряд дірок. Цей заряд приводить до утворення n-каналу в МОН-транзисторі з плаваючим затвором. Тому після виконання операції стирання, навіть при нульовій напрузі на керуючому затворі, всі запам’ятовуючі транзистори флеш-пам’яті з NAND архітектурою відкриті.

Розподіл порогової напруги МОН-транзисторів з плаваючим затвором в ЗМ флеш-пам’яті з архітектурою NAND показано на рис. 8.30. Згідно цьому розподілу напруга UR, що використовується при зчитуванні для вибірки сторінки із блоку даних, повинна відповідати умові Uпор1 UR Uпор2. У флеш-пам’яті з архітектурою NAND, як правило, використовують низький рівень напруги UR = U0 = 0 В. Ця напруга подається на лінію слова вибраного рядка матриці запам’ятовуючого масиву (рис. 8.29), на інші лінії слова подається напруга UP, яка забезпечує відкривання всіх інших послідовно з’єднаних з вибраним запам’ятовуючих транзисторів. Напруга UP називається напругою пропускання і обирається виходячи з умови UP > Uпор2 (рис. 8.30). Звичайно, для флеш-пам’яті з архітектурою NAND значення UP складає 4,5 – 5 В. Таким чином, при наявності напруги UR на одній лінії слова вибраного блоку, а на інших – напруги пропускання UP, потенціал будь-якої розрядної лінії ЗМ при зчитуванні інформації буде визначатися станом одного з m послідовно включених транзисторів (VT2 – VTm+1, рис. 8.29), а саме того, на керуючому затворі якого сигнал низького рівня напруги UR = U0 = 0 В.

|

Рис. 8.30. Розподіл порогової напруги транзисторів у запам’ято-вуючому масиві флеш-пам’яті з архітектурою NAND: після стирання електричним шляхом (1) та УФ світлом (2) і після програмування (на плаваючому затворі негативний заряд електронів) (3)

|

Розглянемо більш докладніше виконання базових операцій флеш-пам’яті з архітектурою NAND.

Стирання інформації в NAND флеш-пам’яті здійснюється поблочно. Схеми увімкнення МОН-транзистора з плаваючим затвором і послідовного ланцюга транзисторів для одного розряду блоку сторінок при виконанні операції стирання показані на рис. 8.31а та рис. 8.31б, відповідно.

За рахунок виникнення в запам’ятовуючому транзисторі (рис. 8.31а) тунельної інжекції Фаулера-Нордгейма через шар діелектрика між плаваючим затвором і підкладкою, електрони з ПЗ переходять на підкладку p-типу де рекомбінують з дірками. При напрузі стирання, що використовується у флеш-пам’яті з архітектурою NAND кількість електронів, які виходять з ПЗ перевищує кількість електронів, що були накопичені на ньому при програмуванні, тому плаваючий затвор заряджається позитивно. Це веде до утворення в підзатворній області транзистора n-каналу. Тому після стирання інформації, що зберігалась в блоці, всі його запам’ятовуючі транзистори відкриті.

|

|

а |

б |

Рис. 8.31. Увімкнення МОН-транзистора з ПЗ (а) і ланцюга транзисторів одного розряду в блоці сторінок при виконанні у флеш-пам’яті з NAND архітектурою операції стирання (б) |

|

Операцію програмування NAND флеш-пам’яті пояснює рис. 8.32. Перед програмуванням відбувається стирання попередньої інформації, що зберігає блок. При цьому плаваючі затвори всіх запам’ятовуючих транзисторів блоку набувають позитивний заряд, завдяки якому в цих транзисторах існують n-канали і вони відкриті. Тому коли сигнал високого рівня напруги на лінії ЛВj (рис. 8.32б), відкриває комутаційні МОН-транзистори, затвори яких з’єднані з цією лінією, потенціал будь-якої розрядної ліній розповсюджується на стоки та витоки всіх послідовно увімкнених запам’ятовуючих транзисторів, що підключені до цієї розрядної лінії.

Якщо при програмуванні до якогось з m послідовно увімкнених запам’ятовуючих транзисторів треба записати логічну „1” (на рис. 8.32б такий транзистор обведено пунктирним колом), тобто зарядити ПЗ транзистора негативним зарядом електронів, на його керуючий затвор подається напруга +20 В, а на стік і витік низький рівень напруги U0 = 0 В (рис. 8.32а). В цьому випадку між керуючим затвором і n-каналом транзистора різниця потенціалів 20 В, яка викликає тунельний струм електронів через шар діелектрика на плаваючий затвор. Електрони за рахунок рекомбінації нейтралізують позитивний заряд дірок на ПЗ і заряджають плаваючий затвор негативним зарядом. Як наслідок n-канал в транзисторі зникає і він закривається. При записуванні логічного „0” на стік і витік транзистора подається напруга +10 В. В цьому випадку різниця потенціалів між керуючим затвором транзистора, підключеним до обраної ЛС, на якій +20 В, і n-каналом транзистора складає 10 В. Ця напруга недостатня для виникнення тунельного струму, тому стан транзистора після програмування залишається незмінним, тобто на його ПЗ позитивний заряд, в транзисторі існує n-канал і він відкритий.

|

|

а |

б |

Рис. 8.32. Увімкнення МОН-транзистора з ПЗ при записуванні логічної одиниці (а) і послідовних ланцюгів транзисторів в блоці при виконанні операції програмування флеш-пам’яті з архітектурою NAND (б) |

|

Виконання операції запису інформації до запам’ято-вуючого масиву флеш-пам’яті з NAND архітектурою ілюструє рис. 8.32б. Процес записування інформації до вибраного блоку відбувається сторінками. Для цього значення бітів сторінки у вигляді напруг 0 В (для записування логічної „1”) і 10 В (для записування логічного „0”) подаються на розрядні лінії ЗМ. Сторінка записується в рядок матриці, лінія слова якого знаходиться під напругою 20 В, на інші ЛС блоку подається напруга 10 В. Вибірка блоку, до якого відбувається записування сторінки, здійснюється напругою високого рівня U1 = 5 В на лінії вибірки ЛВj, на інших подібних лініях ЗМ низький рівень U0 = 0 В. Напруга U1 = 5 В відкриває комутаційні транзистори, які підключають послідовні ланцюги запам’ятовуючих транзисторів до розрядних ліній запам’ятовуючого масиву (рис. 8.32б). При цьому завдяки відкритому стану запам’ятовуючих транзисторів на їх стоках і витоках встановлюється потенціал розрядної лінії до якої вони підключені. Зазначимо, що при виконанні операції програмування, лінія витоків відключена сигналом низького рівня U0 = 0 В на затворах комутаційних МОН-транзисторів, які з’єднані з лінією вибірки ЛВj.

Оскільки всі МОН-транзистори з ПЗ вибраного блоку відкриті і підключені до розрядних ліній відкритими комутаційними транзисторами, відбувається їх програмування згідно механізму описаному вище. Негативний заряд плаваючого затвору (запис логічної „1”) набувають транзистори, на керуючий затвор яких з виділеної лінії слова надходить напруга 20 В, а на стік і витік з розрядної лінії напруга низького рівня U0 = 0 В (рис. 8.32б). Всі інші транзистори блоку не змінюють свій стан.

Оскільки за одну операцію запису у флеш-пам’ять з архітектурою NAND записується не слово даних, як у флеш-пам’яті з архітектурою NOR, а ціла сторінка, що містить множину слів даних, швидкість програмування для такої пам’яті суттєво більша і звичайно складає близько 4 Мбайт/с.

Зчитування інформації у флеш-пам’яті з архітектурою NAND, як і програмування, відбувається сторінками. Комутацію ліній запам’ятовуючого масиву для операції зчитування на прикладі двох розрядів блоку, до якого відбувається звернення, показано на рис. 8.33.

Вибірка блоку в ЗМ здійснюється сигналами високого рівня U1 = 5 В на лініях вибірки ЛВj, ЛВj. Лінії витоків ЗМ при зчитуванні підключаються до землі, а розрядні лінії через p-канали відкритих МОН-транзисторів до шини живлення.

|

Рис. 8.33. Напруги на лініях матриці ЗМ флеш-пам’яті з архітектурою NAND для операції зчитування |

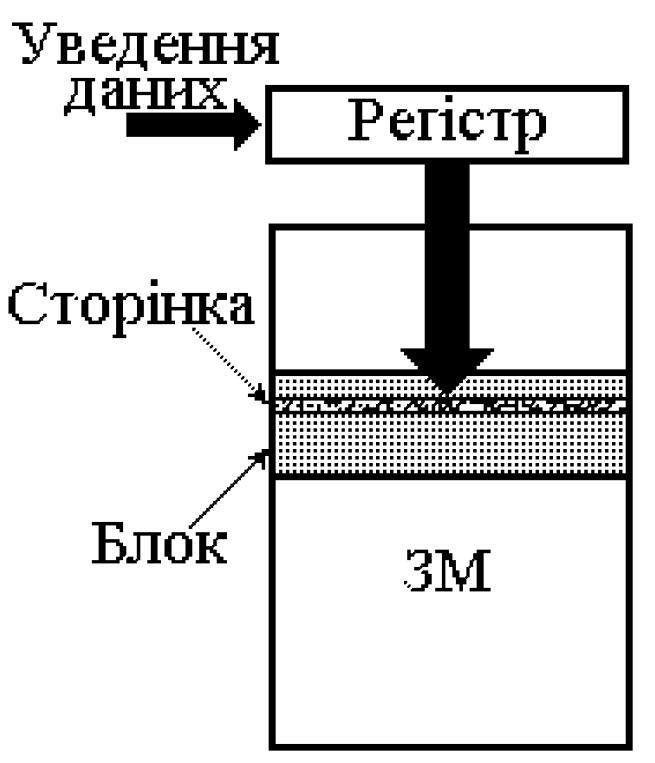

Насамперед зазначимо, що у флеш-пам’яті з NAND архітектурою дані трансформуються сторінками між запам’ятовуючим масивом і внутрішнім регістром, а обмін даними між внутрішнім регістром і зовнішньою 8 бітовою (16 бітовою) шиною здійснюється байтами (двома байтами для 16 бітової шини). Блочно-сторінкову структуру флеш-пам’яті з NAND архітектурою і її взаємодію з зовнішньою шиною ілюструє рис. 8.34.

|

Рис. 8.34. Блочно-сторінкова структура флеш-пам’яті з архітектурою NAND

|

Запам’ятовуючий масив флеш-пам’яті з архітектурою NAND має трьохмірну організацію і складається з двомірних матриць ЗМ, наведених на рис. 8.29. Кількість таких матриць дорівнює розрядності зовнішньої шини даних, отже при восьмирозрядній шині їх вісім. Таким чином, одна двомірна матриця запам’ятовуючого масиву (рис. 8.29) зберігає один з восьми бітів байтів, якими обмінюється пам’ять з зовнішньою шиною. Цей обмін керується спеціальними командами, які забезпечують передачу даних між ЗМ та регістром і регістром та зовнішньою шиною при виконанні базових операцій флеш-пам’яті. Оскільки обмін даними між зовнішньою шиною і внутрішнім регістром здійснюється байтами послідовно у часі, флеш-пам’ять з архітектурою NAND має по суті послідовний доступ до інформації, яка в ній зберігається. Цей доступ здійснюється наступним чином.

При виконанні операції програмування сторінка даних послідовно у часі байт за байтом уводиться з зовнішньої шини даних до внутрішнього регістру NAND флеш-пам’яті, з якого вже цілком перезаписується за адресою блока і сторінки в запам’ятовуючий масив (рис. 8.35а).

|

|

|

а |

б |

в |

Рис. 8.35. Виконання операцій програмування (а), стирання (б) і зчитування (в) у флеш-пам’яті з архітектурою NAND

|

||

При виконанні операції зчитування сторінка даних, яка вибрана з запам’ятовуючого масиву згідно її адресі в блоці та адресі самого блоку в ЗМ, записується до внутрішнього регістру, звідкіля послідовно у часі байт за байтом передається на зовнішню шину даних (рис. 8.35в). Стирання інформації у флеш-пам’яті не потребує обміну даними між запам’ятовуючим масивом та внутрішнім регістром (рис. 8.35б). Цю операцію ініціює команда, яка містить адресу блоку, що стирається. Згідно цієї адреси блок вибирається в ЗМ і відбувається його стирання так, як це було описано вище (рис. 8.31).

Таким чином, на відміну від флеш-пам’яті з архітектурою NOR, яка забезпечує прямий довільний доступ за адресою до будь-якого двійкового слова, що зберігається в запам’ятовуючому масиві, у флеш-пам’яті з архітектурою NAND такий доступ можна отримати тільки через сторінку даних, яка поряд з запитаним словом зберігає багато інших двійкових слів. Тому флеш-пам’ять з архітектурою NAND орієнтована насамперед на зберігання даних файлового типу. Завдяки цьому пам’ять з такою архітектурою, зокрема, знайшла широке використання у флеш-нагромад-жувачах, які на сьогоднішній день успішно конкурують з традиційними нагромаджувачами на жорстких і гнучких магнітних дисках.

Наприкінці наведемо порівняльну таблицю параметрів флеш-пам’яті з архітектурою NOR і NAND.

Таблиця 8.1

Параметри флеш-пам’яті (порівняльна таблиця)

Параметр |

NOR |

NAND |

Максимальна інформаційна ємність (2007 р.) |

1 Гбіт |

8 Гбіт |

Розмір сектору/блоку |

1 Мбіт |

1 Мбіт |

Кількість розрядів зовнішньої шини |

8, 16, 32 |

8, 16 |

Довжина слова/сторінки |

16 байт |

2112 байт |

Час довільного доступу |

60 нс |

25 мкс |

Час послідовного доступу |

25 нс |

30 нс |

Час програмування слова/сторінки |

80 мкс |

500 мкс |

Час стирання |

1 с на сектор |

1 мс на блок |

Пропускна здібність при зчитуванні |

35 Мбайт/c (8) |

24 Мбайт/c (8) |

Пропускна здібність при програмуванні |

0,19 Мбайт/c (8) |

3,75 Мбайт/c (8) |