- •І.М. Черненко, о.І. Івон

- •Електронні елементи та вузли комп'ютерів

- •Дніпропетровськ, 2009

- •Передмова

- •Перелік вживаних скорочень

- •1.1. Загальні відомості, визначення

- •1.2. Способи представлення сигналів в обчислювальних пристроях. Системи числення.

- •Контрольні запитання

- •Розділ 2. Електронні ключі

- •2.1. Основні поняття. Класифікація, вимоги

- •2.2. Ключі на біполярних транзисторах

- •2.3 Ключі на польових (уніполярних) транзисторах

- •Контрольні запитання

- •Цифрової техніки

- •3.1 Математичні основи функціонування елементів та вузлів комп’ютерної електроніки

- •Контрольні запитання

- •4.1. Загальні поняття. Умовне зображення логічних елементів

- •4.2 Параметри елементів цифрової електроніки

- •4.3 Базові логічні елементи транзисторно-транзисторної логіки Шотткі (ттлш)

- •4.4 Базові логічні елементі на мон-транзисторах

- •4.5 Логічні елементи на польових транзисторах структури „метал-напівпровідник” з бар’єром Шотткі

- •Контрольні запитання

- •5.1 Загальні поняття і класифікація тригерів

- •5.2 Параметри тригерів

- •5.3 Асинхронні і синхронні rs-тригери

- •5.4 Асинхронні і синхронні d-тригери

- •5.5. Асинхронні і синхронні jk-тригери

- •5.7. Несиметричний тригер (тригер Шмітта)

- •5.8 Приклади використання тригерів

- •Контрольні запитання

- •Цифрових пристроїв

- •6.1. Інтегрувальні та диференціювальні

- •Сигналів на логічні елементи

- •6.2. Формувачі

- •6.3. Генератори поодиноких імпульсів (одновібратори)

- •6.4. Генератори (мультивібратори)

- •Контрольні запитання

- •7.1 Основні поняття, класифікація

- •7.2 Комбінаційні функціональні вузли

- •7.3. Комбінаційні арифметичні вузли

- •7.4. Послідовнісні вузли

- •Контрольні запитання

- •Та їх елементи

- •8.1 Основні поняття, класифікація

- •8.2 Параметри запам’ятовуючих пристроїв

- •8.3 Структури адресних запам’ятовуючих пристроїв

- •8.4. Динамічні запам’ятовуючі пристрої та їх елементи

- •8.5. Статичні запам’ятовуючі пристрої та їх елементи

- •8.6. Постійні запам’ятовуючі пристрої та їх елементи

- •Контрольні запитання

- •Список літератури Список основної літератури

- •Список рекомендованої літератури

7.4. Послідовнісні вузли

Послідовнісні цифрові вузли будують на логічних елементах і елементах пам’яті – тригерах. До таких вузлів, на сам перед, відносяться регістри і лічильники, які знайшли широке використання в комп’ютерній техніці.

7.4.1. Загальна характеристика і класифікація регістрів. Регістр (від латинської registrum книга для запису) – це послідовнісний цифровий вузол, призначений для прийому, зберігання, перетворення і видачі багаторозрядних двійкових слів. Для зберігання кожного біту двійкового слова в регістрі використовується один тригерний елемент пам’яті. Отже n-розрядний регістр складається з n тригерів. Для побудови регістрів використовують універсальні D і JK тригери, а також RS тригери. Окрім тригерних елементів пам’яті схема регістра може містити комбінаційні вузли на логічних елементах, які забезпечують певні можливості регістра стосовно прийому, видачі та перетворення багаторозрядних двійкових слів. Елементарна дія, що виконує регістр над двійковим словом називається мікрооперацією. У загальному випадку регістри можуть виконувати наступні мікрооперації:

Обнуління або очистка, тобто установка всіх тригерів регістра в нульовий стан;

Прийом двійкового слова (запис або увід слова);

Зберігання двійкового слова;

Видача двійкового слова (зчитування або вивід слова);

Зсув двійкового слова вправо або вліво на задане число розрядів.

За способом організації зв’язків між тригерами регістри поділяються на паралельні і послідовні. В паралельних регістрах зв’язки між інформаційними входами і виходами тригерів сусідніх розрядів відсутні. Такі регістри по суті являють собою набір тригерів, в які можливо вводити або виводити одночасно у всіх розрядах двійкові слова, представлені в паралельному коді. Паралельні регістри називають також статичними регістрами. В послідовних регістрах інформаційні входи і виходи тригерів сусідніх розрядів зв’язані між собою. Це дає можливість передавати біт інформації з даного тригера в сусідній, тобто реалізувати мікрооперацію зсуву двійкового слова. Тому послідовні регістри називають регістрами зсуву. Зазначимо також, що загальними зв’язками між тригерами, як у статичних регістрах, так і в регістрах зсуву є ланцюги керування, до яких відносяться ланцюги тактування, скидання (обнуління), дозволу виводу або вводу.

По способу прийому (вводу) та видачі (виводу) двійкового слова регістри поділяють на регістри с послідовним, паралельним та послідовно-паралельним вводом (виводом) інформації. В регістрах з послідовним вводом (виводом) двійкове слово вводиться (виводиться) послідовно у часі розряд за розрядом. В регістрах з паралельним вводом (виводом) прийом (видача) слова відбувається по всім розрядам одночасно.

За напрямком зсуву послідовні регістри поділяють на односпрямовані регістри зі зсувом вправо, зсувом вліво та реверсивні регістри зсуву. Для останніх у залежності від керуючого сигналу та входу для вводу слова в послідовному коді зсув може здійснюватися в обох напрямках.

За кількістю ліній передачі змінних регістри поділяють на однофазні і парафазні, за способом синхронізації на однотактні, двотактні і багатотактні. В однофазних регістрах вивід двійкового слова відбувається без інверсії або з інверсією, тобто вони мають тільки прямі або інверсні виходи. Парафазні регістри мають як прямі, так й інверсні виходи, що забезпечує вивід слова як в прямій, так і в інверсній формі.

У сучасній цифровій схемотехніці регістри переважно будують на комбінованих DRS-тригерах з динамічним керуванням. Наявність у таких тригерах входів попередньої установки R і S дозволяє організовувати ланцюги обнуління, а в регістрах зсуву входи введення слова в паралельному коді. Багато регістрів мають виходи з трьома станами, що дає їм можливість без додаткових схем інтерфейсу безпосередньо працювати на магістральні шини.

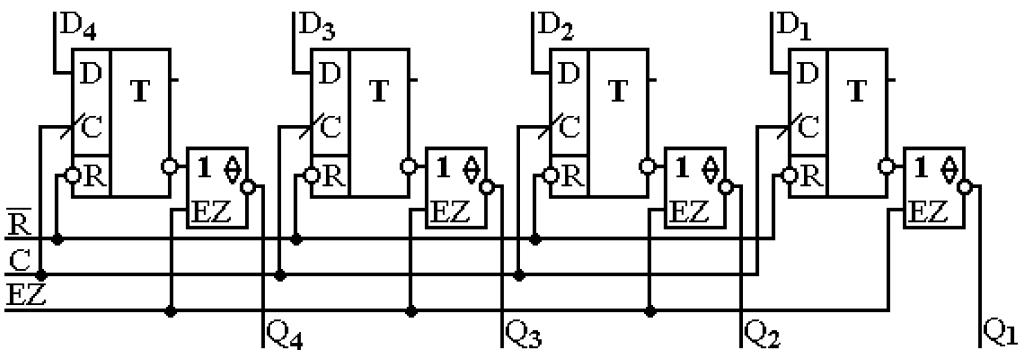

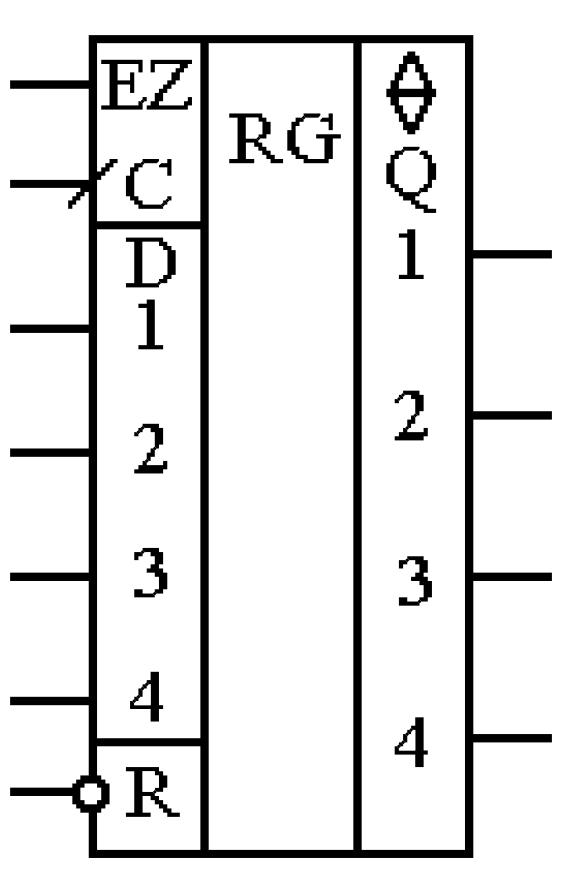

7.4.2. Паралельні (статичні) регістри. Паралельні регістри застосовують в комп’ютерній техніці, як швидкодіючі запам’ятовуючі пристрої, призначені для тимчасового зберігання багаторозрядних двійкових кодів даних і команд. Зокрема такими регістрами в процесорі комп’ютера є регістри загального призначення (РЗП), регістри команд, даних, регістри арифметично-логічного пристрою, призначені для тимчасового зберігання операндів і результатів операцій тощо. Паралельні регістри можуть виконувати тільки чотири перші мікрооперації з перерахованих вище. Їх побудову розглянемо на прикладі чотирьохрозрядного регістра з трьома станами виходу, схема якого показана на рис. 7.50, а умовне графічне зображення на рис. 7.51.

|

Рис. 7.50. Схема паралельного регістра з трьома станами виходу

|

Це регістр з паралельним вводом інформації. Входи DRS-тригерів на рис. 7.50 не показані, до них постійно прикладена напруга логічної одиниці U1, тому при = 1 ці тригери працюють у синхронному режимі (див. підрозділ 5.4.2). Слово, що надходить на входи D1 – D4 регістра в паралельному коді записується в D-тригери по перепаду сигналу на тактовому вході С від низького U0 до високого U1 рівня напруги . Воно зберігається в регістрі до часу поки не буде виконана чергова мікрооперація вводу, тобто по перепаду нове двійкове слово не буде занесено в регістр або не буде виконана мікрооперація його обнуління.

|

Рис. 7.51. Умовне графічне зображення паралельного регістра з трьома вихідними станами |

Третій стан виходів регістра і його керування забезпечується використанням інверторів з трьома вихідними станами, підключених до інверсних виходів DRS-тригерів. При наявності на вході EZ низького рівня напруги U0 інвертори працюють у звичайному логічному стані виходу, тому двійкове слово, що зберігається в регістрі передається на його виходи Q4 Q1, тобто при EZ=0 реалізується мікрооперація виводу слова. Тому на умовних зображеннях регістрів вхід EZ часто показують як інверсний і позначають OE (Output Enable – дозвіл виводу). При високому рівні напруги U1 на вході EZ (EZ = 1) виходи інверторів переходять у стан високого імпедансу двійкове слово з тригерів не виводиться на виходи регістра. Якщо ці виходи підключені до ліній шини даних комп’ютера, то при EZ = 1 вони просто відключаються від них. Тому паралельні регістри з трьома станами виходів дозволяють вирішити проблему, яка виникає в інтерфейсах „загальна шина”, коли багато пристроїв обмінюються двійковими словами через загальні лінії зв’язку. Цей обмін відбувається через вихідні паралельні буферні регістри таких пристроїв, які мають три вихідні стани. В будь-який заданий проміжок часу у звичайному логічному стані знаходяться виходи буферного регістру тільки того пристрою, який передає інформацію в шину, виходи регістрів інших пристроїв переводяться сигналом EZ = 1 у стан високого імпедансу.

За схемою, подібною тій, що наведена на рис. 7.50 реалізовано багато паралельних регістрів, які входять до складу серій ТТЛШ 1531, 1533 та КМОПТЛ 1564, 1554, 1594. На рис. 7.52 наведена мікросхема КР1594ИР23 (функціональний аналог MC74ACT374), яка є восьмирозрядним паралельним регістром з трьома станами виходів.

|

Рис. 7.52. Умовне графічне зображення мікросхеми КР1594ИР23 |

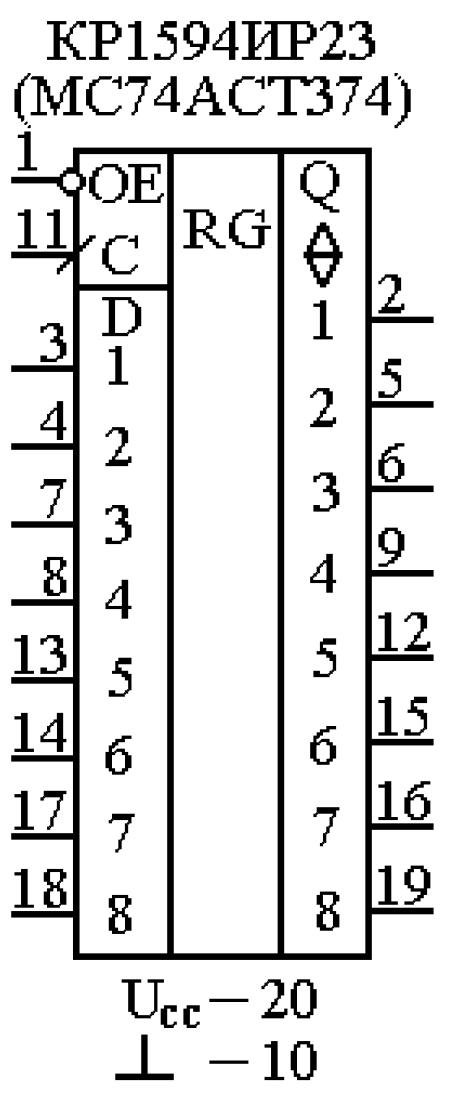

Для керування записом інформації в регістр на інформаційному вході кожного D-тригера включена комбінаційна схема, що складається з двох логічних елементів 2І і елемента 2АБО, які по суті утворюють два канали уведення інформації в D-тригер.

|

Рис. 7.53. Схема паралельного регістра з дозволом запису інформації

|

Інвертор

є загальним для всіх D-тригерів

регістра. Передача біта будь-якого

розряду двійкового слова Dn...D2D1

на інформаційний вхід відповідного

D-тригера

відбувається через канал, що містить

логічний елемент 2І, до іншого входу

якого підключено вихід інвертора. Виходи

D-тригерів

Q1,

Q2,

..., Qn,

з яких зчитується слово, що зберігається

в регістрі, зв’язані зворотним зв’язком

з інформаційними входами відповідних

D-тригерів

через канал, що містить логічний елемент

2І, один зі входів якого підключено до

входу регістра

![]() .

Дозвіл запису здійснюється сигналом

низького рівня напруги U0

на вході

(

= 0), який блокує передачу логічного

сигналу з виходів регістра Q1,

Q2

,..., Qn

на входи D-тригерів,

а його інверсне значення E

= 1 дозволяє передачу бітів двійкового

слова Dn...D2D1

на інформаційні входи D-тригерів.

Тому по перепаду сигналу

на

тактовому вході С двійкове слово Dn…D2D1

записується до D-тригерів

і з’являється на виходах регістра. Коли

= 1 (Е = 0) передача бітів слова зі входів

регістра на інформаційні входи D-тригерів

блокована і деблоковано зворотний

зв’язок між прямими виходами і входами

цих тригерів. Тому при надходженні

перепаду напруги

на вхід С, D-тригери

перезаписують той стан, в якому вони

знаходяться, тобто слово, що зберігається

в регістрі, не змінюється.

.

Дозвіл запису здійснюється сигналом

низького рівня напруги U0

на вході

(

= 0), який блокує передачу логічного

сигналу з виходів регістра Q1,

Q2

,..., Qn

на входи D-тригерів,

а його інверсне значення E

= 1 дозволяє передачу бітів двійкового

слова Dn...D2D1

на інформаційні входи D-тригерів.

Тому по перепаду сигналу

на

тактовому вході С двійкове слово Dn…D2D1

записується до D-тригерів

і з’являється на виходах регістра. Коли

= 1 (Е = 0) передача бітів слова зі входів

регістра на інформаційні входи D-тригерів

блокована і деблоковано зворотний

зв’язок між прямими виходами і входами

цих тригерів. Тому при надходженні

перепаду напруги

на вхід С, D-тригери

перезаписують той стан, в якому вони

знаходяться, тобто слово, що зберігається

в регістрі, не змінюється.

В табл. 7.9 наведені параметри деяких мікросхем паралельних регістрів.

Таблиця 7.9

Параметри інтегральних паралельних регістрів

Параметр |

Мікросхеми та їх функціональні аналоги |

||||

КР1533ИР27 (74ALS377) |

КР1531ИР22 (74АF373) |

КР1561ИР14 (HD74AC283) |

КР1594ИР23 (MC74ACT374) |

||

Розрядність |

8 |

8 |

4 |

8 |

|

z-стан виходів |

нема |

є |

є |

є |

|

Робочі температури, оС |

0 70 |

0 70 |

55 +125 |

40 +85 |

|

Uсс, В |

4,5 5,5 |

4,5 5,5 |

2 18 |

2 6 |

|

I1сп, (IccH), мА |

12 |

38 |

≤0,02 (15 В) |

≤0,08 (5,5 В) |

|

I0сп, (IccL), мА |

20 |

||||

U0вих, (UОL), В |

≤ 0,5 |

≤ 0,5 |

≤ 0,05 |

≤ 0,1 |

|

U1вих, (UОH), В |

2,4 |

2,4 |

Uсс 0,05 |

Uсс 0,2 |

|

I1вх (IIH), мкА |

20 |

5 |

0,1 |

0,1 |

|

I0вх (IОL), мА |

0,2 |

0,6 |

110-4 |

110-4 |

|

I0вих (IОL), мА |

≤ 30 |

≤ 60 |

≤ 8,8 (15 В) |

≤ 75 |

|

tPLH, нс |

СQn |

2,0 8,0 |

9,0 |

300 (5 В) 90 (15 В) |

8 (5 В) |

tPHL, нс |

3,0 11,0 |

5,2 |

7 (5 В) |

||

tPLH, нс |

DnQn |

|

5,3 |

|

|

tPHL, нс |

3,7 |

||||

tPZH, нс |

Час дозволу виводу |

|

5,0 |

200 (5 В) 60 (15 В) |

7 (5 В) |

tPZL, нс |

5,6 |

6,5 (5 В) |

|||

FMAX, Гц |

65 |

|

1,8 (5 В) 12 (15 В) |

60 (3,3 В) 100 (5 В) |

|

7.4.3. Регістри зсуву. Це послідовні регістри, наявність в яких зв’язків між інформаційними входами і виходами тригерів сусідніх розрядів дозволяє при надходженні тактового імпульсу перезаписувати стан тригера кожного розряду регістра в сусідній, тобто здійснювати зсув двійкового слова без зміни послідовності одиниць і нулів у ньому. За такт всі розряди слова, записаного в регістр зсуву можуть бути переміщені на один розряд або у бік старших розрядів (вліво), або у бік молодших розрядів (управо). Регістри, в яких зсув може відбуватися в обох напрямках називають реверсивними регістрами зсуву. На умовних графічних зображеннях інтегральних мікросхем регістрів напрямок зсуву позначають стрілками: зсув управо; зсув вліво; реверс. Регістри зсуву на відміну від статичних регістрів можуть виконувати всі п’ять мікрооперацій, перелічених вище. Мікрооперація зсуву дозволяє вводити і виводити багаторозрядні двійкові слова в таких регістрах у послідовному коді. Тому односпрямовані регістри зсуву мають вхід для послідовного у часі побітового уведення інформації зі зсувом вправо DSR (абревіатура від англійської назви Data Serial Right) або вхід DSL (абревіатура від Data Serial Left) для прийому даних зі зсувом вліво. Реверсивні регістри зсуву, звичайно, мають як вхід DSR, так й вхід DSL, які на умовних графічних зображеннях регістрів позначають також як DR і DL відповідно.

Завдяки наявності зв’язків між інформаційними входами і виходами сусідніх тригерів, що утворюють регістр зсуву, ці тригери одночасно приймають участь як в процесі прийому, так і в процесі передачі інформації. Поєднати ці процеси для тригерів зі статичним керуванням неможливо внаслідок явища гонок, тому в регістрах зсуву використовують виключно тригери з динамічним керуванням по фронту або по зрізу тактового імпульсу.

В комп’ютерній техніці регістри зсуву використовують в блоках арифметично-логічного пристрою процесора, призначених для виконання команд зсуву, арифметичних операцій множення та ділення, в модемах комп’ютерних мереж для перетворення послідовного двійкового коду в паралельний код і навпаки та для інших цілей.

Розглянемо схемотехнічну організацію і функціонування регістрів зсуву різного типа.

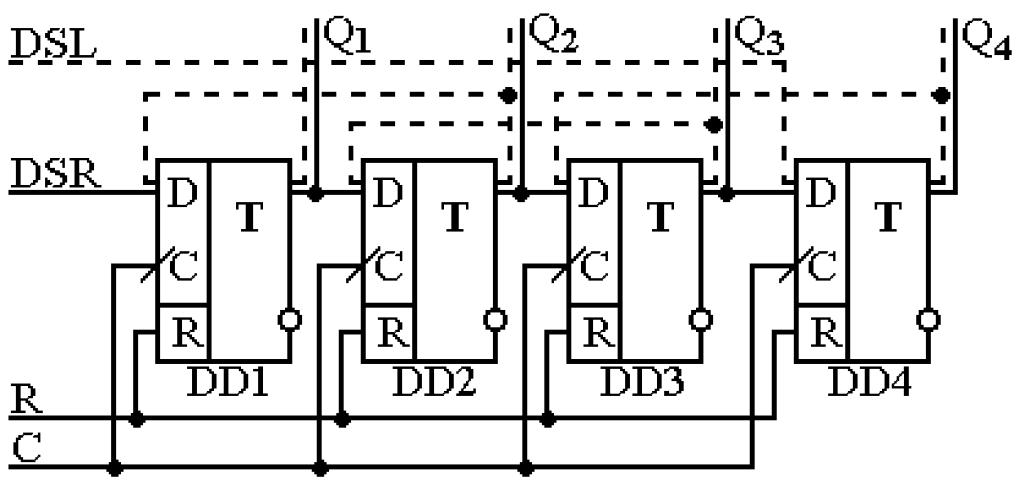

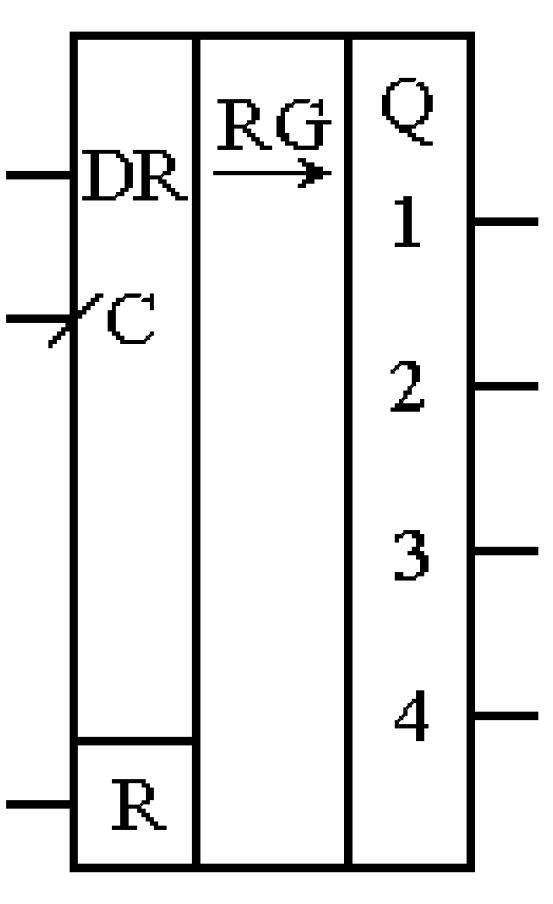

Односпрямовані регістри зсуву з послідовним уводом і паралельно-послідовним виводом реалізуються як послідовний ланцюг синхронних DRS або JKRS-тригерів з об’єднаними тактовими входами С і входами скидання R. Організацію таких регістрів ілюструє схема чотирьохрозрядного регістра зі зсувом управо, наведена на рис. 7.54а (показана суцільними лініями). Умовне зображення такого регістра показано на рис. 7.54б.

|

|

а |

б |

Рис. 7.54. Односпрямований регістр зсуву з послідовним уводом і паралельно-послідовним виводом: а – схема регістра зі зсувом управо (показана суцільними лініями) та зсувом вліво (зв’язки між інформаційними входами D і виходами тригерів показані пунктиром); б – умовне зображення регістра зі зсувом управо

|

|

Завдяки зв’язку в послідовному тригерному ланцюзі виходу і1-го тригера з D входом і-того тригера, при надходженні на його вхід синхронізації С перепаду логічного сигналу біт інформації, який зберігає і1 тригер записується у і-тий тригер, а оскільки тактовий сигнал надходить одночасно на входи синхронізації всіх тригерів регістра відбувається зсув двійкового слова, що зберігає регістр управо на один біт. Інформаційний вхід D першого тригера в ланцюзі тригерів (тригер DD1) є входом для послідовного введення двійкового слова в регістр зі зсувом вправо (на рис. 7.54а цей вхід позначений як DSR). Функціональна таблиця (рис. 7.55) ілюструє уведення в регістр слова A4A3A2A1, яке надходить на вхід DSR побітово в послідовному коді, починаючі з молодшого розряду A1.

Символ в таблиці означає будь-яке значення логічної змінної. Перший тактовий сигнал на вході С забезпечує введення молодшого біта A1 двійкового слова зі входу регістра DSR в тригер DD1, подальші тактові сигнали забезпечують послідовне у часі введення інших бітів слова зі зсувом у кожному такті інформації, що зберігається в регістрі, на один біт управо (від виходів регістра з меншими номерами до виходів з більшими номерами). Через чотири такта всі біти чотирьохрозрядного двійкового слова заносяться до тригерів регістру і воно може бути прочитано в паралельному коді з виходів Q1 – Q4. Таким чином, регістр зсуву виконав перетворення послідовного коду слова в паралельний код.

Номер

|

|||||||||||||||||||||||||||||||||||||||

Рис. 7.55. Функціональна таблиця односпрямованого регістра зсуву з послідовним уводом

|

|||||||||||||||||||||||||||||||||||||||

Зазначимо, що вивід слова можна здійснити також у послідовному коді. Двійкове слово, яке зберігається в односпрямованому регістрі зі зсувом управо (рис. 7.54а), можна прочитати з виходу Q4 в послідовному коді, починаючи з молодшого розряду, якщо подати послідовність з чотирьох тактових сигналів на вхід синхронізації С. Таким чином регістр зсуву (рис. 7.53а) є регістром з паралельно-послідовним виводом інформації. Обнуління регістра здійснюється сигналом високого рівня напруги U1 на вході R (R = 1), який одночасно надходить на входи скидання DRS-тригерів, що утворюють регістр. Мікрооперація зсуву здійснюється при R = 0 у синхронному режимі роботи DRS-тригерів сигналом . Сигнали , 0, 1 на вході С є пасивними, при яких регістр зберігає інформацію (рис. 7.55).

Схема односпрямованого регістра зі зсувом управо (рис. 7.54а) може бути перетворена на схему регістра зі зсувом вліво, якщо змінити зв’язки між інформаційними входами D і виходами сусідніх тригерів. Для цього слід розірвати такі зв’язки, показані суцільними лініями на рис. 7.54а, і організувати їх так, як показано пунктирними лініями. Тепер входом послідовного вводу DSL є D вхід тригера DD4, а послідовні зв’язки між тригерами забезпечують перезапис бітів двійкового слова у напрямку від тригера DD4 до тригера DD1, тобто зсув відбувається вліво (від виходів регістра з більшим номером до виходів з меншим номером).

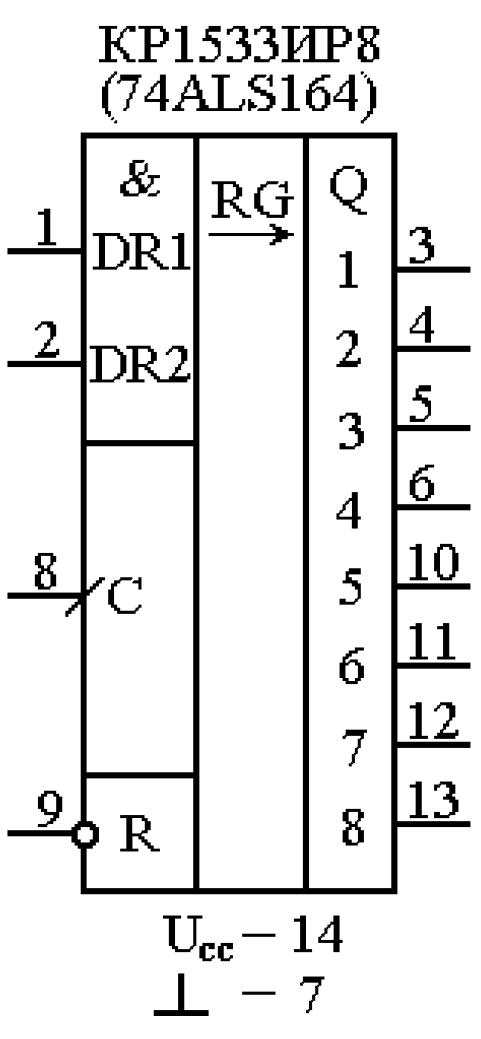

Регістри з послідовним уводом і паралельно-послі-довним виводом входять до складу багатьох серій ІМС. На рис. 7.56, як приклад, наведена мікросхема КР1533ИР8 во

|

Рис. 7.56. Умовне графічне зображення мікросхеми К1533ИР8 |

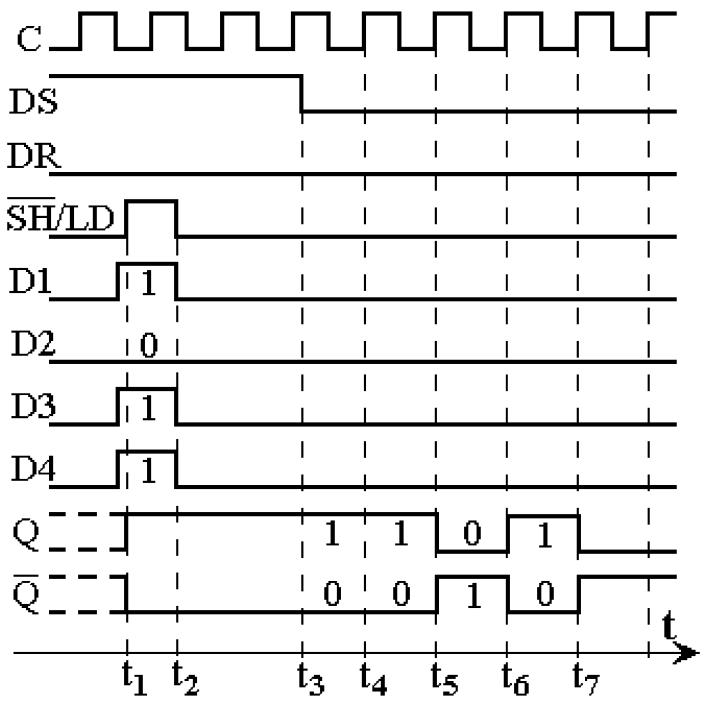

Для перетворення паралельного коду у послідовний потрібні регістри зсуву з паралельним уводом і послідовним виводом. Організацію односпрямованих регістрів зсуву з паралельно-послідовним уводом і послідовним виводом ілюструє схема наведена на рис. 7.57. Регістр має парафазні виходи Q і , з яких двійкове слово, що зберігає регістр, може одночасно виводитися як в прямому, так і в оберненому послідовному коді. Для введення слова в послідовному коді зі зсувом управо використовується вхід DR, а в паралельному коді – входи D1 – D4.

|

Рис. 7.57. Схема чотирьохрозрядного регістра зсуву з паралельно-послідовним уводом і послідовним виводом |

Способом

введення двійкового слова керують

сигнали на вході

![]() /LD.

При наявності на ньому високого рівня

напруги U1

(

/LD

= 1), який є пасивним для елемента ІНЕ,

дозволяється робота цих елементів

схеми, які формують на своїх виходах

логічні сигнали відповідно значенням

бітів двійкового слова на входах

паралельного вводу D1

– D4.

Оскільки виходи ІНЕ

підключені до входів попередньої

установки DRS-тригерів

і

,

які мають більш високий пріоритет ніж

входи D

і C

(див. підрозділ 5.4.2), поява на них активного

сигналу – логічного нуля переводе

DRS-тригери

в асинхронний режим роботи, тому вони

встановлюються відповідно сигналам,

що діють на входах D1

– D4.

Дійсно, нехай при

/LD

= 1 значення D1

= 1,

тоді на виході DD1

логічний нуль (

=0),

який надходить на вхід DD2,

що забезпечує

=1.

На входах попередньої установки

DRS-тригера

DD3

комбінація сигналів

= 0,

= 1, яка, згідно таблиці переходів (рис.

5.25), встановлює цей тригер у одиничний

стан. При D1

= 0 комбінація

= 1,

= 0 встановлює DD3

в нульовий стан. Таким чином при

/LD

= 1 DRS-тригери

регістра (рис. 7.57) на своїх виходах

повторюють відповідні біти двійкового

слова на входах D1

– D4,

тобто відбувається уведення слова в

регістр у паралельному коді.

/LD.

При наявності на ньому високого рівня

напруги U1

(

/LD

= 1), який є пасивним для елемента ІНЕ,

дозволяється робота цих елементів

схеми, які формують на своїх виходах

логічні сигнали відповідно значенням

бітів двійкового слова на входах

паралельного вводу D1

– D4.

Оскільки виходи ІНЕ

підключені до входів попередньої

установки DRS-тригерів

і

,

які мають більш високий пріоритет ніж

входи D

і C

(див. підрозділ 5.4.2), поява на них активного

сигналу – логічного нуля переводе

DRS-тригери

в асинхронний режим роботи, тому вони

встановлюються відповідно сигналам,

що діють на входах D1

– D4.

Дійсно, нехай при

/LD

= 1 значення D1

= 1,

тоді на виході DD1

логічний нуль (

=0),

який надходить на вхід DD2,

що забезпечує

=1.

На входах попередньої установки

DRS-тригера

DD3

комбінація сигналів

= 0,

= 1, яка, згідно таблиці переходів (рис.

5.25), встановлює цей тригер у одиничний

стан. При D1

= 0 комбінація

= 1,

= 0 встановлює DD3

в нульовий стан. Таким чином при

/LD

= 1 DRS-тригери

регістра (рис. 7.57) на своїх виходах

повторюють відповідні біти двійкового

слова на входах D1

– D4,

тобто відбувається уведення слова в

регістр у паралельному коді.

При /LD = 0 входи паралельного уводу D1 – D4 блоковані, оскільки незалежно від їх логічного стану на виходах всіх елементів ІНЕ схеми діє напруга логічної одиниці. На входах попередньої установки DRS-тригерів комбінація = 1, = 1, яка переводе ці тригери у синхронний режим роботи (рис. 5.25). Тому при надходженні сигналів на вхід С регістра відбувається уведення послідовного двійкового слова через вхід DR зі зсувом вправо. Це відбувається таким же чином, як в регістрі зсуву розглянутому раніше (рис. 7.54). Вхід DS схеми (рис. 7.57) призначений для керування подачею тактових сигналів на тригери регістра. Пасивний для логічного елемента АБО сигнал низького рівня напруги U0 на вході DS (DS = 0) дозволяє подачу тактових сигналів на тригери регістра, активний сигнал високого рівня U1 (DS = 1) – забороняє їх подачу. Тому при /LD = 0, DS = 1 регістр (рис. 7.57) знаходиться у стані зберігання інформації.

Регістри зсуву, які мають паралельно-послі-довний увід та послідовний вивід, використовують для перетворення паралельного коду двійкового слова в послідовний код. Таке перетворення, на прикладі двійкового коду 1011, ілюструють часові діаграми, наведені на рис. 7.58.

|

Рис. 7.58. Часові діаграми перетворення паралельного коду в послідовний код |

|

Рис. 7.59. Умовне графічне зображення мікросхеми КР1533ИР9 |

Прикладом односпрямованого регістру зсуву, який має схемотехнічну організацію подібну до наведеної на рис. 7.57, є мікросхема КР1533ИР9 (функціональний аналог SN74ALS165) (рис. 7.59). Мікросхема має вісім входів D для запису у регістр двійкового слова в паралельному коді і вхід DR для запису слова в послідовному коді. Зсув слова управо на один біт відбувається перепадом сигналу на вході С при наявності на вході DS низького рівня напруги U0 (DS = 0) і блокується сигналом високого рівня U1 (DS = 1). Запис слова у паралельному коді зі входів D відбувається сигналом низького рівня U0 на вході PL (PL = 0). Регістр зберігає інформацію, коли DS = 1, PL = 1.

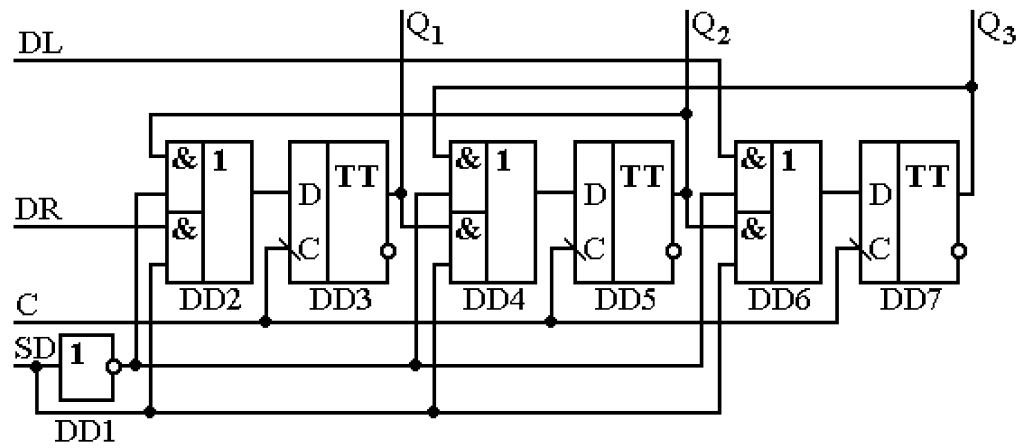

Реверсивні регістри зсуву можуть здійснювати зсув двійкового слова в обох напрямках, тому на їх умовних графічних зображеннях використовують позначення . Схеми реверсивних регістрів містять обидва типи зв’язків між інформаційними входами і виходами сусідніх тригерів, що забезпечують зсув слова управо і вліво (на рис. 7.54а такі зв’язки показані суцільними і пунктирними лініями). Управління зв’язками між тригерами здійснюють за допомогою комутаційних елементів, в якості яких можуть бути використані логічні елементи ІАБО чи ІАБОНЕ. Один з варіантів організації схеми реверсивного регістра зсуву з використанням логічних елементів ІАБО показано на рис. 7.60 на прикладі трьохрозрядного регістру.

|

Рис. 7.60. Схема реверсивного регістра зсуву

|

В схемі для керування напрямком зсуву використовується вхід SD. При високому рівні напруги на ньому SD = 1, логічний нуль, що надходить з виходу інвертора DD1 на верхні секції І логічних елементів DD2, DD4, DD6, блокує перезапис інформації з виходів тригерів з більшими номерами в тригери з меншими номерами, тобто забороняє зсув двійкового слова вліво. Одночасно сигнал SD = 1 дозволяє функціонування зв’язків між тригерами, що забезпечують передачу інформації з послідовного входу DR зі зсувом управо. У випадку SD = 0, навпаки, блоковані зв’язки між тригерами через нижні секції елементів ІАБО, що забезпечують зсув вправо, і логічною одиницею з виходу DD1 дозволені зв’язки, які забезпечують зсув вліво. Таким чином, в схемі регістра зсуву, що наведена на рис. 7.60, сигнал високого рівня напруги U1 на вході SD забезпечує зсув двійкового слова в розрядній сітці управо, а сигнал низького рівня напруги U0 уліво.

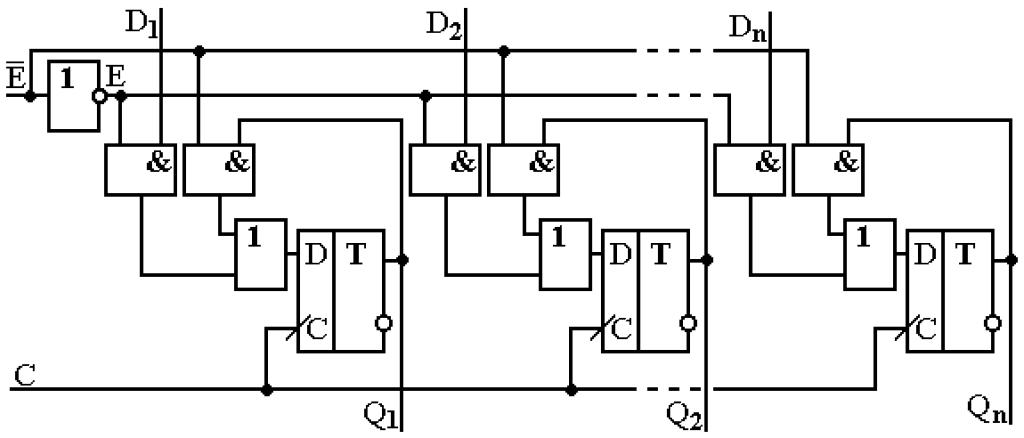

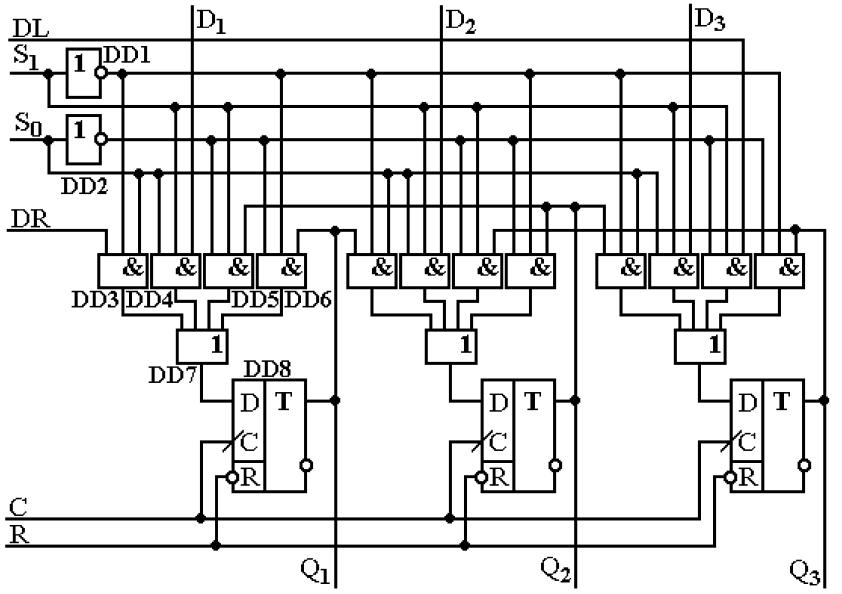

Реверсивні регістри зсуву з паралельно-послідовним вводом і паралельно послідовним виводом двійкового слова називають універсальними. Такі регістри можуть виконувати всі мікрооперації, притаманні таким цифровим вузлам. Типова схема універсального регістра, на прикладі трьох розрядів, показана на рис. 7.61.

|

Рис. 7.61. Схема універсального регістра

|

Характерною особливістю цієї схеми є те, що вона складається з блоків, які повторюються в кожному розряді регістра. До складу блоку входить DRS-тригер (вхід для таких тригерів на схемі не показано), чотири логічних елемента 3І та один елемент 4АБО. По суті сукупність цих логічних елементів утворює елемент 3І4АБО, за допомогою якого відбувається керування мікроопераціями, що виконує регістр. Інвертори DD1, DD2 є загальними для всіх розрядів регістра, на їх входи подаються керуючи логічні сигнали S1, S0, які визначають тип мікрооперації регістра. Вхід DL призначено для вводу послідовного коду слова зі зсувом вліво, вхід DR – для його вводу зі зсувом управо. Через входи D1 – D3 здійснюється паралельне уведення двійкового слова. Всі операції уведення інформації відбуваються сигналом на вході С регістра, для чого в його схемі використані D-тригери з прямим динамічним керуванням. Мікрооперація обнуління реалізується сигналом низького рівня напруги U0 на вході R.

Функціональна таблиця універсального регістра (рис. 7.61), наведена на рис. 7.62. В ній значення логічних змінних на виходах регістра Q1, Q2, Q3 у стані зберігання позначено як q1, q2, q3, а символ означає будь-яке значення.

Мікрооперація

Входи

Виходи

R

C

Номер такта

S1

S0

DR

DL

D1

D2

D3

Q1

Q2

Q3

Обнуління

0

0

0

0

Зберігання

1

0

0

q1

q2

q3

Зсув управо

1

1

0

1

A1

A1

q2

q3

1

2

0

1

A2

A2

A1

q3

1

3

0

1

A3

A3

A2

A1

Зсув вліво

1

1

1

0

A3

q2

q3

A3

1

2

1

0

A2

q3

A3

A2

1

3

1

0

A1

A3

A2

A1

Паралельний увід

1

1

1

1

A3

A2

A1

A3

A2

A1 |

|||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

Рис. 7.62. Функціональна таблиця універсального регістра

|

|||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

Розглянемо роботу універсального регістра з урахуванням функціональної таблиці (рис. 7.62). Насамперед зазначимо, що на виконання конкретної мікрооперації схема регістра (рис. 7.61) налаштовується за допомогою чотирьох логічних елементів 3І, що розташовані у кожному її розряді.

Елемент DD3 та еквівалентні йому за призначенням елементи 3І розташовані в тих же позиціях інших розрядів схеми регістра відповідають за зсув управо. Як видно (рис. 7.61), саме через ці елементи і елементи 4АБО заведені зв’язки між входом DR, входами D і виходами тригерів, що забезпечують зсув управо (від виходів регістра з меншими номерами до виходів з більшими номерами). Коли на входах керування логічні сигнали S1 = 0, S0 = 1 з виходу DD1 і входу S0 поступають логічні одиниці, які дозволяють зв’язки між тригерами для зсуву управо. Одночасно, хоча б на одному зі входів елементів 3І DD4, DD5, DD6 та еквівалентних їм елементів інших розрядів з’являється логічний нуль, що блокує мікрооперації пов’язані з цими елементами. Тому по перепадам тактових сигналів на вході С регістра двійкове слово A3A2A1, яке надходить у послідовному коді на вхід DR, починаючи з молодшого розряду, уводиться до регістру зі зсувом управо (рис. 7.62). Через три такти це слово може бути виведено в паралельному коді.

Елемент DD5 та еквівалентні йому за призначенням елементи 3І інших розрядів регістра відповідають за зсув вліво. Через ці елементи і елементи 4АБО створені зв’язки від входу DL до виходу Q1 регістра. Зсув вліво дозволяють значення керуючих сигналів S1 = 1, S0 = 0, при яких на входах елемента DD5 і еквівалентних йому за призначенням елементів 3І, підключених до входу регістра S1 і виходу інвертора DD2, забезпечується логічна одиниця. На входах інших елементів 3І при S1 = 1, S0 = 0 є хоча б один логічний нуль, який блокує інші мікрооперації регістра. Зсув двійкового слова вліво відбувається таким же чином, як зсув управо, описаний вище (рис. 7.62).

За мікрооперацію вводу слова в паралельному коді відповідають логічні елементи 3І (елемент DD4 та інші), входи яких з’єднані зі входами регістра D1 – D3, призначеними для паралельного вводу інформації. Два інші входи цих елементів з’єднані безпосередньо зі входами керування S1, S0 (рис. 7.61). Тому при S1 = 1, S0 = 1 біти двійкового слова зі входів D1 – D3 передаються через ці елементи 3І та елементи 4АБО на інформаційні входи D тригерів і перепадом сигналу на вході С записуються до регістра.

Елемент DD6 та інші подібні елементи 3І, два входи яких підключені до виходів інверторів DD1, DD2, відповідають за мікрооперацію зберігання. При S1 = 0, S0 = 0 з інверторів на два входи кожного з цих елементів надходять логічні одиниці, що дозволяють через третій їх вхід зворотний зв’язок між виходом і входом D кожного тригера (рис. 7.61). Всі інші зв’язки, описані вище, блокуються нулем на входах відповідних елементів 3І. Тому по перепаду тактового сигналу тригер просто перезаписує інформацію, яку він зберігає, тому двійкове слово, що зберігається в регістрі не змінюється.

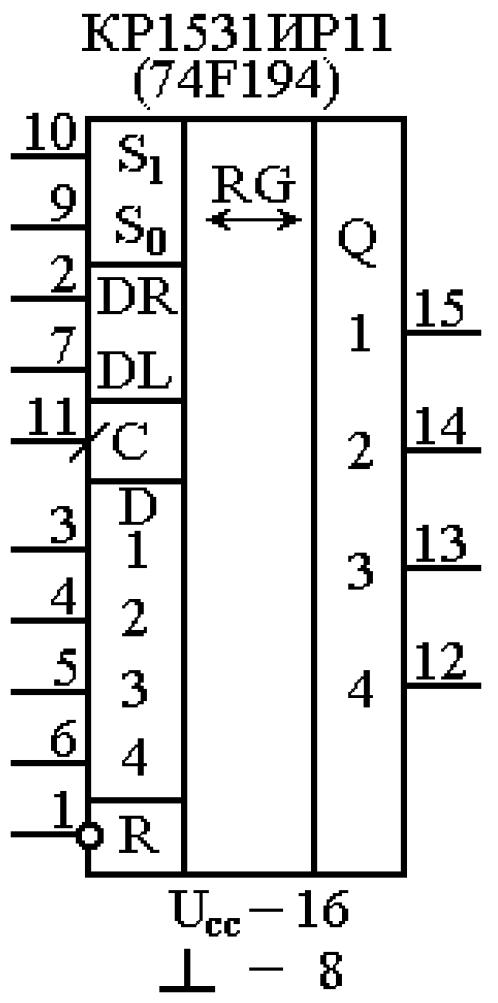

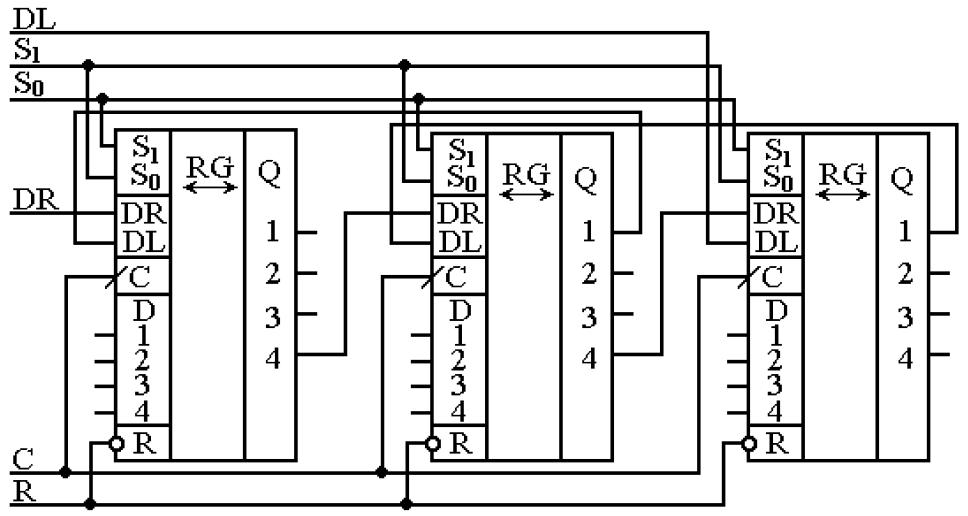

Прикладом універсального чотирьохрозрядного регістра, реалізованого за схемою наведеною на рис. 7.61, є мікросхема КР1531ИР11 (функціональний аналог 74F194), умовне зображення якої і нумерація виводів показані на рис. 7.63.

|

Рис. 7.63. Умовне графічне зображення мікросхеми КР1531ИР11 |

|

Рис. 7.64. Нарощування розрядності універсальних регістрів

|

Різні типи регістрів зсуву входять до багатьох серій мікросхем. В табл. 7.10 наведена інформація про інтегральні регістри зсуву серій ТТЛШ і КМОПТЛ, а в табл. 7.11 представлені параметри деяких таких мікросхем.

Таблиця 7.10

Мікросхеми регістрів зсуву ТТЛШ та КМОПТЛ

Мікросхема (аналог) |

Тип логіки |

Тип регістра |

Кількість розрядів |

Напрямок зсуву |

z-стан виходів |

КР1533ИР8 (SN74ALS164N) |

ТТЛШ |

З послідов-ним уводом і паралельно-послідов-ним виводом |

8 |

управо |

нема |

1531ИР8 (74F164) |

ТТЛШ |

8 |

|||

1533ИР31 (без аналога) |

ТТЛШ |

24 |

|||

74HC4015 |

КМОПТЛ |

4 |

|||

КР1564ИР8 (MM74HC164) |

КМОПТЛ |

8 |

|||

КР1554ИР8 (HD74ACT164) |

КМОПТЛ |

8 |

|||

КР1533ИР9 (SN74ALS165N) |

ТТЛШ |

З паралельно-послідов-ним уводом і послідов-ним парафазним виводом |

8 |

управо |

нема |

КР1564ИР9 (MM74AHC165) |

КМОПТЛ |

||||

КР1533ИР10 (SN74ALS166N) |

ТТЛШ |

З паралельно-послідов-ним уводом і послідовним виводом |

8 |

управо |

нема |

КР1554ИР10 (HD74ACT166) |

КМОПТЛ |

||||

КР1554ИР51 (CD4035BC) |

КМОПТЛ |

З паралельно-послідов-ним уводом та парафазним паралельним виводом |

4 |

управо |

нема |

КР1533ИР24 (SN74ALS299N) |

ТТЛШ |

Універсаль-ний

|

8 |

ревер-сивний |

є |

КР1533ИР29 (SN74ALS323) |

ТТЛШ |

||||

КР1531ИР11 (74F194) |

ТТЛШ |

4 |

ревер-сивний |

нема |

|

КФ1561ИР6 (MC14034B) |

КМОПТЛ |

8 |

ревер-сивний |

нема |

|

1564ИР11 (MM54HC194) |

КМОПТЛ |

4 |

ревер-сивний |

нема |

|

КР1554ИР24 (IN74AC299) |

КМОПТЛ |

8 |

ревер-сивний |

є |

|

КР1594ИР29 (MC74ACT323) |

КМОПТЛ |

Таблиця 7.11

Параметри деяких мікросхем регістрів зсуву

Параметр |

Мікросхема |

||||

КР1533ИР8 |

КР1531ИР11 |

КФ1561ИР6 |

КР1594ИР29 |

||

Робочі температури, оС |

0÷70 |

0÷70 |

65÷+150 |

65÷+150 |

|

Uсс, В |

4,5÷5,5 |

4,5÷5,5 |

2÷ 18 |

2÷6 |

|

Iсп, (Icc), мА |

10 |

33 |

≤0,03(15 В) |

≤0,08 (5,5 В) |

|

U0вих, (UОL), В |

≤ 0,5 |

≤ 0,5 |

≤ 0,05 |

≤ 0,1 |

|

U1вих, (UОH), В |

2,4 |

2,5 |

Uсс 0,05 |

Uсс 0,2 |

|

I1вх (IIH), мкА |

20 |

5 |

≤ 0,1 мкА |

0,1 |

|

I0вх (IIL), мА |

0,1 |

0,6 |

110-4 |

||

I0вих (IОL), мА |

30 |

≤ 60 |

≤ 8,8 (15 В) |

≤ 75 |

|

tPLH, нс |

СQn |

5,0÷13,0 |

5,2 |

525 (5 В) 145 (15 В) |

9,0 (5 В) |

tPHL, нс |

6,0÷15,0 |

5,5 |

9,0 (5 В) |

||

tPLH, нс |

RQn |

8,0 18,0 |

8,6 |

|

|

tPHL, нс |

|||||

tPZH, нс |

Час дозволу виводу |

|

|

505 (U5 В) 130(15 В) |

7,5 (5 В) |

tPZL, нс |

7,5 (5 В) |

||||

FMAX, МГц |

50 |

150 |

2,5 (5 В) 8,0 (U15 В) |

125 (5 В) |

|

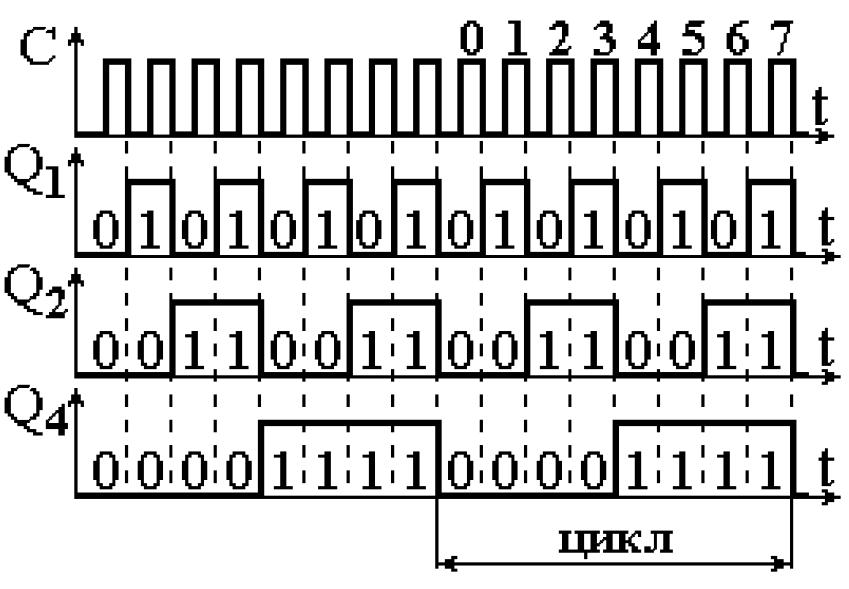

7.4.4. Загальна характеристика і класифікація лічильників. Лічильник – це послідовнісний цифровий вузол, призначений для перетворення кількості імпульсів, що надійшли на його вхід, у певний код. Лічильники, як і регістри зсуву, будують на основі зв’язаних між собою розрядних каскадів. У загальному випадку схема такого каскаду складається з тригера і комбінаційного вузла, призначеного для формування сигналів керування тригером.

Лічильники можуть виконувати наступні мікрооперації над двійковими словами (кодовими комбінаціями):

Обнуління або очистка, тобто установка всіх тригерів лічильника в нульовий стан;

Запис слова в паралельному коді;

Зберігання двійкового слова;

Видача (вивід) слова в паралельному коді;

Збільшення двійкового слова, що зберігається в лічильнику на одиницю (інкрементація);

Зменшення двійкового слова, що зберігається в лічильнику на одиницю (декрементація).

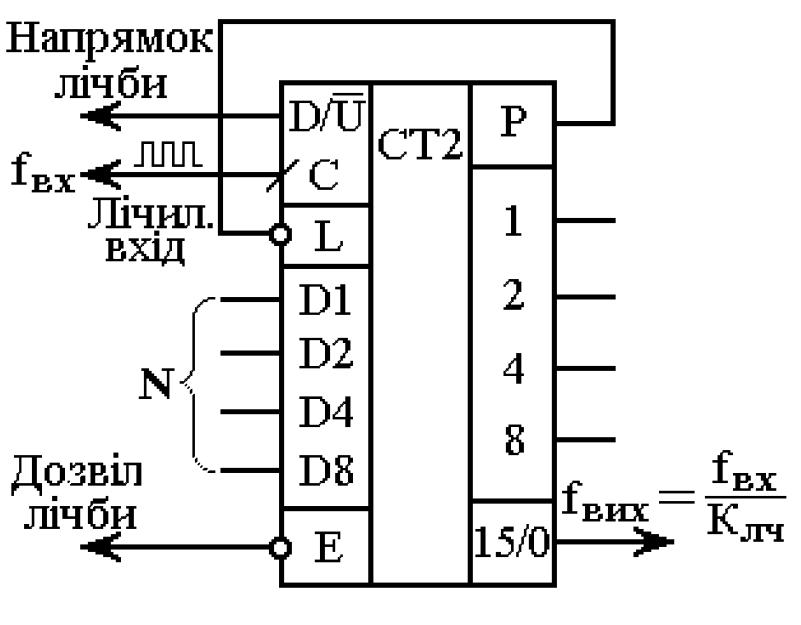

Будь-яке значення двійкового слова (кодова комбінація), яке лічильник формує в процесі роботи, називається станом лічильника. Характерним для лічильників є циклічний режим роботи. Це означає, що починаючі свою роботу з початкового стану, що визначається деяким значенням двійкового слова, лічильник після надходження на його вхід певної кількості імпульсів досягає граничного значення двійкового слова, після чого скидається у початковий стан і починає новий цикл роботи. Граничне значення двійкового слова, після якого лічильник повертається у початковий стан, називається станом переповнення лічильника. Кількість станів, що приймає лічильник за один цикл роботи називається коефіцієнтом (модулем) лічби.

Лічильники можуть працювати у трьох режимах: керування, накопичення і ділення. У режимі керування інформація зчитується з виходів лічильника після кожного лічильного імпульсу. В такому режимі лічильник працює, наприклад, коли він використовується, як програмний лічильник процесора, що зберігає адреси команд. У режимі накопичення лічильник підраховує число імпульсів, що надійшли на його вхід на заданому відрізку часу. Оскільки число таких імпульсів лічильник подає на виходах у певному двійковому коді, в цьому режимі його можна використовувати, як генератор коду (кодових комбінацій). Властивість лічильників зменшувати частоту сигналу на своїх виходах відносно вхідної частоти використовується у режимі ділення. В такому режимі працюють дільники частоти на основі лічильників, які використовуються в пристроях синхронізації та управління комп’ютера.

Лічильники класифікують по типу коду, напрямку лічби, типу логічних зв’язків між тригерами та по модулю лічби.

По типу коду лічильники поділяють на кільцеві, двійкові та десяткові. Кільцеві лічильники перетворюють число імпульсів, що надійшли на їх вхід в унітарний код, двійкові лічильники – в двійковий код, а десяткові – в двійково-кодований десятковий код.

По напрямку лічби лічильники поділяють на підсумовуючі (прямої лічби) і віднімальні (зворотної лічби). У підсумовуючих лічильниках вихідний код збільшується на одиницю з кожним лічильним імпульсом, у віднімальних – зменшується.

По типу логічних зв’язків між тригерами лічильники поділяють на лічильники з послідовним, паралельним, крізним та груповим переносом.

В лічильниках з послідовним переносом сигнал, що перемикає розрядні тригери передається через послідовне коло таких тригерів, в якому кожний тригер формує сигнал перемикання для сусіднього тригера. Тому лічильний імпульс, що надходить на вхід першого тригера кола викликає послідовне у часі перемикання тригерів лічильника.

В лічильниках з паралельним переносом лічильний імпульс надходить одночасно на тригери всіх розрядів, що викликає їх одночасне перемикання.

В лічильниках з крізним переносом для передачі сигналу, що перемикає розрядні тригери, використовуються послідовні ланцюги логічних елементів, звичайно, кон’юнкторів або диз’юнкторів. Тому тригери таких лічильників, як і лічильників з послідовним переносом, перемикаються послідовно у часі, але швидкодія збільшується за рахунок менших затримок сигналу в послідовному колі логічних елементів порівняно з подібним колом тригерів.

В лічильниках з груповим переносом тригери об’єднуються у групи, в межах яких та між самими групами використовуються різні типи переносу лічильного сигналу згадані вище.

За модулем лічби лічильники поділяють на лічильники зі сталим, довільним і програмованим модулем. У лічильниках зі сталим модулем коефіцієнт лічби визначається насамперед кодом, що використовує лічильник і розрядністю лічильника. Лічильники з довільним модулем реалізують на основі лічильників зі сталим модулем, який змінюють шляхом виключення того чи іншого числа станів лічильника. Таке виключення реалізують шляхом створення зворотних зв’язків між виходами лічильника і входом скидання або за рахунок певних зв’язків між розрядними тригерами. У лічильниках з програмованим модулем виключення станів лічильника і тим самим зміна його коефіцієнта лічби здійснюється за допомогою двійкового коду, що уводиться зі входів паралельного вводу лічильника.

До основних експлуатаційних показників лічильників відносять ємність і швидкодію. Ємність визначає коефіцієнт лічби Клч, який характеризує число імпульсів доступних ліченню за один цикл роботи лічильника.

Швидкодію визначають два параметра: роздільна здатність tроз.лч і час установлення коду tуст лічильника.

Роздільна здатність це мінімальний час між вхідними сигналами, при якому ще забезпечується безперебійна робота лічильника. Цей параметр безпосередньо пов’язаний з розділяючим часом тригерів tроз (див. підрозділ 5.2), на яких побудовано лічильник. Зворотна величина роздільної здатності визначає максимальну частоту лічби fmax:

fmax = 1/tроз.лч. (7.56)

Час установлення коду tуст це максимально можливий інтервал часу між моментом надходження вхідного сигналу і моментом переходу лічильника в новий стійкий стан. Параметри швидкодії лічильників залежать від часових параметрів тригерів і способу їх з’єднання між собою.

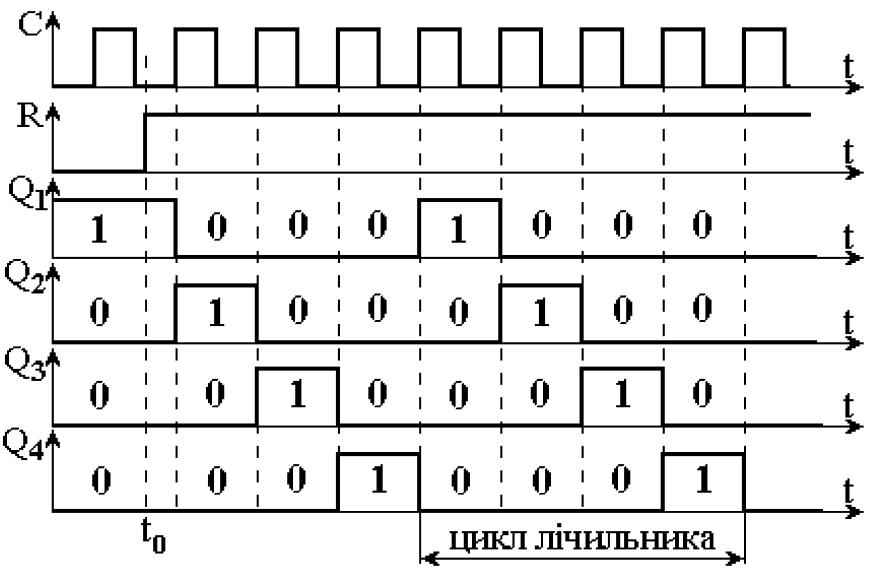

7.4.5. Кільцеві лічильники. Кільцеві лічильники перетворюють кількість імпульсів, що надходять на їх вхід в унітарний код, тобто код що містить одиницю тільки в одному розряді, в інших – нулі. Нульовому стану кільцевого лічильника відповідає унітарний код з одиницею у молодшому розряді. Для побудови таких лічильників використовують регістри зсуву.

Найпростіший кільцевий лічильник – це регістр зсуву, замкнений у кільце, тобто включений таким чином, що вихід тригера його останньої ступені підключений до інформаційного входу тригера першої ступені. Схема кільцевого лічильника, реалізованого на односпрямованому регістрі зі зсувом управо, показана на рис. 7.65а.

|

а |

|

б |

Рис. 7.65. Схема кільцевого лічильника (а) і часові діаграми сигналів на його входах і виходах (б) |

Сукупність значень бітів Q4Q3Q2Q1, що зберігають розрядні тригери лічильника, утворює унітарний двійковий код. Обнуління лічильника відбувається сигналом низького рівня напруги U0 на вході скидання лічильника R (R = 0). Цей сигнал надходить на входи попередньої установки комбінованих DRS-тригерів і встановлює їх згідно таблиці справжності на рис. 5.25 (на вільному вході попередньої установки кожного DRS-тригера діє сигнал високого рівня U1, ланцюги, що створюють такий сигнал на рис. 7.65а не показані). Отже початковий стан кільцевого лічильника, реалізованого за схемою, наведеною на рис. 7.65а, визначає унітарний код 0001.

Сигнал високо рівня напруги U1 на вході R дозволяє лічбу. Тому DRS-тригери переходять у синхронний режим роботи і по кожному перепаду тактового сигналу записують логічну змінну, що діє на їх інформаційному вході D. Як наслідок двійкове слово зсувається у кожному такті на один біт управо (рис. 7.65б). Завдяки зв’язку між виходом Q4 тригера DD4 та D входом тригера DD1 значення біту, що поступає з DD4 переноситься в тригер DD1. На виходах лічильника формується послідовність станів 0001, 0010, 0100, 1000 (рис. 7.65б). Через чотири такти лічильник досягає стану переповнення 1000, тому в наступному такті логічна одиниця з тригера DD4 перезаписується у тригер DD1 і починається новий цикл роботи лічильника.

Таким чином, для лічильника, схема якого наведена на рис. 7.65а, коефіцієнт лічби дорівнює Клч = 4. У загальному випадку n-розрядного кільцевого лічильника коефіцієнт лічби визначає співвідношення:

Клч = n, (7.57)

де n – кількість розрядів (тригерів) лічильника.

Оскільки лічильний сигнал С (рис. 7.65б) надходить одночасно на всі тригери (рис. 7.65а), то час установлення коду кільцевого лічильника tуст визначає час затримки перемикання тригера tз.пер, а роздільну здатність tроз.лч – розділяючий час тригера tроз, тобто tуст = tз.пер, tроз.лч = tроз. З урахуванням цього максимальна частота лічби кільцевого лічильника фактично визначається максимальною частотою перемикання тригерів, тобто fmax = 1/tроз.

З часових діаграм, наведених на рис. 7.65б, випливає, що на кожному виході кільцевого лічильника частота сигналу в чотири рази менша за частоту лічильного сигналу на вході С. Таким чином, кільцевий лічильник виконує функцію дільника частоти, який у загальному випадку має коефіцієнт ділення частоти Кділ = 1/Клч = 1/n.

Недоліком кільцевих лічильників є досить висока ймовірність збоїв, обумовлених перешкодами. Збої виявляються як зникнення одиниці в унітарному коді або як поява зайвих одиниць. Для боротьби зі збоями кільцевих лічильників використовують ланцюги корекції їх стану. Такі ланцюги можуть бути створені на базі логічних елементів АБОНЕ. Схема чотирьохрозрядного кільцевого лічильника з ланцюгом корекції стану показана на рис. 7.66а. В цій схемі функцію корекції виконує логічний елемент DD2, входи якого підключені до виходів регістру зсуву DD1, а вихід до входу послідовного уводу DR. Принцип роботи кільцевого лічильника з ланцюгом корекції ілюструє функціональна таблиця наведена на рис. 7.66б.

|

|

||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

а |

б |

||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

Рис. 7.66. Схема кільцевого лічильника з ланцюгом корекції (а) і його функціональна таблиця (б)

|

|||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

Сигнал високого рівня напруги U1 на вході R регістра зсуву (R = 1), незалежно від сигналів на інших його входах, викликає обнуління і тим самим забороняє роботу кільцевого лічильника, який встановлюється в неробочий стан 0000. В цьому стані на виході елемента 3АБОНЕ DD2 логічна одиниця, яка поступає на вхід DR регістра DD1. Коли сигнал низького рівня R = 0 дозволяє роботу лічильника, ця одиниця по перепаду першого тактового імпульсу записується до регістра, тобто встановлюється його початковий стан 0001, з якого починається лічба (рис. 7.66б, номер такта 1). Логічна одиниця на будь-якому вході DD2 забезпечує на його виході логічний нуль, який при надходженні наступних тактових імпульсів вводиться в регістр через вхід DR. Тому подальші лічильні сигнали , за рахунок введення нулів зі входу DR і зсуву слова в бік виходів регістра з більшими номерами, в кожному такті збільшують унітарний код на одиницю аж до значення 1000 (Q4 = 1), яке відповідає стану переповнення лічильника. В цьому стані на всіх входах DD2 сигнал логічного нуля, а на виході логічної одиниці. Тому наступний лічильний імпульс (рис. 7.66б, такт номер 5) вводить одиницю зі входу DR і виводить її з виходу Q4 за межі розрядної сітки регістра. В лічильнику знову реалізується стан 0001, з якого починається новий цикл лічби.

Якщо через дію перешкоди зникає одиниця унітарного коду (рис. 7.66б, такт номер 6), то на виході логічного елемента DD2 одразу з’являється одиниця, яка наступним лічильним імпульсом записується до регістру, тобто відбувається відновлення унітарного коду кільцевого лічильника з початкового стану 0001 (рис. 7.66б, такт номер 7).

У випадку, коли перешкода приводить до появи зайвих одиниць у вихідному коді кільцевого лічильника (рис. 7.66б, такт номер 9), за рахунок зсуву, ці одиниці через декілька тактів виводяться за межі розрядної сітки регістра і унітарний код відновлюється (рис. 7.66б, такт номер 12).

Позитивною якістю кільцевих лічильників є висока швидкодія, і безпосереднє, без використання дешифраторів, перетворення кількості лічильних імпульсів в унітарний код. Вадою є потреба великої кількості тригерів для забезпечення великих значень коефіцієнта лічби Клч. Так, наприклад, для реалізації кільцевого лічильника з Клч = 256 потрібно 256 тригерів, тоді як для реалізації двійкового лічильника з таким же Клч всього вісім тригерів. Зменшити вдвічі кількість тригерів кільцевого лічильника можливо, якщо реалізувати його як лічильник Джонсона.

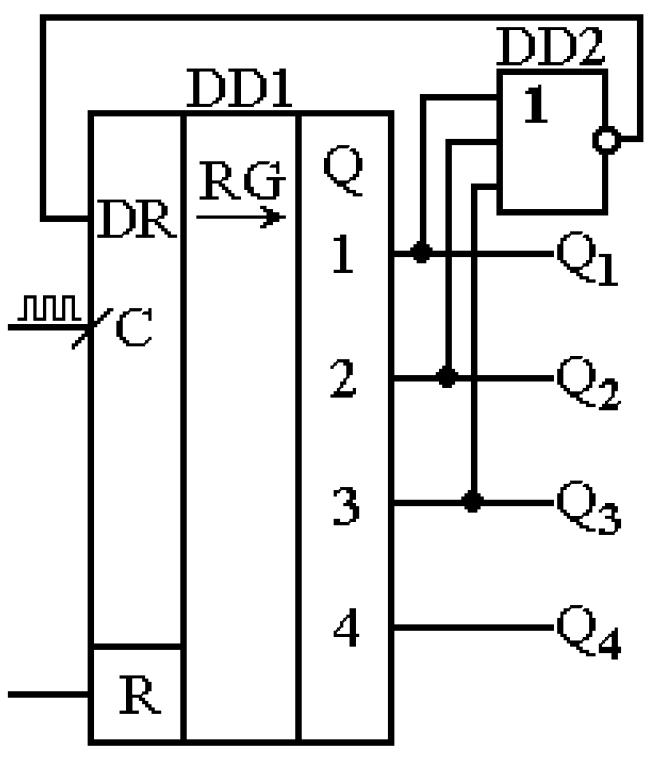

Лічильник Джонсона це різновид кільцевого лічильника, в якому один зв’язок між виходами і інформаційними входами сусідніх розрядних тригерів зроблений перехресним, тобто інформаційний вхід підключено не до прямого виходу сусіднього тригера, а до інверсного. Схема лічильника Джонсона показана на рис. 7.67.

В схемі перехресним є зв’язок між інверсним виходом тригера DD3 і входом D тригера DD1. Функціональна таблиця лічильника Джонсона, що пояснює його роботу, показана на рис. 7.68.

|

Рис. 7.67. Схема шестирозрядного лічильника Джонсона

|

У початковому стані лічильника при R = 0, не залежно від наявності тактового сигналу на вході С, всі D-тригери зберігають нульовий стан. Робота лічильника дозволяється сигналом високого рівня напруги U1 (R = 1).

R

|

||||||||||||||||||||||||||||||||||||||||||||||||||||||||

Рис. 7.68. Функціональна таблиця лічильника Джонсона

|

По

перепаду першого тактового імпульсу

одиниця з інверсного виходу

![]() тригера DD3

записується у DD1

і по ланцюгу тригерів від виходу Q1

до виходу Q3

починає розповсюджуватися хвиля одиниць.

Через три тактових імпульси всі тригери

заповнюються одиницями (рис. 7.68, номер

імпульсу 3) і на інверсному виході тригера

DD3

з’являється логічний нуль. Наступний

імпульс вводить цей нуль в тригер DD1

і по ланцюгу тригерів розповсюджується

хвиля нулів. По перепаду

шостого імпульсу лічильник Джонсона

повертається у початковий стан Q3Q2Q1

= 000.

тригера DD3

записується у DD1

і по ланцюгу тригерів від виходу Q1

до виходу Q3

починає розповсюджуватися хвиля одиниць.

Через три тактових імпульси всі тригери

заповнюються одиницями (рис. 7.68, номер

імпульсу 3) і на інверсному виході тригера

DD3

з’являється логічний нуль. Наступний

імпульс вводить цей нуль в тригер DD1

і по ланцюгу тригерів розповсюджується

хвиля нулів. По перепаду

шостого імпульсу лічильник Джонсона

повертається у початковий стан Q3Q2Q1

= 000.

Таким чином, з функціональної таблиці (рис. 7.68) випливає, що робочий цикл лічильника Джонсона, реалізованого за схемою на рис. 7.67, має шість станів, тобто Клч = 6. У загальному випадку, коли такий лічильник побудовано на n тригерах, коефіцієнт лічби дорівнює:

Клч = 2n. (7.58)

На відміну від кільцевого лічильника, який безпосередньо формує на виходах розрядних тригерів унітарний код, код вихідних станів Q3Q2Q1 лічильника Джонсона потребує перетворення в унітарний код. Це можна зробити за допомогою дешифратора, побудованого на логічних елементах 2І. Як видно з функціональної таблиці (рис. 7.68) комбінації коду Q3Q2Q1 відрізняються парними позиціями (в таблиці ці позиції підкреслені). Такі парні позиції є індивідуальними для кожного значення кодового слова Q3Q2Q1. З урахуванням цих парних позицій можна для кожного стану лічильника Джонсона за допомогою елемента 2І сформувати логічну одиницю унітарного коду. Спосіб дешифрації парних позицій кодового слова Q3Q2Q1 для кожного стану y0, y1,…, y5 лічильника Джонсона наведено у крайньому правому стовпці таблиці на рис. 7.68. Схема дешифратора, що перетворює код станів лічильника Джонсона в унітарний код y5y4y3y2y1y0, показана на рис. 7.67.

За рахунок використання дешифратора на кон’юнкто-рах затримка сигналів у схемі лічильника Джонсона більша ніж у кільцевому лічильнику, тому час установлення коду для нього дорівнює tуст = tз.пер + tзп.кон (tз.пер – час затримки перемикання тригера, tзп.кон – час затримки поширення кон’юнктора). Відповідно збільшується роздільна здатність лічильника Джонсона tроз.лч і зменшується максимальна частота лічби fmax: tроз.лч = tроз + tзп.кон (tроз розділяючий час тригера), fmax = 1/(tроз + tзп.кон).

Кільцеві лічильники, побудовані за схемою лічильника Джонсона, входять до складу деяких серій мікросхем. Як приклад наведемо мікросхему 564ИЕ9 (функціональний аналог CD4022BC), умовне графічне зображення якої показано на рис. 7.69.

|

Рис. 7.69. Умовне графічне зображення мікросхеми 564ИЕ9 |

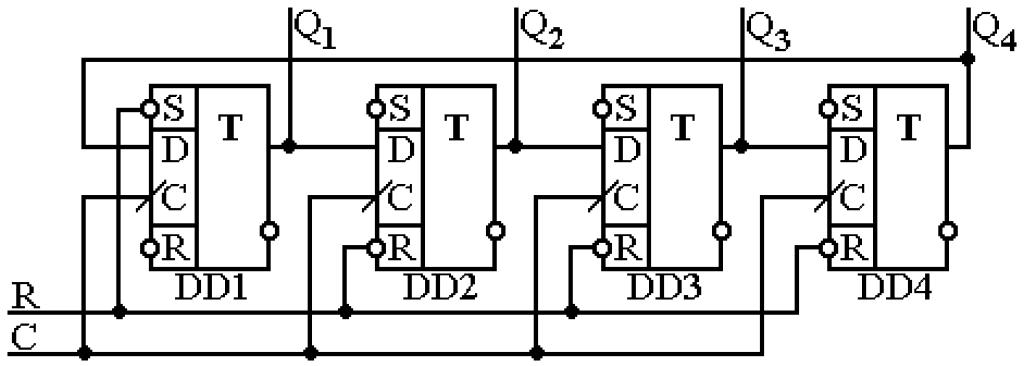

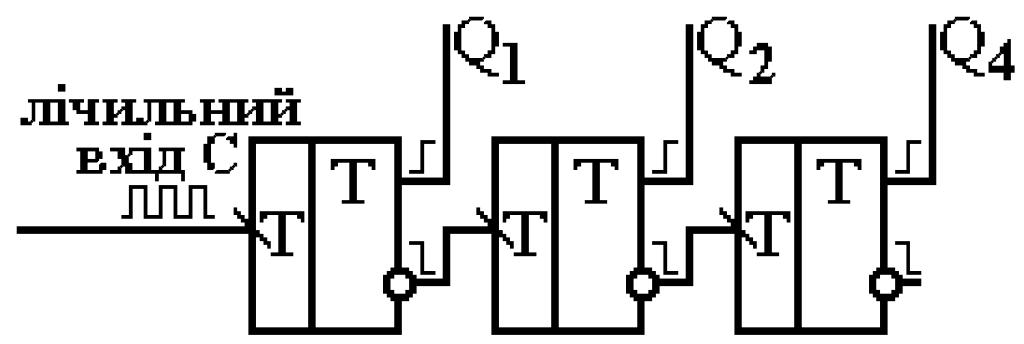

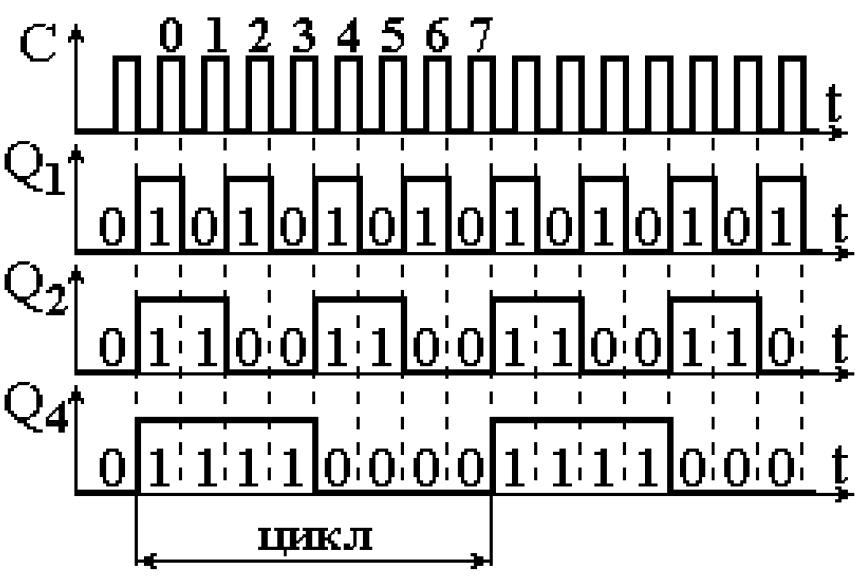

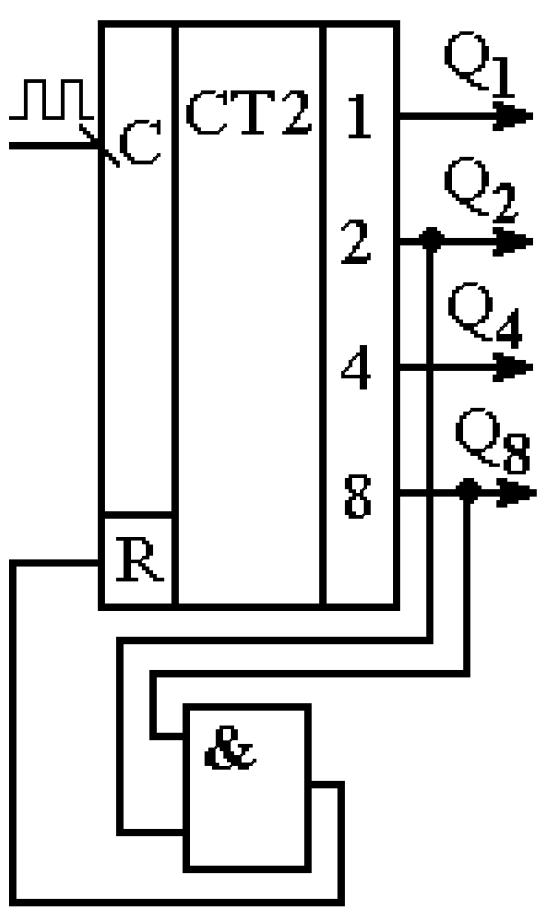

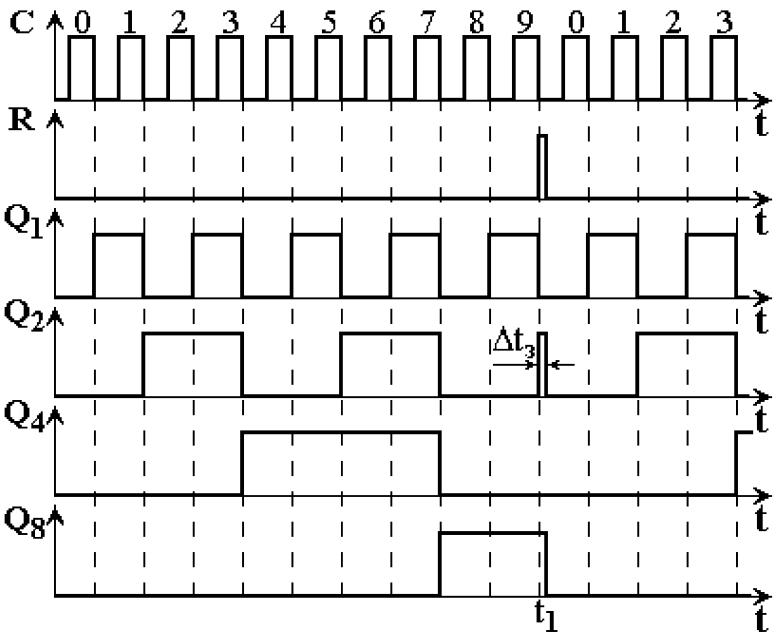

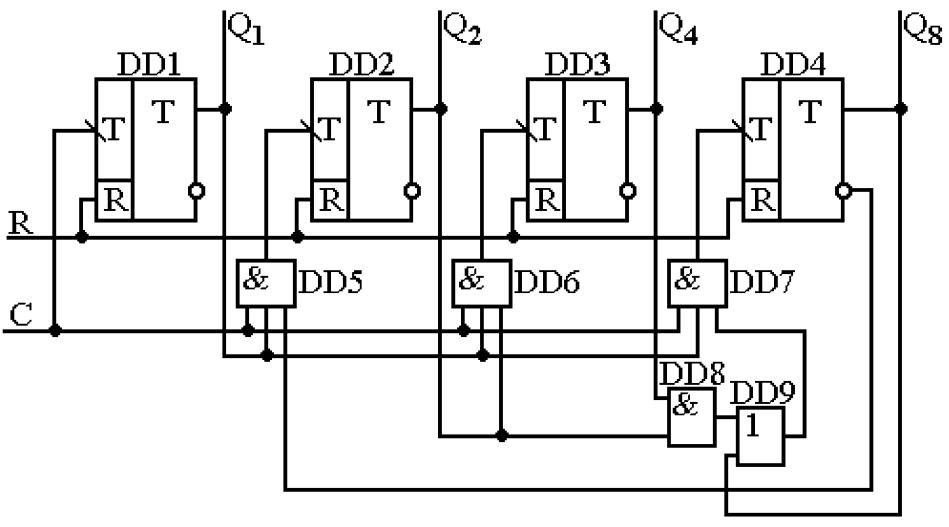

7.4.6. Двійкові лічильники. Двійкові лічильники перетворюють кількість імпульсів, що надійшли на їх вхід, у двійкове число (двійковий код). Основою двійкових лічильників є T-тригери. Як було показано у підрозділі 5.6 таки тригери перемикаються у протилежний стан при надходженні на їх вхід Т кожного тактового сигналу і тому виконують функцію лічильника з коефіцієнтом лічби Клч = 2. Для реалізації n-розрядного двійкового лічильника Т-тригери послідовно з’єднують між собою, таким чином, що певна зміна сигналу на виході тригера молодшого розряду викликає перемикання тригера сусіднього старшого розряду. Тому n-розрядний двійковий лічильник на своїх виходах формує n-розрядне двійкове число, яке дорівнює кількості імпульсів, що надійшли на лічильний вхід. Оскільки кількість n-розрядних двійкових чисел дорівнює 2n, то таку ж кількість станів має й двійковий лічильник, тобто його коефіцієнт лічби дорівнює

Клч = 2n. (7.59)

Т-тригери, з яких складається двійковий лічильник реалізують на базі універсальних синхронних JK- та D-тригерів з динамічним керуванням згідно схемам, показаним на рис. 5.43а і 5.44а. Оскільки у якості Т входу використовують динамічний вхід синхронізації JK- і D-тригерів, то Т-тригери мають інформаційний вхід Т з динамічним керуванням або по фронту (перепадом напруги ), або по зрізу (перепадом напруги ) тактового імпульсу.

Підсумовуючі та віднімальні двійкові лічильники з послідовним перенесенням можуть бути побудовані як на Т-тригерах з прямим (по фронту імпульсу ), так і зворотним (по зрізу імпульсу ) керуванням. Для визначення структури таких лічильників розглянемо зростаючу і спадаючу послідовності трьохрозрядних двійкових чисел, що наведені у таблицях на рис. 7.70. Перша з них відповідає послідовності станів підсумовуючого лічильника (початковий стан 000), а друга – послідовності станів віднімального лічильника (початковий стан 111). Зазначимо, що для двійкових лічильників, як індекс виходу Qj, використовують вагу двійкового розряду j = 2i (i = 0,1,2...).

З таблиці (рис. 7.70а) видно, що перемикання будь-якого розряду підсумовуючого лічильника з одиниці в нуль (перепад ) викликає перемикання сусіднього старшого розряду лічильника. З таблиці (рис. 7.70б) випливає, що для віднімального лічильника таке перемикання викликає перепад .

|

|

а |

б |

Рис. 7.70. Послідовності станів трьохрозрядних двійкових лічильників: а підсумовуючого; б віднімального

|

|

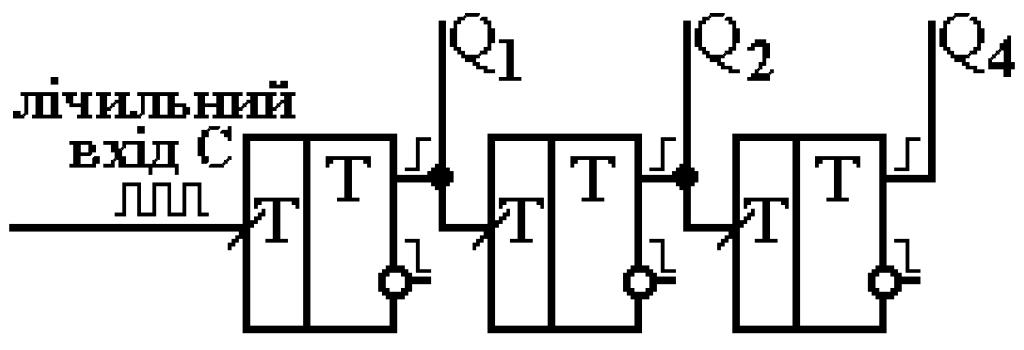

Таким чином, при реалізації на Т-тригерах із зворотним динамічним керуванням (керуванням по зрізу імпульсу ) підсумовуючих лічильників треба з’єднати прямі виходи і входи Т тригерів сусідніх розрядів у напрямку від молодшого до старшого розряду (рис. 7.71а), а коли Т-тригери мають пряме динамічне керування (керування по фронту імпульсу ) – з’єднують інверсні виходи з Т входами (рис. 7.71б). Для реалізації віднімальних лічильників з’єднання виконують навпаки, а саме: коли Т-тригери керовані зрізом імпульсу , інверсні виходи з’єднують з Т входами сусідніх тригерів (рис. 7.71в), а при керуванні по фронту – з’єднують прямі виходи тригерів з Т входами (рис. 7.71г). Двійкові лічильники, побудовані за схемами на рис. 7.71, мають послідовне перенесення, оскільки сигнал, що перемикає Т-тригери, послідовно передається по ланцюгу тригерів починаючи з лічильного входу.

|

|

а |

б |

|

|

в |

г |

Рис. 7.71. Підсумовуючі (а, б) і віднімальні (в, г) двійкові лічильники на Т-тригерах з прямим і зворотним динамічним керуванням

|

|

При побудові часових діаграм підсумовуючих і віднімальних двійкових лічильників враховують таблиці переходів T-тригерів з прямим (рис. 5.43б) або зворотним (рис. 5.44б) динамічним керуванням. Такі часові діаграми для лічильників, побудованих на Т-тригерах зі зворотним керуванням (рис. 5.43), показані на рис. 7.72. При їх побудові, для спрощення, затримки сигналів не враховані і прийнято, що початковим станом, як підсумовуючого так і віднімального лічильників є нульовий стан Q4Q2Q1 = 000.

У відповідності з таблицею справжності Т-тригера із зворотним динамічним керуванням (рис. 5.44б) тригер молодшого розряду Q1 лічильників обох типів перемикається по кожному зрізу тактового сигналу на вході С, тому часові діаграми на виході Q1 мають однаковий вигляд, як для підсумовуючого, так й для віднімального лічильників (рис. 7.72а та рис. 7.72б). Оскільки згідно схемам таких лічильників (рис. 7.71) сигнали на Т входи тригерів старших розрядів надходять з прямих або інверсних виходів тригерів сусідніх молодших розрядів, у випадку підсумовуючого лічильника (рис. 7.71а) тригери старших розрядів перемикаються по перепаду напруги на прямих виходах цих тригерів, а у випадку віднімального лічильника (рис. 7.71в) – по інверсному перепаду напруги на прямих виходах. Це приводить до того, що на виходах підсумовуючого лічильника формується зростаюча послідовність двійкових кодів (рис. 7.72а), а на виходах віднімального лічильника спадаюча послідовність (рис. 7.72б). За один цикл своєї роботи лічильники здатні підраховувати 23 = 8 імпульсів.

|

|

а |

б |

Рис. 7.72. Часові діаграми сигналів на прямих виходах підсумовуючого (а) і віднімального (б) двійкових лічильників

|

|

З часових діаграм (рис. 7.72) видно, що на кожному виході двійкового лічильника частота ділиться на два. Тому у загальному випадку коефіцієнт ділення частоти на будь-якому k-тому виході n-розрядного двійкового лічильника визначається співвідношенням: Кділ = 2-k (k = 1,2,3,...,n нумерація виходів лічильника, починаючи з молодшого розряду). Оскільки при переході до будь-якого нового стану лічильника з послідовним перенесенням відбувається послідовне у часі перемикання Т-тригерів, затримки накопичуються. Найбільша затримка установлення коду має місце при завершенні циклу, коли лічильник перемикається від стану переповнення у початковий стан (від 11...11 до 00...00 для підсумовуючого і від 00...00 до 11...11 для віднімального лічильника). Саме ця затримка, з урахуванням найгіршого випадку, коли для встановлення нового стану повинні перемкнутися усі Т-тригери, визначає час установлення коду двійкового лічильника з послідовним перенесенням:

tуст = ntз.пер, (7.60)

де tз.пер – затримка перемикання Т-тригера, n – кількість розрядів двійкового лічильника. З урахуванням (7.60) максимальна частота лічби двійкового лічильника з послідовним перенесенням визначається як fmax = 1/ntз.пер.

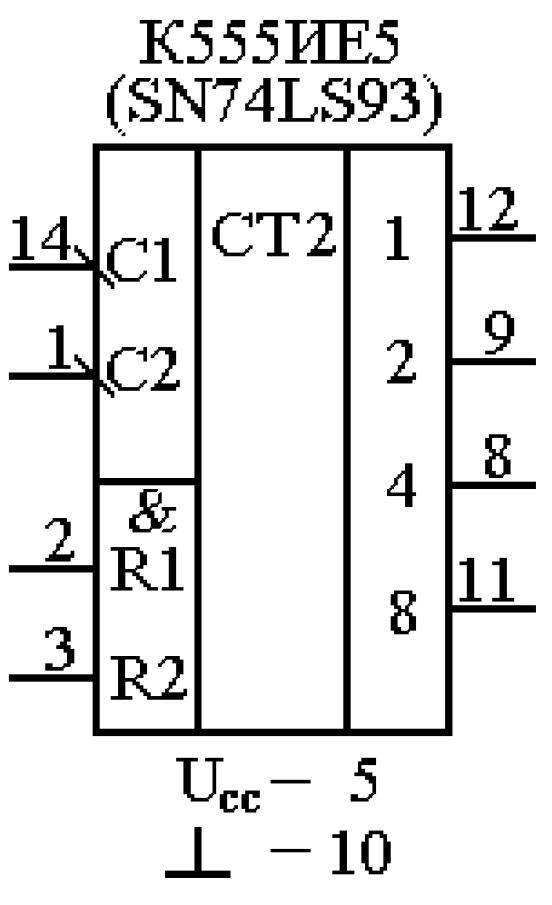

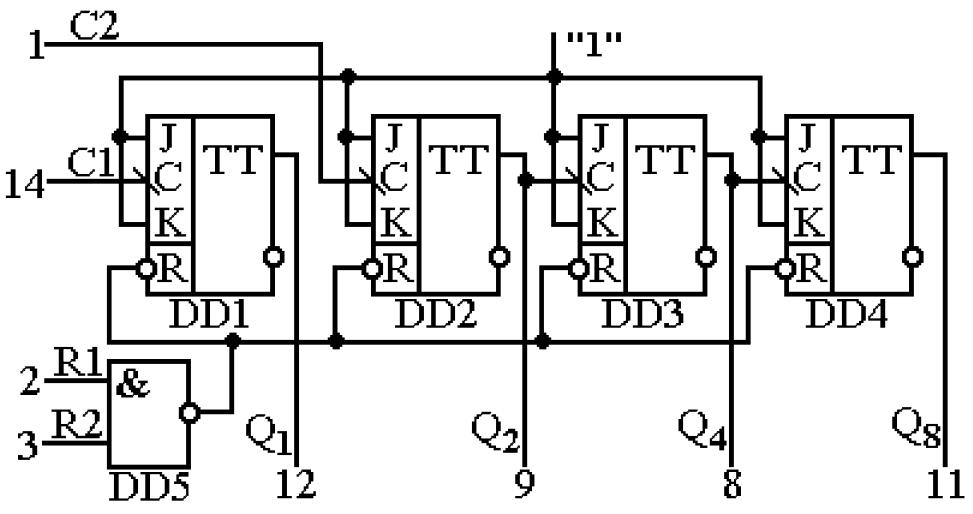

Підсумовуючи двійкові лічильники з послідовним перенесенням входять до складу серій мікросхем ТТЛШ і КМОПТЛ. До такого типу лічильників належать, зокрема, 4-х розрядний двійковий лічильник К555ИЕ5 (SN74LS93) і 12-ти розрядний лічильник КР1561ИЕ20 (MC14040B). Умовне зображення і схема лічильника К555ИЕ5 показані на рис. 7.73.

Основою цього лічильника є двохступеневі JKRS-тригери зі зворотним динамічним керуванням, увімкнені як T-тригери (рис. 5.44а). Сукупність T-тригерів DD2 – DD4 складає трьохрозрядний двійковий лічильник з послідовним перенесенням і лічильним входом С2. Тригер DD1 може бути використаним, як окремий Т-тригер. Якщо його вихід Q1 з’єднати зі входом С2, то утворюється чотирьохрозрядний двійковий лічильник з лічильним входом С1. Мікросхема має два входи обнуління R1 і R2, зв’язані логічною операцією І (рис. 7.73а)

|

|

а |

б |

Рис. 7.73. Умовне графічне зображення мікросхеми двійкового лічильника з послідовним перенесенням К555ИЕ5 (а) і її логічна структура (б)

|

|

При нарощуванні розрядності лічильників з послідовним перенесенням входи обнуління мікросхем об’єднують між собою, а вихід старшого розряду кожної мікросхеми з’єднують з лічильним входом мікросхеми сусідніх старших розрядів. Для лічильника, нарощеного таким чином, лічильним входом є відповідний вхід мікросхеми молодших розрядів.

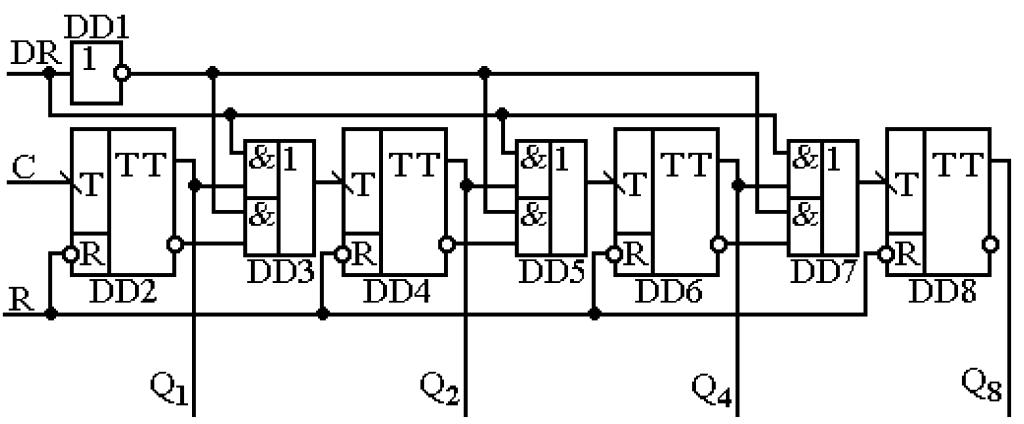

Реверсивні двійкові лічильники мають у схемі обидва типи зв’язків між Т-тригерами, що притаманні як підсумовуючим (рис. 7.71а), так і віднімальним (рис. 7.71в) лічильникам. Перемикання цих зв’язків, для забезпечення заданого напрямку лічби, здійснюють за допомогою логічних елементів ІАБО чи ІАБОНЕ. Один з можливих способів організації реверсивних двійкових лічильників ілюструє схема, показана на рис. 7.74.

|

Рис. 7.74. Схема реверсивного двійкового лічильника з послідовним перенесенням

|

В цій схемі зв’язок між прямими виходами і Т-входами сусідніх тригерів, що забезпечує прямий напрямок лічби, здійснюється через верхні секції І логічних елементів ІАБО DD3, DD5, DD7, а зв’язок між інверсними виходами і входами Т, що забезпечує зворотну лічбу, – через нижні секції І цих елементів. Логічний нуль, який є активним сигналом для елементів І, блокує такий зв’язок, а логічна одиниця дозволяє. Тому при наявності на вході DR, який керує напрямком лічби, логічної одиниці, дозволяється зв’язок між Т-тригерами, що використовується у підсумовуючих лічильниках (рис. 7.71а) і логічним нулем з виходу інвертора DD1 блокується зв’язок між Т-тригерами характерний для віднімальних лічильників (рис. 7.71в). Схема, наведена на рис. 7.74 працює як підсумовуючий лічильник. При DR = 0, блокування зв’язків між виходами і Т-входами тригерів має зворотний характер, тому схема на рис. 7.74 працює як віднімальний лічильник.

Недоліком лічильників з послідовним перенесенням є низька швидкодія, що є наслідком послідовного у часі перемикання розрядних тригерів таких лічильників. Цей недолік усунуто у двійкових лічильниках з паралельним перенесенням, в яких Т-тригери всіх розрядів перемикаються одночасно.

Для визначення особливостей побудови двійкових лічильників з паралельним перенесенням розглянемо додавання одиниці до будь якого довільного багаторозрядного двійкового числа:

![]() .

.

З наведеного прикладу випливає, що при збільшенні двійкового числа на одиницю відбувається інверсія (перемикання у протилежний стан) всіх його молодших розрядів аж до першого, в якому логічний „0”, включаючи цей розряд. Старші розряди числа, за першим нульовим розрядом не змінюють своїх значень.

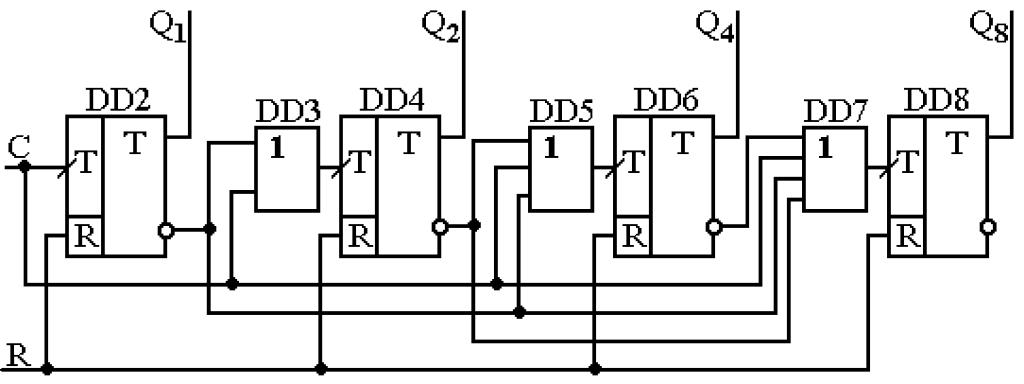

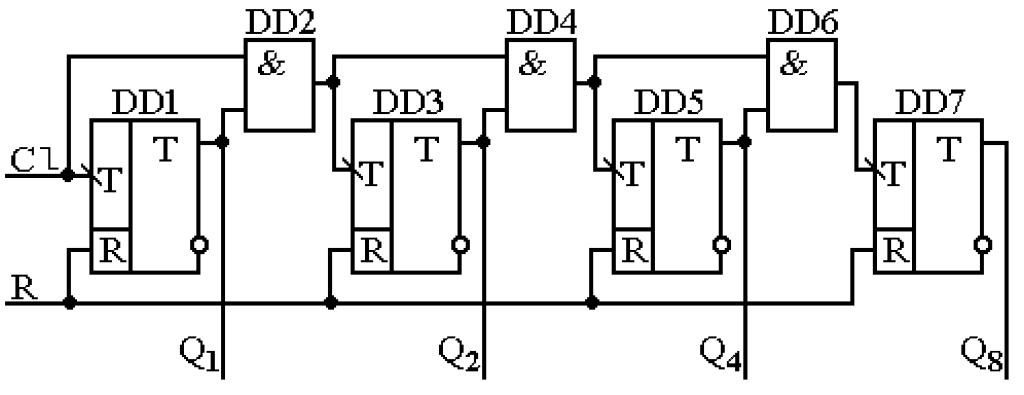

Розглянутий вище приклад свідчить про те, що при одночасному надходженні лічильного сигналу на всі Т-тригери підсумовуючого лічильника з паралельним перенесенням, цей сигнал повинен перемикати лише Т-тригери молодших розрядів, включаючи перший з них, на прямому виході якого логічний „0”, а на інверсному – логічна „1”. Передача лічильного сигналу на Т входи інших тригерів лічильника повинна блокуватися. Таке блокування можна реалізувати, якщо передавати лічильний сигнал на вхід Т кожного тригера через логічний елемент І, до інших входів якого підключені прямі виходи Т-тригерів попередніх молодших розрядів. Можна також використати логічний елемент АБО, входи якого з’єднані з інверсними виходами тригерів попередніх молодших розрядів. Схема підсумовуючого двійкового лічильника, який використовує для організації паралельного перенесення логічні елементи АБО показана на рис. 7.75.

|

Рис. 7.75. Схема двійкового лічильника з паралельним перенесенням

|

Лічильний сигнал зі входу С надходить одночасно на кожний Т-тригер через логічні елементи АБО DD3, DD5, DD7. Інші входи цих елементів з’єднані з інверсними виходами тригерів попередніх молодших розрядів лічильника. Якщо хоча б один з цих тригерів у нульовому стані, логічна одиниця з його інверсного виходу, яка є активним сигналом для елемента АБО, блокує передачу перемикаючого сигналу на Т-тригери наступних старших розрядів лічильника і їх стан не змінюється. Перемикаються тільки тригери молодших розрядів, що у стані логічної одиниці і перший з них у стані логічного нуля, оскільки пасивний для АБО сигнал логічного нуля не блокує передачу на них перемикаючого сигналу . Таким чином відбувається зміна двійкового коду на виході підсумовуючого лічильника, відповідно з правилами зміни розрядів двійкового числа при збільшенні його на одиницю, як показано у прикладі наведеному вище. Сигнал високого рівня напруги на вході R лічильника (R=1) скидає його у нульовий стан.

Оскільки у лічильниках з паралельним перенесенням лічильний сигнал надходить одночасно на тригери всіх розрядів, час установлення коду не залежить від розрядності лічильника і визначається затримкою перемикання Т-тригера tз.пер і затримкою поширення сигналу елемента АБО tзп.диз:

tуст = tз.пер + tзп.диз, (7.61)

відповідно максимальна частота лічення двійкового лічильника з паралельним перенесенням визначається як fmax = 1/(tз.пер + tзп.диз).

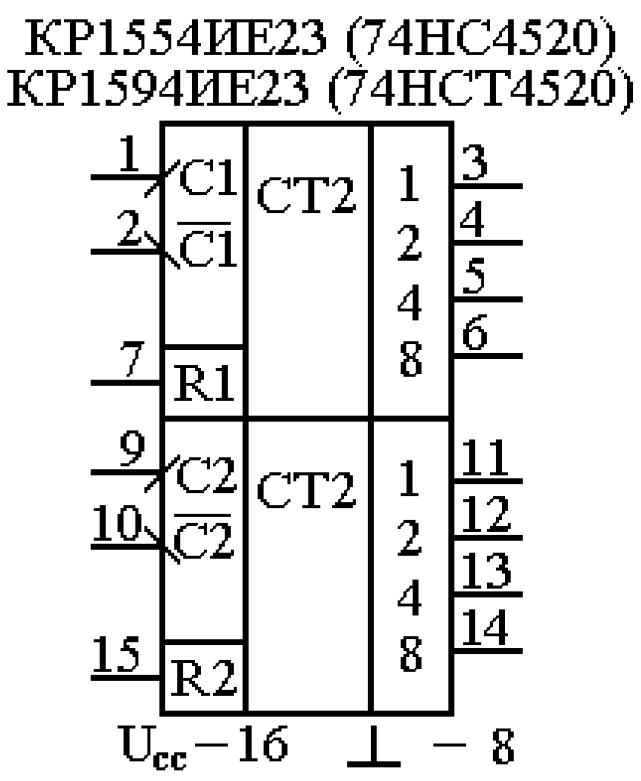

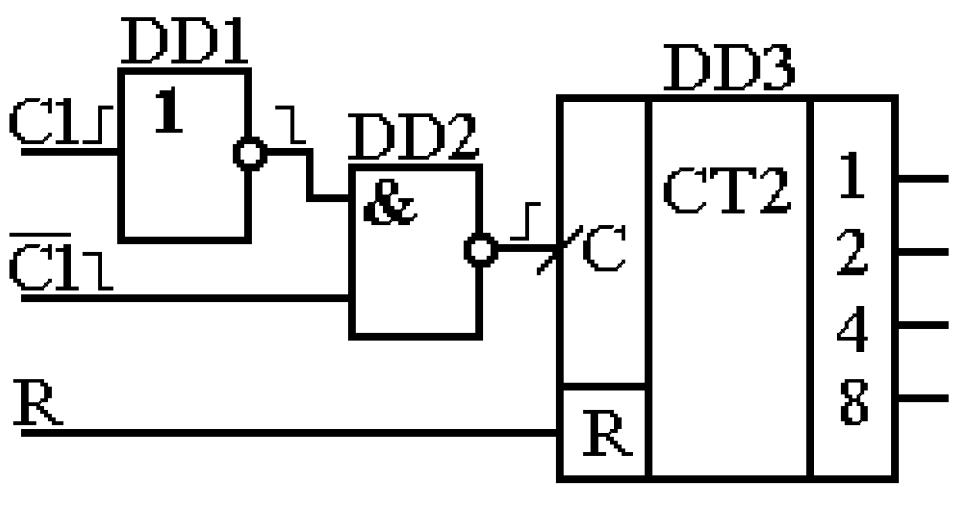

За схемою, наведеною на рис. 7.75 реалізовано інтегральні лічильники КР1554ИЕ23 (74HC4520) та КР1594ИЕ23 (74HCT4520), умовне графічне зображення яких показано на рис. 7.76а.

|

|

а |

б |

Рис. 7.76. Умовне графічне зображення мікросхем КР1554ИЕ23 і КР1594ИЕ23 (а) та схема організації їх лічильних входів (б)

|

|

Ці

мікросхеми містять два чотирьохрозрядних

підсумовуючих лічильника з паралельним

перенесенням. Кожний з них має два

лічильних входи з прямим (по фронту

імпульсу

)

та зворотним (по зрізу імпульсу

)

динамічним керуванням. Для організації

таких входів використовується схема

показана на рис. 7.76б. Тут DD3

двійковий лічильник, реалізований за

схемою наведеною на рис. 7.75. При

використанні

![]() як лічильного входу на вході С1 повинна

бути напруга низького рівня (С1 = 0). В

цьому випадку з інвертора DD1

на елемент ІНЕ

DD2

поступає логічна одиниця, яка не блокує

передачу лічильного сигналу

зі входу

на вхід С лічильника DD3.

Лічильний сигнал

інвертується DD2

у сигнал

,

який сприймається лічильником DD3.

При використанні С1 як лічильного входу

на вході

повинна бути напруга високого рівня (

= 1). Вона дозволяє передачу лічильного

сигналу

зі входу С1, який, завдяки подвійній

інверсії, надходить на вхід С без зміни

і тому сприймається схемою лічильника

DD3.

як лічильного входу на вході С1 повинна

бути напруга низького рівня (С1 = 0). В

цьому випадку з інвертора DD1

на елемент ІНЕ

DD2

поступає логічна одиниця, яка не блокує

передачу лічильного сигналу

зі входу

на вхід С лічильника DD3.

Лічильний сигнал

інвертується DD2

у сигнал

,

який сприймається лічильником DD3.

При використанні С1 як лічильного входу

на вході

повинна бути напруга високого рівня (

= 1). Вона дозволяє передачу лічильного

сигналу

зі входу С1, який, завдяки подвійній

інверсії, надходить на вхід С без зміни

і тому сприймається схемою лічильника

DD3.

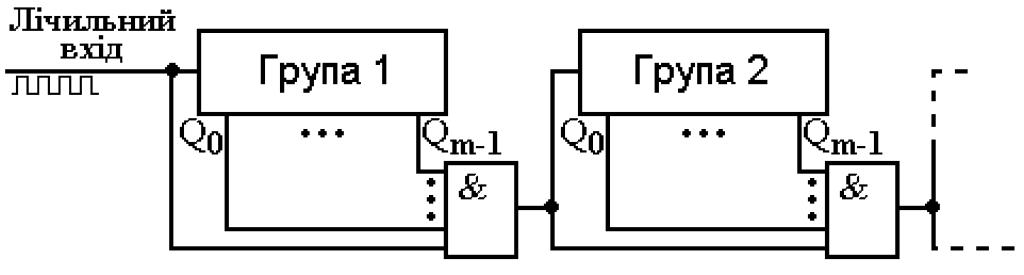

При зростанні кількості розрядів реалізація паралельних лічильників ускладнюється. Це обумовлено зростанням навантаження на виходи тригерів, особливо тригера молодшого розряду (див. схему на рис. 7.75), і зростанням кількості входів логічних елементів І чи АБО, які потрібні для організації паралельного перенесення. У зв’язку з обмеженнями, які виникають при побудові лічильників з паралельним перенесенням, поширене розповсюдження отримали лічильники з груповим перенесенням, які будуть розглянуті нижче.

Двійкові лічильники з крізним перенесенням використовують послідовний ланцюг кон’юнкторів для передачі лічильного сигналу на Т-тригери з урахуванням стану тригерів попередніх молодших розрядів. Схема підсумовуючого лічильника з крізним перенесенням показана на рис. 7.77.

|

Рис. 7.77. Схема двійкового лічильника з крізним перенесенням

|

Лічильний сигнал , що надходить на вхід С, передається по ланцюгу послідовно увімкнених логічних елементів 2І DD2, DD4, DD6, другий вхід яких підключений до прямих виходів Т-тригерів. Якщо хоча б один з цих тригерів знаходиться у нульовому стані, передача лічильного сигналу на тригери подальших старших розрядів блокується починаючи з логічного елемента 2І, вхід якого підключений до виходу першого з тригерів молодших розрядів установленого в нульовий стан.

На відміну від лічильника з паралельним перенесенням (рис. 7.75), для схеми лічильника з крізним перенесенням (рис. 7.77) відсутнє обмеження розрядності пов’язане з перевантаженням Т-тригерів молодших розрядів і максимально дозволеною кількістю входів кон’юнктора.

Час установлення коду двійкового лічильника з крізним перенесенням визначається сумою затримки перемикання Т-тригера tз.пер і максимальної затримки розповсюдження лічильного сигналу у послідовному ланцюгу кон’юнкторів, яка при розрядності лічильника n дорівнює (n 1)tзп.кон (tзп.кон затримка поширення сигналу кон’юнктора):

tуст = tз.пер + (n 1)tзп.кон. (7.62)

Порівняння співвідношень (7.60) і (7.62) показує, що при однаковій розрядності виграш у швидкодії лічильників з крізним перенесенням, порівняно з лічильниками з послідовним перенесенням, тим більший, чим менше затримка поширення кон’юнкторів tзп.кон порівняно з затримкою перемикання Т-тригерів tз.пер.

В двійкових лічильниках з груповим перенесенням Т-тригери, з яких складається лічильник, поділені на групи, в межах яких здійснюється один з типів перенесення розглянутих вище, а групи зв’язані між собою ланцюгами міжгрупового перенесення. Звичайно поміж групами організують крізне перенесення, як показано на рис. 7.78.

|

Рис. 7.78. Структура лічильника з груповим перенесенням

|

При одиничному стані всіх тригерів групи надходження чергового лічильного сигналу створює перенесення з цієї групи у наступну групу. Цьому сприяє міжгруповий кон’юнктор, на один зі входів якого подається лічильний сигнал або сигнал перенесення попередньої групи, а інші входи з’єднані з виходами тригерів поточної групи (рис. 7.78). Сигнал перенесення з виходу міжгрупового кон’юнктора надходить на лічильний вхід наступної групи та міжгруповий кон’юнктор цієї групи. Таким чином він розповсюджується по ланцюгу міжгрупових кон’юнкторів, так як це має місце у двійковому лічильнику з крізним перенесенням. Блокування розповсюдження лічильного сигналу на наступні групи відбувається при нульовому стані хоча б одного з тригерів поточної групи. Час установлення коду лічильника з груповим перенесенням визначається виходячи з найгіршого для швидкодії випадку, коли сигнал перенесення проходить через усі групи і надходить на вхід останньої

tуст = tуст.гр + (l 1)tзп.кон, (7.63)

де l кількість груп; tуст.гр час установлення коду у групі.

На підставі (7.63) можна визначити tуст для n розрядних двійкових лічильників з груповим перенесенням, які мають різний тип перенесення в межах групи. Якщо у таких лічильниках l груп, то кожна з них містить n/l Т-тригерів. У випадку, коли в межах груп перенесення паралельне, на підставі (7.61) і (7.63), одержимо наступний вираз для часу установлення коду:

tуст = tз.пер + tзп.диз + (l 1)tзп.кон ≈ tз.пер + ltзп.кон, (7.64)

а якщо між Т-тригерами групи має місце крізне перенесення, урахування (7.62) приводить до виразу:

![]() . (7.65)

. (7.65)

Розвинені серії інтегральних мікросхем звичайно містять від 4-ох до 11 варіантів двійкових лічильників, які, як правило, є 4-ох розрядними. Нарощування розрядності (каскадування) лічильників може виконуватися шляхом послідовного включення мікросхем по ланцюгам перенесення або організації паралельно послідовного перенесення за допомогою кон’юнкторів. В останньому випадку структура нарощеного лічильника відповідає рис. 7.78 і він фактично є лічильником з груповим перенесенням, в якому кожна група – це інтегральна мікросхема лічильника.

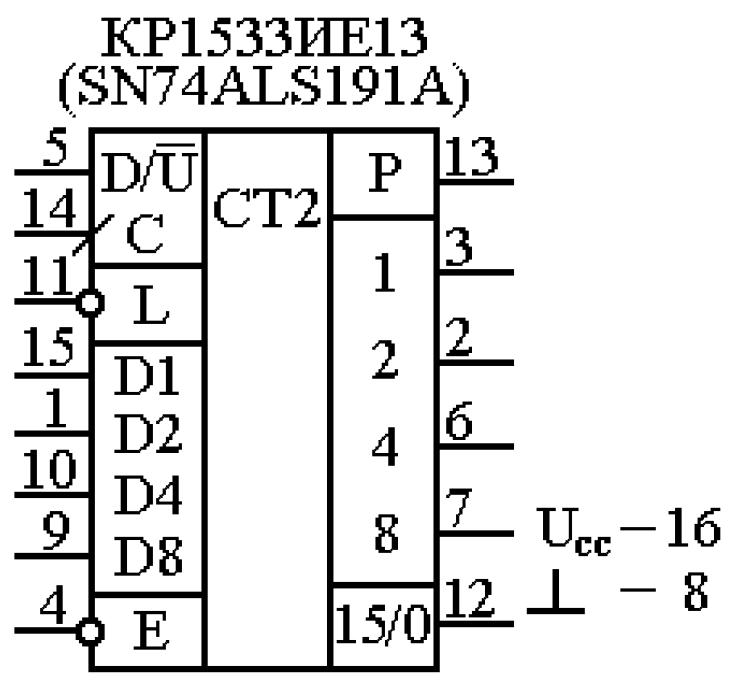

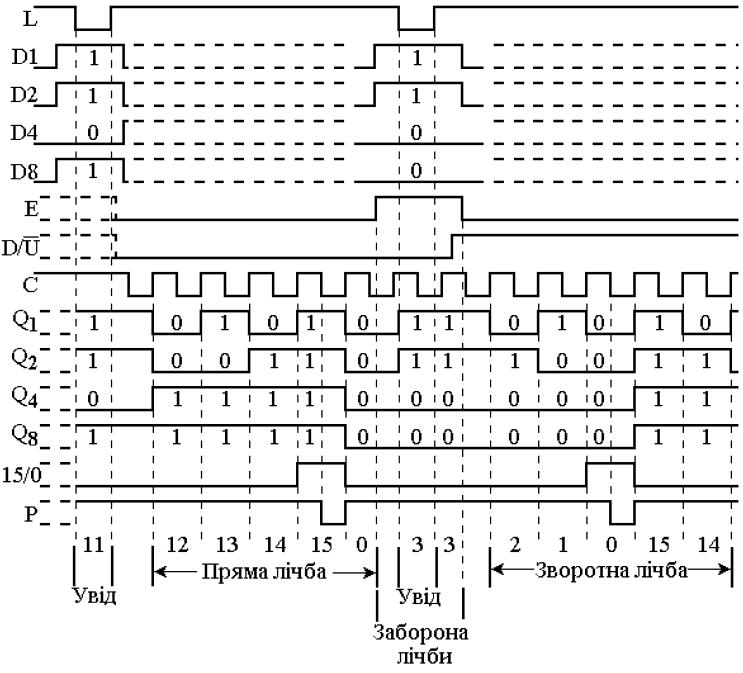

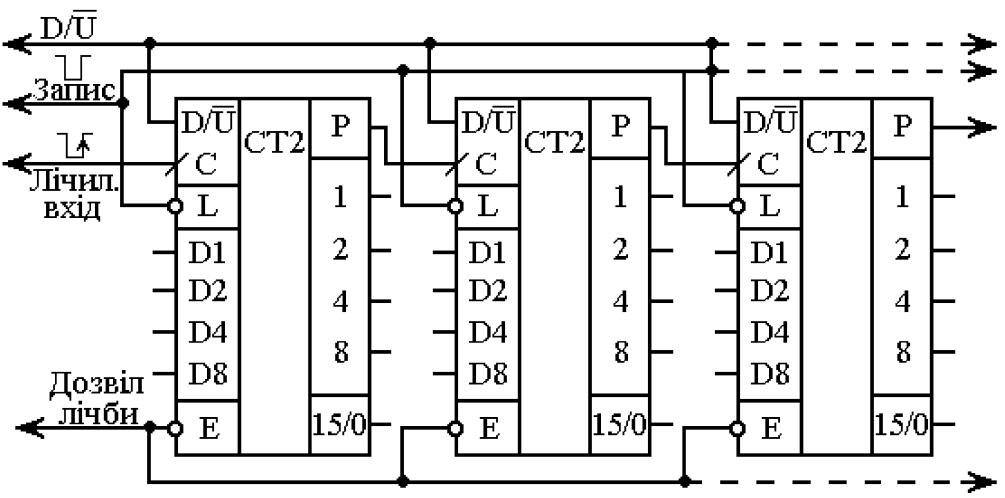

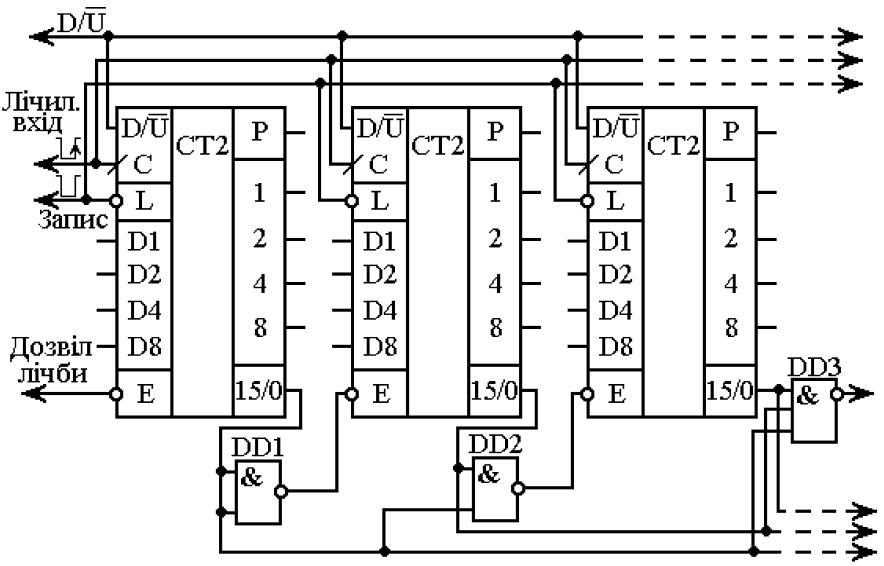

Реверсивні лічильники з паралельним завантаженням двійкового слова називають також програмованими лічильниками. Завдяки паралельному завантаженню такі лічильники можна установити в будь-який стан для початку лічба і, тим самим, програмним шляхом змінювати коефіцієнт лічби.

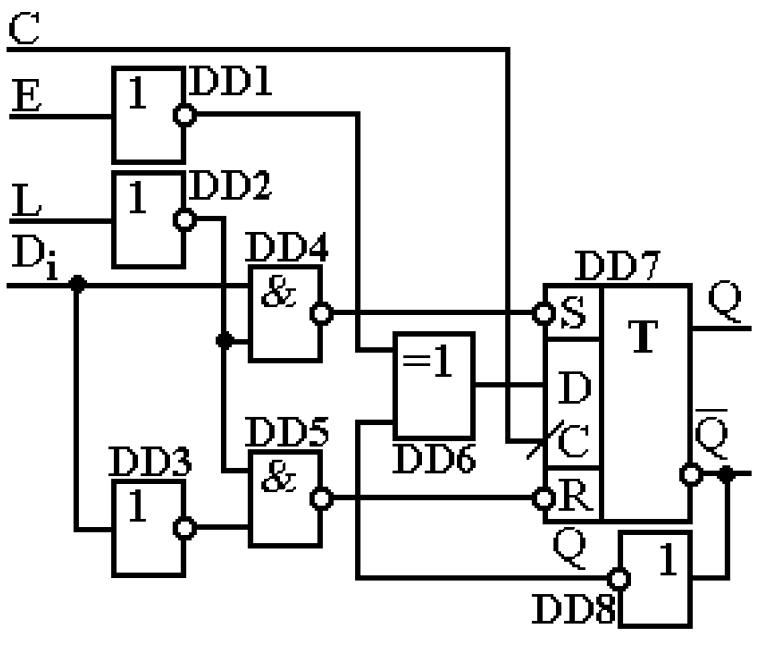

Лічильники з паралельним завантаженням можна будувати на DRS-тригерах, увімкнених як показано на рис. 7.79. Лічильний сигнал С подається на тактовий вхід DRS-тригера, а завантаження біта Di двійкового слова здійснюється через входи попередньої установки тригера R і S. Це відбувається при сигналі логічного нуля на вході L (L=0), коли логічна одиниця з виходу DD2 деблокує елементи 2ІНЕ DD4, DD5, тобто дозволяє паралельний увід. На ви-

|

Рис. 7.79. Схема управління DRS-тригером в лічильниках з паралельним завантаженням |

Лічильний режим роботи дозволяється при Е = 0, L = 1, коли нуль на виході DD2 забезпечує = 1, = 1 і DRS-тригер працює в синхронному режимі (див. таблицю переходів на рис. 5.25). Одиниця з виходу DD1 перетворює елемент „сума за модулем 2” DD6 в інвертор, тому D = і синхронний D-тригер працює як Т-тригер (рис. 5.43), тобто перемикається у протилежний стан по кожному перепаду на вході С. Сигнал Е = 1 при L = 1 забороняє лічильний режим, оскільки в цьому випадку DD6 працює як повторювач і тому D = Q. По кожному перепаду на вході С тригер перезаписує інформацію, яка в ньому зберігається і його стан не змінюється.

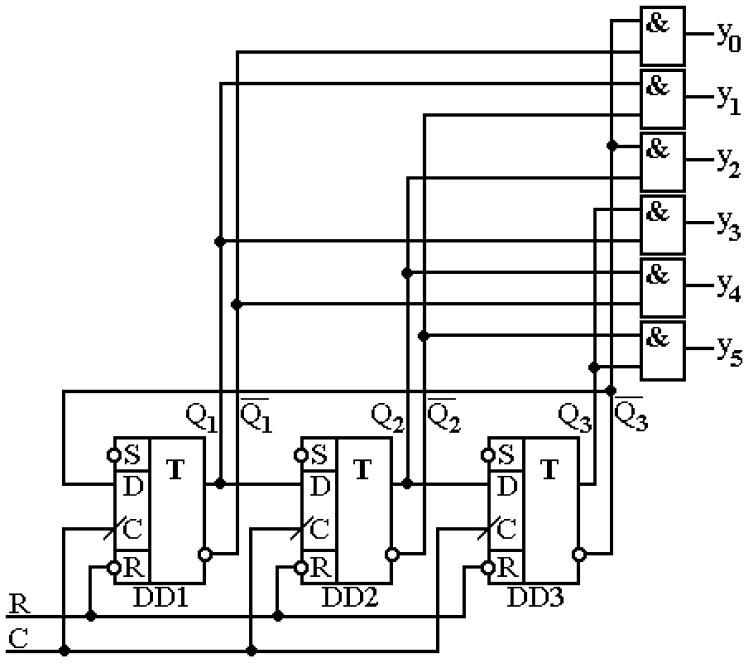

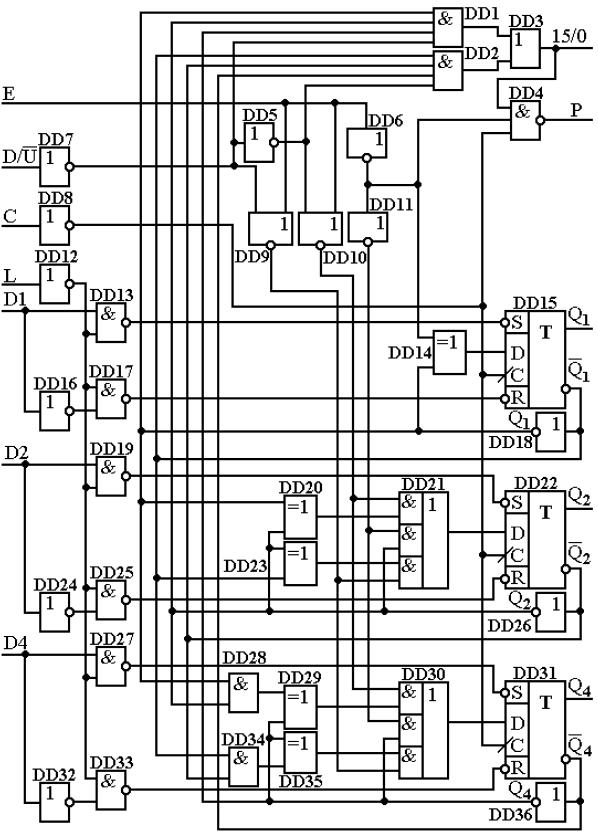

Схема трьохрозрядного реверсивного програмованого двійкового лічильника з паралельним перенесенням показана на рис. 7.80.

Завантаження в лічильник двійкового слова D4D2D1 з відповідних паралельних входів здійснюється сигналом низького рівня напруги U0 на вході L (L = 0) так, як було описано вище. Для цього використовуються входи і комбінованих DRS-тригерів, які мають більш високий пріоритет установки стану тригера ніж входи D і С (див. підрозділ 5.4.2). Сигнали на входах і тригерів DD15, DD22, DD31 формуються відповідно зі значеннями бітів двійкового слова за допомогою схем на логічних елементах DD12, DD13, DD16, DD17, DD19, DD24, DD25, DD27, DD32, DD33 і забезпечують запис слова в тригери лічильника таким чином, що Q4 = D4, Q2 = D2, Q1 = D1.

Схема на рис. 7.80 має обидва типи зв’язків між тригерами, що забезпечують пряму і зворотну лічбу. Для керування цими зв’язками використовуються логічні елементи 2І3АБО DD21, DD30. Паралельне перенесення в схемі забезпечують логічні елементи DD20, DD23, DD28, DD29, DD34, DD35. Відзначимо, що зв’язки між тригерами для роботи лічильника в підсумовуючому режимі увімкнені через елемент DD20, верхню секцію 2І DD21, елементи DD28, DD29 та верхню секцію 2І DD30. Зв’язки для зворотної лічби здійснюються через логічний елемент DD23, нижню секцію 2І DD21, елементи DD34, DD35 та нижню секцію 2І DD30.

|

Рис. 7.80. Схема реверсивного програмованого лічильника |

Лічильний режим роботи схеми на рис. 7.80 реалізується тільки при наявності на вході L високого рівня напруги U1 (L = 1), який переводе DRS-тригери лічильника в синхронний режим роботи, оскільки при L = 1 на входах попередньої установки цих тригерів логічні сигнали = 1, = 1. Зазначимо, що лічильний режим роботи може бути заборонений сигналом високого рівня напруги U1 на вході E (E = 1). В цьому випадку логічні нулі з виходів DD9, DD10 блокують верхні і нижні секції 2І елементів DD21, DD31, через які здійснюються зв’язки між тригерами для прямої і зворотної лічби, а логічна одиниця, що надходить з виходу DD11, деблокує середні секції 2І DD21, DD30, через які на входи D тригерів DD22, DD30 з виходів DD26, DD36 передаються значення логічних сигналів Q2, Q4 на прямих виходах тригерів. Теж саме, стосовно тригера DD15, здійснює логічний елемент DD14, оскільки завдяки нулю з виходу DD6 він працює як повторювач, тобто передає значення Q1 на вхід D тригера DD15. Таким чином при E = 1 тригери лічильника по кожному перепаду сигналу на лічильному вході С перезаписують інформацію, яку вони зберігають і тому стан лічильника не змінюється.

Дозвіл

лічильного режиму роботи забезпечує

сигнал низького рівня напруги U0

на вході Е (Е = 0), який деблокує логічні

елементи DD9,

DD10

і блокує середні секції 2І елементів

DD21,

DD30.

Логічна одиниця з виходу DD6

перетворює DD14

в інвертор і тригер молодшого розряду

лічильника DD15

починає працювати як Т-тригер, оскільки

для нього D

=

![]() .

.

Керування

напрямком лічби здійснюється сигналами

на вході D/![]() .

При Е = 0 сигнал низького рівня U0

на цьому вході (D/

= 0) забезпечує прямий напрямок лічби,

сигнал високого рівня U1

(D/

= 1)

зворотний. Нехай, наприклад, D/

= 0, тоді на виході DD9

логічний нуль, який блокує зв’язки між

тригерами для зворотної лічби, а логічна

одиниця з виходу DD10

деблокує верхні секції 2І елементів

DD21,

DD30,

тобто дозволяє пряму лічбу. Дійсно,

нехай, наприклад, лічильник знаходиться

у стані Q4Q2Q1

= 011. Тоді елемент DD20

працює як інвертор, оскільки на нього

надходить логічна одиниця з DD26,

а DD29

– як повторювач, завдяки логічному нулю

з виходу DD36.

Тому на інформаційному вході D

тригера DD22

за рахунок інверсії Q1

логічний нуль, а на відповідному вході

тригера DD31

D

= Q2