- •Features

- •Pin Configurations

- •Disclaimer

- •Overview

- •Block Diagram

- •Pin Descriptions

- •Port B (PB5..PB0)

- •RESET

- •AVR CPU Core

- •Introduction

- •Architectural Overview

- •Status Register

- •Stack Pointer

- •Interrupt Response Time

- •SRAM Data Memory

- •Data Memory Access Times

- •EEPROM Data Memory

- •EEPROM Read/Write Access

- •Atomic Byte Programming

- •Split Byte Programming

- •Erase

- •Write

- •I/O Memory

- •Clock Systems and their Distribution

- •CPU Clock – clkCPU

- •I/O Clock – clkI/O

- •Flash Clock – clkFLASH

- •ADC Clock – clkADC

- •Clock Sources

- •Default Clock Source

- •External Clock

- •System Clock Prescaler

- •Switching Time

- •Idle Mode

- •Power-down Mode

- •Analog to Digital Converter

- •Analog Comparator

- •Brown-out Detector

- •Internal Voltage Reference

- •Watchdog Timer

- •Port Pins

- •Resetting the AVR

- •Reset Sources

- •Power-on Reset

- •External Reset

- •Brown-out Detection

- •Watchdog Reset

- •Watchdog Timer

- •Timed Sequences for Changing the Configuration of the Watchdog Timer

- •Safety Level 1

- •Safety Level 2

- •Interrupts

- •I/O Ports

- •Introduction

- •Configuring the Pin

- •Toggling the Pin

- •Reading the Pin Value

- •Unconnected Pins

- •Alternate Port Functions

- •Alternate Functions of Port B

- •Register Description for I/O-Ports

- •Port B Data Register – PORTB

- •External Interrupts

- •8-bit Timer/Counter0 with PWM

- •Overview

- •Registers

- •Definitions

- •Counter Unit

- •Output Compare Unit

- •Force Output Compare

- •Modes of Operation

- •Normal Mode

- •Fast PWM Mode

- •Phase Correct PWM Mode

- •Prescaler Reset

- •External Clock Source

- •Analog Comparator

- •Analog Comparator Multiplexed Input

- •Features

- •Operation

- •Starting a Conversion

- •Changing Channel or Reference Selection

- •ADC Input Channels

- •ADC Voltage Reference

- •ADC Noise Canceler

- •Analog Input Circuitry

- •ADC Accuracy Definitions

- •ADC Conversion Result

- •ADLAR = 0

- •ADLAR = 1

- •debugWIRE On-chip Debug System

- •Features

- •Overview

- •Physical Interface

- •Software Break Points

- •Limitations of debugWIRE

- •debugWIRE Related Register in I/O Memory

- •debugWire Data Register – DWDR

- •Performing a Page Write

- •Reading the Fuse and Lock Bits from Software

- •Preventing Flash Corruption

- •Fuse Bytes

- •Latching of Fuses

- •Signature Bytes

- •Calibration Byte

- •Page Size

- •Serial Downloading

- •Data Polling Flash

- •Data Polling EEPROM

- •Chip Erase

- •Programming the Flash

- •Programming the EEPROM

- •Reading the Flash

- •Reading the EEPROM

- •Power-off sequence

- •Electrical Characteristics

- •Absolute Maximum Ratings*

- •External Clock Drive Waveforms

- •External Clock Drive

- •ADC Characteristics – Preliminary Data

- •Active Supply Current

- •Idle Supply Current

- •Power-down Supply Current

- •Pin Pull-up

- •Register Summary

- •Instruction Set Summary

- •Ordering Information

- •Packaging Information

- •Erratas

- •Table of Contents

ATtiny13

ATtiny13

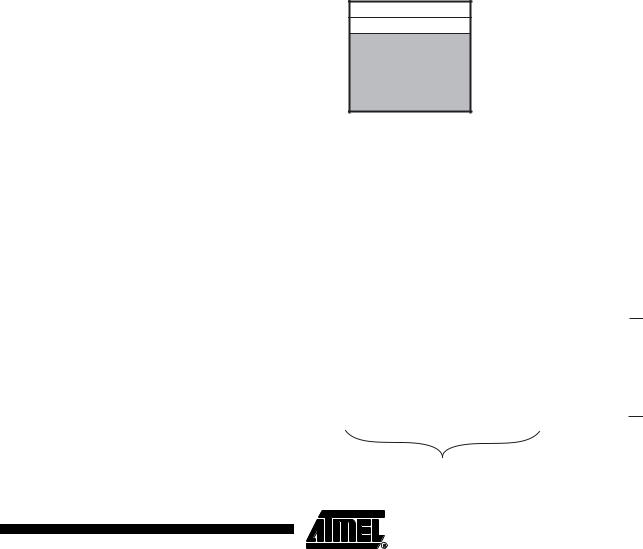

SRAM Data Memory |

Figure 9 shows how the ATtiny13 SRAM Memory is organized. |

|

The lower 160 Data memory locations address both the Register File, the I/O memory |

|

and the internal data SRAM. The first 32 locations address the Register File, the next 64 |

|

locations the standard I/O memory, and the last 64 locations address the internal data |

|

SRAM. |

|

The five different addressing modes for the Data memory cover: Direct, Indirect with |

|

Displacement, Indirect, Indirect with Pre-decrement, and Indirect with Post-increment. In |

|

the Register File, registers R26 to R31 feature the indirect addressing pointer registers. |

|

The direct addressing reaches the entire data space. |

|

The Indirect with Displacement mode reaches 63 address locations from the base |

|

address given by the Y- or Z-register. |

|

When using register indirect addressing modes with automatic pre-decrement and post- |

|

increment, the address registers X, Y, and Z are decremented or incremented. |

|

The 32 general purpose working registers, 64 I/O Registers, and the 64 bytes of internal |

|

data SRAM in the ATtiny13 are all accessible through all these addressing modes. The |

|

Register File is described in “General Purpose Register File” on page 7. |

|

Figure 9. Data Memory Map |

Data Memory

32 Registers

64 I/O Registers

Internal SRAM

(64 x 8)

0x0000 - 0x001F

0x0020 - 0x005F

0x0060

0x009F

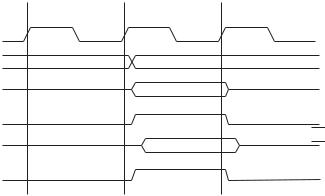

Data Memory Access Times This section describes the general access timing concepts for internal memory access. The internal data SRAM access is performed in two clkCPU cycles as described in Figure 10.

Figure 10. On-chip Data SRAM Access Cycles

T1 T2 T3

clkCPU

Address Compute Address Address valid

Data

WR

Data

RD

Read Write

Read Write

Memory Access Instruction |

Next Instruction |

13

2535A–AVR–06/03