- •Features

- •Pin Configurations

- •Disclaimer

- •Overview

- •Block Diagram

- •Pin Descriptions

- •Port B (PB5..PB0)

- •RESET

- •AVR CPU Core

- •Introduction

- •Architectural Overview

- •Status Register

- •Stack Pointer

- •Interrupt Response Time

- •SRAM Data Memory

- •Data Memory Access Times

- •EEPROM Data Memory

- •EEPROM Read/Write Access

- •Atomic Byte Programming

- •Split Byte Programming

- •Erase

- •Write

- •I/O Memory

- •Clock Systems and their Distribution

- •CPU Clock – clkCPU

- •I/O Clock – clkI/O

- •Flash Clock – clkFLASH

- •ADC Clock – clkADC

- •Clock Sources

- •Default Clock Source

- •External Clock

- •System Clock Prescaler

- •Switching Time

- •Idle Mode

- •Power-down Mode

- •Analog to Digital Converter

- •Analog Comparator

- •Brown-out Detector

- •Internal Voltage Reference

- •Watchdog Timer

- •Port Pins

- •Resetting the AVR

- •Reset Sources

- •Power-on Reset

- •External Reset

- •Brown-out Detection

- •Watchdog Reset

- •Watchdog Timer

- •Timed Sequences for Changing the Configuration of the Watchdog Timer

- •Safety Level 1

- •Safety Level 2

- •Interrupts

- •I/O Ports

- •Introduction

- •Configuring the Pin

- •Toggling the Pin

- •Reading the Pin Value

- •Unconnected Pins

- •Alternate Port Functions

- •Alternate Functions of Port B

- •Register Description for I/O-Ports

- •Port B Data Register – PORTB

- •External Interrupts

- •8-bit Timer/Counter0 with PWM

- •Overview

- •Registers

- •Definitions

- •Counter Unit

- •Output Compare Unit

- •Force Output Compare

- •Modes of Operation

- •Normal Mode

- •Fast PWM Mode

- •Phase Correct PWM Mode

- •Prescaler Reset

- •External Clock Source

- •Analog Comparator

- •Analog Comparator Multiplexed Input

- •Features

- •Operation

- •Starting a Conversion

- •Changing Channel or Reference Selection

- •ADC Input Channels

- •ADC Voltage Reference

- •ADC Noise Canceler

- •Analog Input Circuitry

- •ADC Accuracy Definitions

- •ADC Conversion Result

- •ADLAR = 0

- •ADLAR = 1

- •debugWIRE On-chip Debug System

- •Features

- •Overview

- •Physical Interface

- •Software Break Points

- •Limitations of debugWIRE

- •debugWIRE Related Register in I/O Memory

- •debugWire Data Register – DWDR

- •Performing a Page Write

- •Reading the Fuse and Lock Bits from Software

- •Preventing Flash Corruption

- •Fuse Bytes

- •Latching of Fuses

- •Signature Bytes

- •Calibration Byte

- •Page Size

- •Serial Downloading

- •Data Polling Flash

- •Data Polling EEPROM

- •Chip Erase

- •Programming the Flash

- •Programming the EEPROM

- •Reading the Flash

- •Reading the EEPROM

- •Power-off sequence

- •Electrical Characteristics

- •Absolute Maximum Ratings*

- •External Clock Drive Waveforms

- •External Clock Drive

- •ADC Characteristics – Preliminary Data

- •Active Supply Current

- •Idle Supply Current

- •Power-down Supply Current

- •Pin Pull-up

- •Register Summary

- •Instruction Set Summary

- •Ordering Information

- •Packaging Information

- •Erratas

- •Table of Contents

System Clock and

Clock Options

Clock Systems and their Distribution

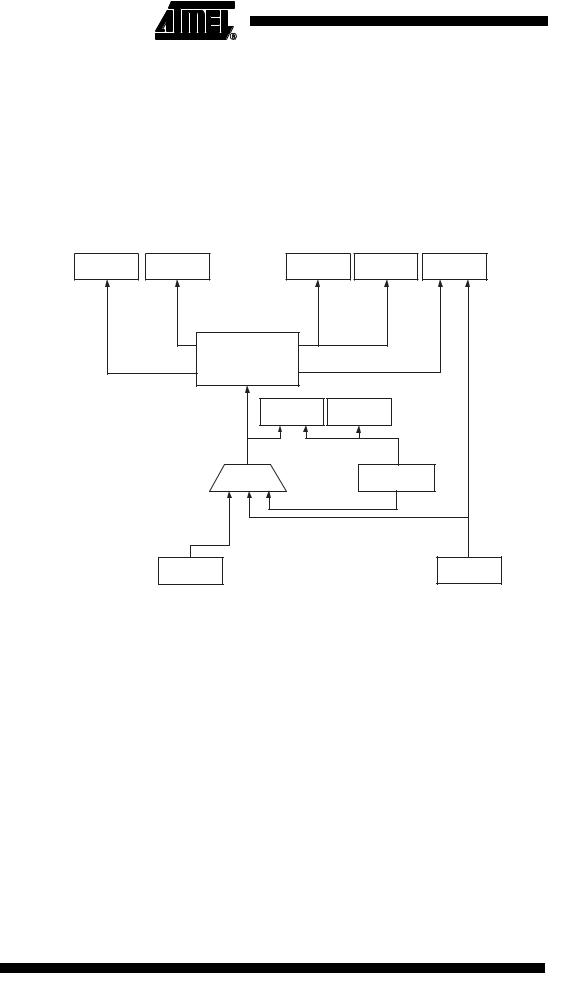

Figure 11 presents the principal clock systems in the AVR and their distribution. All of the clocks need not be active at a given time. In order to reduce power consumption, the clocks to modules not being used can be halted by using different sleep modes, as described in “Power Management and Sleep Modes” on page 26. The clock systems are detailed below.

Figure 11. |

Clock Distribution |

|

|

|

|

|

|

|

ADC |

General I/O |

|

CPU Core |

RAM |

Flash and |

|

|

Modules |

|

EEPROM |

||||

|

|

|

|

|

|

||

|

|

clkI/O |

AVR Clock |

clkCPU |

|

|

|

|

|

clkADC |

Control Unit |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

clkFLASH |

|

|

|

|

|

|

Reset Logic |

Watchdog Timer |

|

||

|

|

|

Source clock |

|

|

Watchdog clock |

|

|

|

|

Clock |

|

|

Watchdog |

|

|

|

|

Multiplexer |

|

|

Oscillator |

|

|

|

External Clock |

|

|

|

|

Calibrated RC |

|

|

|

|

|

|

Oscillator |

|

|

|

|

|

|

|

|

|

CPU Clock – clkCPU |

The CPU clock is routed to parts of the system concerned with operation of the AVR |

|

core. Examples of such modules are the General Purpose Register File, the Status Reg- |

|

ister and the Data memory holding the Stack Pointer. Halting the CPU clock inhibits the |

|

core from performing general operations and calculations. |

I/O Clock – clkI/O |

The I/O clock is used by the majority of the I/O modules, like Timer/Counter. The I/O |

|

clock is also used by the External Interrupt module, but note that some external inter- |

|

rupts are detected by asynchronous logic, allowing such interrupts to be detected even if |

|

the I/O clock is halted. |

Flash Clock – clkFLASH |

The Flash clock controls operation of the Flash interface. The Flash clock is usually |

|

active simultaneously with the CPU clock. |

ADC Clock – clkADC |

The ADC is provided with a dedicated clock domain. This allows halting the CPU and |

|

I/O clocks in order to reduce noise generated by digital circuitry. This gives more accu- |

|

rate ADC conversion results. |

20 ATtiny13

2535A–AVR–06/03