- •Оглавление

- •Предисловие

- •Лекция 1

- •1. Научные основы информатики

- •1.1. Цели и задачи дисциплины

- •1.2. Теоретические основы информатики

- •1.3. Практические основы информатики

- •1.3.1. Структура компьютера и принцип программного управления

- •1.3.2. Архитектура современного компьютера

- •1.4. Классификация компьютеров

- •Лекция 2

- •2. Назначение и основные представления о работе функциональных блоков компьютера

- •2.1. Оперативная память

- •2.3. Внешняя память

- •2.3.1. Магнитные диски

- •2.3.2. Оптические диски

- •2.3.3. Магнитооптические диски

- •2.3.4. Особенности устройства Flash-накопителей

- •2.3.4.1. Программирование ячейки

- •2.3.4.2. Стирание ячейки

- •3.1.2. Арифметическо – логическое устройство

- •3.1.3. Разрядность процессора

- •3.1.4. Принцип действия процессора

- •3.1.5. Тактовая частота

- •3.2. Адресация данных и команд в оперативной памяти компьютера

- •3.2.1. Методы адресации

- •3.2.2. Стековая организация памяти

- •3.2.3. Магазинная организация памяти

- •3.3. Системы счисления и кодирования информации

- •3.3.1. Виды систем счисления

- •3.3.2. Перевод чисел из восьмеричной и шестнадцатеричной системы счисления в десятичную

- •3.3.3. Перевод чисел из восьмеричной и шестнадцатеричной системы счисления в двоичную

- •3.3.4. Перевод чисел с двоичной системы счисления в восьмеричную и шестнадцатеричную

- •3.3.5. Перевод чисел с десятичной системы счисления в другие

- •3.3.5.1. Перевод целых десятичных чисел в двоичные.

- •3.3.5.2. Перевод дробных чисел

- •Лекция 4

- •4. Формы представления чисел в эвм

- •4.1. Представление чисел в форме с фиксированной точкой

- •4.2. Представление чисел в форме с плавающей точкой

- •В итоге получается

- •4.3.1. Операция алгебраического сложения чисел, представленных в форме с фиксированной точкой

- •4.3.2. Операция алгебраического сложения чисел, представленных в форме с плавающей точкой

- •4.3.3. Принципы аппаратной реализации операций умножения и деления

- •Кодирование алфавитно – цифровой информации

- •Базовыми логическими операциями являются операции

- •Смысл этих операций становится понятным из табл. 5.1

- •5.2. Триггеры

- •6.2. Дешифраторы

- •6.3. Счетчики

- •6.4. Сумматоры

- •Лекция 7

- •7. Алгоритм и программа. Виды вычислительных процессов

- •7.1. Алгоритм

- •7.1.2. Требования к алгоритму

- •7.2. Программа

- •7.3. Виды вычислительных процессов

- •Лекция 8

- •8. Типовые алгоритмы

- •8.1. Определение суммы чисел произвольного ряда

- •8.2. Определение произведения чисел произвольного ряда

- •8.3. Алгоритм определения наибольшего (наименьшего) числа из заданного ряда чисел

- •8.4. Алгоритм определения наибольшего (наименьшего) значения вычисляемой функции

- •8.5. Вычисление функции с одновременно изменяющимися несколькими аргументами

- •8.6. Итерационные циклы

- •9.1.2. Метод поиска наименьшего (наибольшего)

- •9.2. Типовые алгоритмы решения задач с использованием матриц

- •Лекция 10

- •10. Алгоритмические языки. Общие представления.

- •Символы языка

- •10.2. Данные

- •10.2.1. Собственные типы данных

- •10.3. Идентификаторы

- •Операции. Выражения

- •10.4.1. Операции

- •Логические операции

- •10.4.2. Выражения

- •Лекция 11

- •Безусловный оператор

- •11.1. Структура программы

- •11.2. Оператор условия

- •11.2.1. Альтернативный оператор условия.

- •11.2.2. Безальтернативный оператор условия

- •11.2.3. Составные операторы условия

- •11.3. Безусловный оператор

- •11.4. Оператор множественного выбора

- •Операция «Запятая»

- •12.1.2. Оператор цикла while

- •Более изящной является запись

- •12.1.3. Оператор цикла do . . . While

- •12.1.4. Операторы continue, break

- •12.2. Массивы. Переменные типа массив

- •12.2.1. Описание массивов

- •12.2.2. Ввод массивов Использование массивов в вычислениях предполагает их ввод, в качестве исходных данных, а также вывод их в качестве результата вычислений.

- •12.2.3. Вывод массивов

- •12.2.4. Операции с массивами

- •12.2.5. Многомерные массивы

- •Для четырехмерного

- •12.2.6. Представление многомерных массивов как массив массивов.

- •Описание массивов с помощью инструкции typedef

- •Лекция 13

- •13. Символьные массивы

- •13.1 Описание символьных массивов

- •13.2. Ввод символьных массивов

- •13.3. Операции со строками

- •13.4. Строковые массивы

- •Лекция 14

- •14. Внешние файлы. Переменные файлового типа Файл – это информация, размещенная на внешнем носителе и имеющая свое имя.

- •14.1. Текстовые файлы. Файловый ввод и вывод данных

- •Здесь fstream – ключевое слово, играющее роль имени типа переменной,

- •Функция open( )

- •Функция close( )

- •Функции eol( ) и eof ( )

- •Операторы открытия и закрытия файла

- •Спецификации ios::nocreate и ios::in комбинируются с помощью логической операции || (дизъюнкция).

- •14.1.1. Создание внешних файлов

- •14.1.2. Операции с файловыми переменными

- •14.2. Бинарные файлы

- •Лекция 15

- •15. Функции

- •15.1. Структура функций

- •15.2. Локальные и глобальные данные

- •15.3. Виды функций

- •15.3.1. Функции, возвращающие результат по значению

- •Вызов функции

- •Место записи оператора вызова

- •Особенности выделения памяти при вызове функции

- •15.3.2. Функции, возвращающие результат по ссылке

- •Вызов функции

- •15.3.3. Место расположения функций в программе

- •Лекция 16

- •16. Программное обеспечение компьютера. Основные представления

- •16.1. Операционная система

- •16.2. Прикладные программы

- •16.2.1. Текстовый редактор Microsoft Word

- •Интерфейс редактора

- •Основное меню

- •Панель инструментов

- •16.3. Электронные таблицы. Ms Excel.Основные представления

- •Интерфейс программы ms Excel

- •Рабочее окно представляет собой не чистое поле, а пустую таблицу, состоящую из столбцов и строк. Максимальный размер таблицы:

- •Операции с ячейками

- •Выделение ячеек

- •Выделение группы смежных ячеек

- •Выделение нескольких несмежных интервалов

- •Выделение отдельной строки и отдельного столбца

- •Ввод числовых данных

- •Ввод текста

- •Режим автозаполнения

- •Ввод даты и времени

- •Ввод последовательных рядов чисел

- •17.3. Редактирование данных

- •Копирование, перемещение и удаление данных

- •17.4. Операции с данными Сортировка

- •Автосуммирование

- •17.5. Работа с формулами

- •Порядок создания формул

- •17.6. Использование в формулах адресов ячеек

- •Удаленные ссылки

- •Лекция 18

- •18. Электронная таблица ms Excel. Функции

- •18.1. Операции и функции

- •Но совершенно очевидно, что она более громоздкая, чем запись сумм(а1: а8).

- •Ошибки в формулах

- •Автопересчет

- •18.2. Относительная и абсолютная адресация ячеек

- •18.3. Построение диаграмм

- •Общий порядок построения диаграмм

- •Лекция 19

- •19. Решение математических задач средствами ms Excel

- •19.1. Операции с матрицами

- •19.1.1. Транспонирование матриц

- •19.1.2. Вычисление определителя матрицы

- •19.1.3. Нахождение обратной матрицы

- •19.1.4. Сложение и вычитание матриц

- •19.1.5. Умножение матрицы на число

- •19.1.6. Умножение матриц

- •19.2. Решение систем линейных уравнений

- •19.3. Решение уравнения с одним неизвестным

- •Лекция 20

- •20. Электронные таблицы ms Excel. Форматирование данных. Операции с большими таблицами и листами

- •20.1. Форматирование данных

- •20.1.1. Форматирование текста

- •20.1.2. Форматирование чисел

- •К сожалению за одно обращение к окну Специальная вставка можно скопировать только один элемент. Поэтому для копирования нескольких элементов приходится несколько раз выполнять команду

- •20.2. Операции с большими таблицами

- •Скрытие столбцов и строк

- •Формат – Столбец – Отобразить.

- •Деление окна

- •На рис.20.1 выделена ячейка f5, которая делит окно на четыре области. Выделенная ячейка размещена в верхнем левом углу правой нижней области.

- •Для снятия деления необходимо выполнить операции с пунктами меню Окно – Снять разделение

- •Закрепление областей

- •20.3. Операции с рабочими листами

- •Переименование листов

- •Выделение группы листов

- •20.4. Печать

- •Лекция 21

- •21. Базы данных. Основные понятия и определения

- •21.1. Форма хранения информации

- •Реляционная модель базы данных

- •Структура таблиц базы данных

- •21.2.2. Индексы базы данных

- •21.2.3. Связи базы данных

- •Главная таблица

- •21.3. Основные виды работы с базами данных

- •Лекция 22

- •22. Система управления базой данных ms Access

- •22.1. Назначение и возможности субд ms Access

- •22.2. Запуск и завершение работы программы ms Access

- •23.3. Типы данных

- •22.4. Разработка и создание базы данных

- •22.4.1. Разработка структуры базы данных

- •22.4.2. Имена полей и объектов

- •22.5. Создание новой базы данных средствами субд ms Access

- •22.5.1.Создание таблиц базы данных с помощью мастера таблиц Под созданием базы данных подразумевается создание системы связанных таблиц с именами и заголовками полей, со значениями атрибутов в полях.

- •22.5.2. Создание таблиц в режиме конструктора

- •22.5.3. Создание связей

- •23.1.1. Создание формы в режиме автоформ

- •23.1.2. Создание формы в режиме мастера форм

- •В последнем окне мастера

- •При выборе варианта Изменить макет формы произойдет переключение в режим конструктора, в котором можно выполнить любую модификацию формы, созданной мастером.

- •23.1.3 Ввод и редактирование записей с помощью формы

- •23.1.4. Простейшие модификации формы с помощью конструктора

- •23.2. Поиск и запросы

- •23.2.1. Поиск и фильтрация данных

- •После этого следует задать образцы поиска и замены, установить параметры поиска и щелкнуть по нужной кнопке Найти далее, Заменить или Заменить все.

- •23.2.2. Применение фильтра

- •23.3. Типы запросов

- •Запрос на выборку

- •Запрос на изменение

- •Перекрестный запрос

- •23.3.1. Создание запроса на выборку

- •23.3.1.1. Создание запроса с помощью мастера

- •23.3.1.2. Создание запроса с помощью конструктора

- •23.3.2. Выполнение запроса

- •23.3.3. Модификация запроса

- •Лекция 24

- •24. Создание отчетов в ms Access. Презентация

- •24.1. Создание отчетов

- •24.1.1. Режим автоотчета

- •24.1.2. Создание отчета с помощью мастера

- •24.1.3. Модификация отчета в режиме конструктора

- •24.2. Печать отчета

- •Файл – Параметры страницы

- •Файл – Печать – Параметры печати

- •24.3. Презентация. Основные представления

- •24.3.4. Простейшие настройки программы ms Power Point

- •Лекция 25

- •25. Компьютерные сети. Основные представления

- •25.1. Линии связи

- •25.2. Компьютерные сети

- •25.3. Топология компьютерных сетей

- •25.4. Пропускная способность сетей

- •Функциональные структуры компьютерных сетей

- •Лекция 26

- •26. Интернет, общие представления. Основы работы в Интернете

- •26.1. Основные понятия и определения

- •26.1.1. Протоколы Интернет

- •26.1.3. Доменные адреса

- •26.1.4. Узел Интернета

- •26.1.5. Получение доступа к Интернету

- •26.1.6. Вход в Интернет

- •26.2. Информационные ресурсы Интернет

- •Основными представителями гипертекстовых документов являются Web – страница и сайт.

- •26.2.2. Адрес ресурса

- •Фактически url является адресом запрашиваемого ресурса в Интернете или просто адресом ресурса.

- •В общем случае url имеет достаточно сложную структуру. В простейших случаях, при запросе наиболее популярных ресурсов, например, для доступа к начальным страницам сайтов, url содержит:

- •26.3. Электронная почта

- •26.3.1. Сообщения

- •Структура сообщений

- •27.2. Операции с исходящими сообщениями

- •27.3. Операции с входящими сообщениями

- •27.4. Электронные доски объявлений

- •27.5. Телеконференции

- •27.6. Пересылка файлов

- •27.7. Интернет – пейджеры

- •27.8. Базы данных в Интернет

- •27.9. Обозреватели сети Интернет

- •Сервис – Свойства обозревателя

- •Запрос ресурса

- •Кодировка текста Web – страницы

- •Перемещение по гиперссылкам

- •Папка Избранное

- •Лекция 28

- •28. Создание Web – страниц. Поисковые системы

- •28.1. Создание Web – страниц

- •28.3. Загрузка файлов из сети Интернет

- •28.4. Работа с почтовым сайтом

- •28.5. Программа Outlook Express

- •28.5.1. Запуск и интерфейс программы Outlook Express

- •28.5.2. Создание учетной записи

- •28.5.4 Создание и отправка сообщения

- •– Щелкнуть по кнопке Создать сообщение, что вызовет появление окна, которое будет содержать бланк сообщения и необходимый инструментарий для его создания;

- •28.5.5. Разметка и форматирование сообщений

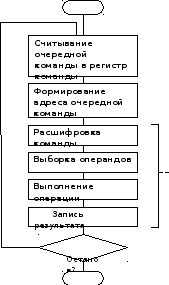

3.1.4. Принцип действия процессора

Принцип действия процессора можно понять на примере выполнения одной команды (рис.3.1).

Исполнение

команды

НЕТ

ДА

Рис. 3.1 Основной алгоритм работы процессора.

Рабочий цикл выполнения команды в основном одинаков для всех вычислительных машин различных поколений и отличается лишь некоторыми деталями реализации. Важной составной частью архитектуры компьютера по фон Нэйману является счетчик адреса команд. Он постоянно указывает на ячейку памяти, в которой хранится следующая команда. После считывания очередной команды из памяти процессор сразу же увеличивает значение счетчика так, чтобы он показывал адрес ячейки памяти со следующей командой. Затем считанная команда расшифровывается и выполняется в соответствии с алгоритмом, приведенным на рис. 3.1

. В данном алгоритме не задано первоначальное значение счетчика адреса команд. В этом случае аппаратным путем заносится стартовый адрес, находящейся в ПЗУ программы инициализации всех устройств и начальной загрузки ЭВМ.

3.1.5. Тактовая частота

Любая операция процессора (машинная команда) состоит из отдельных элементарных действий – тактов. В зависимости от сложности команда может быть реализована за различное число тактов. Например, пересылка информации из одного внутреннего регистра процессора в другой выполняется за несколько тактов, а для перемножения двух чисел количество тактов требуется на порядок больше. Существенное удлинение команды происходит, если обрабатываемые данные не находятся внутри процессора и их приходится считывать из памяти.

Для организации последовательного выполнения требуемых тактов в компьютере имеется специальный генератор тактовых импульсов. Каждый импульс инициализирует очередной такт машинной команды. Чем чаще следуют импульсы, тем быстрее будет выполнена операция, состоящая из фиксированного числа тактов. Тактовая частота определяется количеством тактов за секунду. Очевидно, что для повышения быстродействия компьютера, следует повышать тактовую частоту. Однако этому имеется ограничение – быстродействие процессора. Можно повышать тактовую частоту до такой степени, что процессор не будет успевать за один такт (интервал между соседними импульсами) выполнять элементарную операцию. В современных процессорах тактовая частота не превышает 1ГГц.

3.2. Адресация данных и команд в оперативной памяти компьютера

3.2.1. Методы адресации

При обмене информацией с памятью процессор обращается к ячейкам ОЗУ по их адресам. Способы задания требуемых адресов в командах компьютера принято называть методами адресации. От видов и разнообразия адресации существенно зависит эффективность работы. Сведения об адресе и его составных частях содержится в команде. Любая команда компьютера состоит из двух частей:

-

а д р е с н о й

-

о п е р а ц и о н н о й.

Иначе еще говорят, что команда состоит из адресного кода и кода операции или исполнительного кода.

Адресная часть показывает, где хранится необходимая для выполнения операции информация (данные) и куда (по какому адресу) помещать результат операции.

Операционная часть предписывает действие, которое необходимо выполнить с данными. Код операции представляет собой некоторый условный номер в общем списке системы команд. В основном этот список построен в соответствии с определенными внутренними закономерностями, хотя они и не всегда очевидны.

Известны четыре структуры команд:

– ч е т ы р е х а д р е с н а я,

– т р е х а д р е с н а я,

– д в у х а д р е с н а я,

– о д н о а д р е с н а я.

На рис. 3.1 приведены схемы этих структур.

-

Код

Операции

Адрес

А1

Адрес

А2

Адрес

А3

Адрес

А4

а

|

Код операции |

Адрес А1 |

Адрес А2 |

Адрес А3 |

б

-

Код

операции

Адрес

А1

Адрес

А2

в

|

Код операции |

Адрес А1 |

г

Рис. 3.1 Структура команд

а – четырехадресная, б – трехадресная, в – двухадресная, г – одноадресная.

В общем случае адресная часть должна содержать четыре адреса или адресных кода (рис. 3.1а). Адреса А1 и А2 – адреса двух операндов, участвующих в операции, А3 – адрес ячейки, куда помещается результат операции, А4 – адрес ячейки, содержащей следующую команду. Тогда реализацию операции сложения можно изобразить как

А3 = А1 + А2.

Такой порядок выборки называют принудительным, он устарел и в настоящее время не применяется. Учитывая то, что в программе все команды выполняются последовательно, то это означает, что, если выполнялась команда, адрес которой содержался в ячейке к, то адрес следующей команды будет в ячейке к + 1. Такой порядок выборки команд называют естественным. Он нарушается только специальными командами перехода. Поэтому в трехадресной команде, как видно из рис.3.1б, адрес следующей команды отсутствует. Он «по умолчанию» принимается следующим после адреса предыдущей команды. Этот метод называют косвенной адресацией. Следует иметь в виду, что адреса всех команд содержатся в специальном регистре – счетчике команд, куда они все предварительно заносятся. Характер реализации операции в трехадресной команде такой же, как и в четырехадресной.

В двухадресной команде кроме отсутствия адреса следующей команды, еще отсутствует и адрес результата (рис. 3.1в). В этом случае результат заносится по месту одного из операндов (обычно первого). Характер реализации операции с такой командой выглядит следующим образом

А1 = А1 + А2.

В одноадресной команде (рис.3.1г) подразумеваемые адреса имеют не только результат операции, но и один из операндов. Здесь указывается адрес только одного операнда, адресом второго операнда является содержимое триггерного регистра компьютера. Схема реализации операций при одноадресной команде выглядит следующим образом

Рг = Рг + А1.

Здесь

Рг

обозначает триггерный регистр.

Естественно, что при выборе той или иной

структуры команды, стремились к сокращению

размера ячейки памяти, выделяемой для

команды. Исходя из того, что команда

представляется в двоичном коде, то

разрядность ячейки будет определяться

разрядностью кода операции и адресов.

Разрядность кода операции зависит от

общего количества различных операций.

Если таковых, например, N,

и они определяются как ![]() ,

,

где m – количество двоичных разрядов ячейки, то отсюда это количество определится как

m

= log![]() N.

N.

В настоящее время широкое распространение получила одноадресная структура команд. В этом случае не требуется память для промежуточных результатов. Эту роль выполняет специальный регистр.