- •Оглавление

- •Предисловие

- •Лекция 1

- •1. Научные основы информатики

- •1.1. Цели и задачи дисциплины

- •1.2. Теоретические основы информатики

- •1.3. Практические основы информатики

- •1.3.1. Структура компьютера и принцип программного управления

- •1.3.2. Архитектура современного компьютера

- •1.4. Классификация компьютеров

- •Лекция 2

- •2. Назначение и основные представления о работе функциональных блоков компьютера

- •2.1. Оперативная память

- •2.3. Внешняя память

- •2.3.1. Магнитные диски

- •2.3.2. Оптические диски

- •2.3.3. Магнитооптические диски

- •2.3.4. Особенности устройства Flash-накопителей

- •2.3.4.1. Программирование ячейки

- •2.3.4.2. Стирание ячейки

- •3.1.2. Арифметическо – логическое устройство

- •3.1.3. Разрядность процессора

- •3.1.4. Принцип действия процессора

- •3.1.5. Тактовая частота

- •3.2. Адресация данных и команд в оперативной памяти компьютера

- •3.2.1. Методы адресации

- •3.2.2. Стековая организация памяти

- •3.2.3. Магазинная организация памяти

- •3.3. Системы счисления и кодирования информации

- •3.3.1. Виды систем счисления

- •3.3.2. Перевод чисел из восьмеричной и шестнадцатеричной системы счисления в десятичную

- •3.3.3. Перевод чисел из восьмеричной и шестнадцатеричной системы счисления в двоичную

- •3.3.4. Перевод чисел с двоичной системы счисления в восьмеричную и шестнадцатеричную

- •3.3.5. Перевод чисел с десятичной системы счисления в другие

- •3.3.5.1. Перевод целых десятичных чисел в двоичные.

- •3.3.5.2. Перевод дробных чисел

- •Лекция 4

- •4. Формы представления чисел в эвм

- •4.1. Представление чисел в форме с фиксированной точкой

- •4.2. Представление чисел в форме с плавающей точкой

- •В итоге получается

- •4.3.1. Операция алгебраического сложения чисел, представленных в форме с фиксированной точкой

- •4.3.2. Операция алгебраического сложения чисел, представленных в форме с плавающей точкой

- •4.3.3. Принципы аппаратной реализации операций умножения и деления

- •Кодирование алфавитно – цифровой информации

- •Базовыми логическими операциями являются операции

- •Смысл этих операций становится понятным из табл. 5.1

- •5.2. Триггеры

- •6.2. Дешифраторы

- •6.3. Счетчики

- •6.4. Сумматоры

- •Лекция 7

- •7. Алгоритм и программа. Виды вычислительных процессов

- •7.1. Алгоритм

- •7.1.2. Требования к алгоритму

- •7.2. Программа

- •7.3. Виды вычислительных процессов

- •Лекция 8

- •8. Типовые алгоритмы

- •8.1. Определение суммы чисел произвольного ряда

- •8.2. Определение произведения чисел произвольного ряда

- •8.3. Алгоритм определения наибольшего (наименьшего) числа из заданного ряда чисел

- •8.4. Алгоритм определения наибольшего (наименьшего) значения вычисляемой функции

- •8.5. Вычисление функции с одновременно изменяющимися несколькими аргументами

- •8.6. Итерационные циклы

- •9.1.2. Метод поиска наименьшего (наибольшего)

- •9.2. Типовые алгоритмы решения задач с использованием матриц

- •Лекция 10

- •10. Алгоритмические языки. Общие представления.

- •Символы языка

- •10.2. Данные

- •10.2.1. Собственные типы данных

- •10.3. Идентификаторы

- •Операции. Выражения

- •10.4.1. Операции

- •Логические операции

- •10.4.2. Выражения

- •Лекция 11

- •Безусловный оператор

- •11.1. Структура программы

- •11.2. Оператор условия

- •11.2.1. Альтернативный оператор условия.

- •11.2.2. Безальтернативный оператор условия

- •11.2.3. Составные операторы условия

- •11.3. Безусловный оператор

- •11.4. Оператор множественного выбора

- •Операция «Запятая»

- •12.1.2. Оператор цикла while

- •Более изящной является запись

- •12.1.3. Оператор цикла do . . . While

- •12.1.4. Операторы continue, break

- •12.2. Массивы. Переменные типа массив

- •12.2.1. Описание массивов

- •12.2.2. Ввод массивов Использование массивов в вычислениях предполагает их ввод, в качестве исходных данных, а также вывод их в качестве результата вычислений.

- •12.2.3. Вывод массивов

- •12.2.4. Операции с массивами

- •12.2.5. Многомерные массивы

- •Для четырехмерного

- •12.2.6. Представление многомерных массивов как массив массивов.

- •Описание массивов с помощью инструкции typedef

- •Лекция 13

- •13. Символьные массивы

- •13.1 Описание символьных массивов

- •13.2. Ввод символьных массивов

- •13.3. Операции со строками

- •13.4. Строковые массивы

- •Лекция 14

- •14. Внешние файлы. Переменные файлового типа Файл – это информация, размещенная на внешнем носителе и имеющая свое имя.

- •14.1. Текстовые файлы. Файловый ввод и вывод данных

- •Здесь fstream – ключевое слово, играющее роль имени типа переменной,

- •Функция open( )

- •Функция close( )

- •Функции eol( ) и eof ( )

- •Операторы открытия и закрытия файла

- •Спецификации ios::nocreate и ios::in комбинируются с помощью логической операции || (дизъюнкция).

- •14.1.1. Создание внешних файлов

- •14.1.2. Операции с файловыми переменными

- •14.2. Бинарные файлы

- •Лекция 15

- •15. Функции

- •15.1. Структура функций

- •15.2. Локальные и глобальные данные

- •15.3. Виды функций

- •15.3.1. Функции, возвращающие результат по значению

- •Вызов функции

- •Место записи оператора вызова

- •Особенности выделения памяти при вызове функции

- •15.3.2. Функции, возвращающие результат по ссылке

- •Вызов функции

- •15.3.3. Место расположения функций в программе

- •Лекция 16

- •16. Программное обеспечение компьютера. Основные представления

- •16.1. Операционная система

- •16.2. Прикладные программы

- •16.2.1. Текстовый редактор Microsoft Word

- •Интерфейс редактора

- •Основное меню

- •Панель инструментов

- •16.3. Электронные таблицы. Ms Excel.Основные представления

- •Интерфейс программы ms Excel

- •Рабочее окно представляет собой не чистое поле, а пустую таблицу, состоящую из столбцов и строк. Максимальный размер таблицы:

- •Операции с ячейками

- •Выделение ячеек

- •Выделение группы смежных ячеек

- •Выделение нескольких несмежных интервалов

- •Выделение отдельной строки и отдельного столбца

- •Ввод числовых данных

- •Ввод текста

- •Режим автозаполнения

- •Ввод даты и времени

- •Ввод последовательных рядов чисел

- •17.3. Редактирование данных

- •Копирование, перемещение и удаление данных

- •17.4. Операции с данными Сортировка

- •Автосуммирование

- •17.5. Работа с формулами

- •Порядок создания формул

- •17.6. Использование в формулах адресов ячеек

- •Удаленные ссылки

- •Лекция 18

- •18. Электронная таблица ms Excel. Функции

- •18.1. Операции и функции

- •Но совершенно очевидно, что она более громоздкая, чем запись сумм(а1: а8).

- •Ошибки в формулах

- •Автопересчет

- •18.2. Относительная и абсолютная адресация ячеек

- •18.3. Построение диаграмм

- •Общий порядок построения диаграмм

- •Лекция 19

- •19. Решение математических задач средствами ms Excel

- •19.1. Операции с матрицами

- •19.1.1. Транспонирование матриц

- •19.1.2. Вычисление определителя матрицы

- •19.1.3. Нахождение обратной матрицы

- •19.1.4. Сложение и вычитание матриц

- •19.1.5. Умножение матрицы на число

- •19.1.6. Умножение матриц

- •19.2. Решение систем линейных уравнений

- •19.3. Решение уравнения с одним неизвестным

- •Лекция 20

- •20. Электронные таблицы ms Excel. Форматирование данных. Операции с большими таблицами и листами

- •20.1. Форматирование данных

- •20.1.1. Форматирование текста

- •20.1.2. Форматирование чисел

- •К сожалению за одно обращение к окну Специальная вставка можно скопировать только один элемент. Поэтому для копирования нескольких элементов приходится несколько раз выполнять команду

- •20.2. Операции с большими таблицами

- •Скрытие столбцов и строк

- •Формат – Столбец – Отобразить.

- •Деление окна

- •На рис.20.1 выделена ячейка f5, которая делит окно на четыре области. Выделенная ячейка размещена в верхнем левом углу правой нижней области.

- •Для снятия деления необходимо выполнить операции с пунктами меню Окно – Снять разделение

- •Закрепление областей

- •20.3. Операции с рабочими листами

- •Переименование листов

- •Выделение группы листов

- •20.4. Печать

- •Лекция 21

- •21. Базы данных. Основные понятия и определения

- •21.1. Форма хранения информации

- •Реляционная модель базы данных

- •Структура таблиц базы данных

- •21.2.2. Индексы базы данных

- •21.2.3. Связи базы данных

- •Главная таблица

- •21.3. Основные виды работы с базами данных

- •Лекция 22

- •22. Система управления базой данных ms Access

- •22.1. Назначение и возможности субд ms Access

- •22.2. Запуск и завершение работы программы ms Access

- •23.3. Типы данных

- •22.4. Разработка и создание базы данных

- •22.4.1. Разработка структуры базы данных

- •22.4.2. Имена полей и объектов

- •22.5. Создание новой базы данных средствами субд ms Access

- •22.5.1.Создание таблиц базы данных с помощью мастера таблиц Под созданием базы данных подразумевается создание системы связанных таблиц с именами и заголовками полей, со значениями атрибутов в полях.

- •22.5.2. Создание таблиц в режиме конструктора

- •22.5.3. Создание связей

- •23.1.1. Создание формы в режиме автоформ

- •23.1.2. Создание формы в режиме мастера форм

- •В последнем окне мастера

- •При выборе варианта Изменить макет формы произойдет переключение в режим конструктора, в котором можно выполнить любую модификацию формы, созданной мастером.

- •23.1.3 Ввод и редактирование записей с помощью формы

- •23.1.4. Простейшие модификации формы с помощью конструктора

- •23.2. Поиск и запросы

- •23.2.1. Поиск и фильтрация данных

- •После этого следует задать образцы поиска и замены, установить параметры поиска и щелкнуть по нужной кнопке Найти далее, Заменить или Заменить все.

- •23.2.2. Применение фильтра

- •23.3. Типы запросов

- •Запрос на выборку

- •Запрос на изменение

- •Перекрестный запрос

- •23.3.1. Создание запроса на выборку

- •23.3.1.1. Создание запроса с помощью мастера

- •23.3.1.2. Создание запроса с помощью конструктора

- •23.3.2. Выполнение запроса

- •23.3.3. Модификация запроса

- •Лекция 24

- •24. Создание отчетов в ms Access. Презентация

- •24.1. Создание отчетов

- •24.1.1. Режим автоотчета

- •24.1.2. Создание отчета с помощью мастера

- •24.1.3. Модификация отчета в режиме конструктора

- •24.2. Печать отчета

- •Файл – Параметры страницы

- •Файл – Печать – Параметры печати

- •24.3. Презентация. Основные представления

- •24.3.4. Простейшие настройки программы ms Power Point

- •Лекция 25

- •25. Компьютерные сети. Основные представления

- •25.1. Линии связи

- •25.2. Компьютерные сети

- •25.3. Топология компьютерных сетей

- •25.4. Пропускная способность сетей

- •Функциональные структуры компьютерных сетей

- •Лекция 26

- •26. Интернет, общие представления. Основы работы в Интернете

- •26.1. Основные понятия и определения

- •26.1.1. Протоколы Интернет

- •26.1.3. Доменные адреса

- •26.1.4. Узел Интернета

- •26.1.5. Получение доступа к Интернету

- •26.1.6. Вход в Интернет

- •26.2. Информационные ресурсы Интернет

- •Основными представителями гипертекстовых документов являются Web – страница и сайт.

- •26.2.2. Адрес ресурса

- •Фактически url является адресом запрашиваемого ресурса в Интернете или просто адресом ресурса.

- •В общем случае url имеет достаточно сложную структуру. В простейших случаях, при запросе наиболее популярных ресурсов, например, для доступа к начальным страницам сайтов, url содержит:

- •26.3. Электронная почта

- •26.3.1. Сообщения

- •Структура сообщений

- •27.2. Операции с исходящими сообщениями

- •27.3. Операции с входящими сообщениями

- •27.4. Электронные доски объявлений

- •27.5. Телеконференции

- •27.6. Пересылка файлов

- •27.7. Интернет – пейджеры

- •27.8. Базы данных в Интернет

- •27.9. Обозреватели сети Интернет

- •Сервис – Свойства обозревателя

- •Запрос ресурса

- •Кодировка текста Web – страницы

- •Перемещение по гиперссылкам

- •Папка Избранное

- •Лекция 28

- •28. Создание Web – страниц. Поисковые системы

- •28.1. Создание Web – страниц

- •28.3. Загрузка файлов из сети Интернет

- •28.4. Работа с почтовым сайтом

- •28.5. Программа Outlook Express

- •28.5.1. Запуск и интерфейс программы Outlook Express

- •28.5.2. Создание учетной записи

- •28.5.4 Создание и отправка сообщения

- •– Щелкнуть по кнопке Создать сообщение, что вызовет появление окна, которое будет содержать бланк сообщения и необходимый инструментарий для его создания;

- •28.5.5. Разметка и форматирование сообщений

6.4. Сумматоры

Сумматором называется электронное устройство, выполняющее арифметическое суммирование кодов чисел.

Обычно сумматоры представляют собой комбинацию одноразрядных суммирующих схем. При сложении двух чисел, независимо от системы счисления, в каждом разряде производится сложение трех цифр:

-

цифры данного разряда первого слагаемого,

-

цифры данного разряда второго слагаемого,

-

цифры переноса из соседнего младшего разряда (1 или 0).

Таблица 6.2

-

Перенос из младшего разряда

X1

X2

S

Перенос в старший разряд

0

0

0

0

0

0

1

0

1

0

0

0

1

1

0

0

1

1

0

1

1

0

0

1

0

1

1

0

0

1

1

0

1

0

1

1

1

1

1

1

В результате сложения для каждого разряда получаются цифры суммы для этого разряда и цифра (1 или 0) переноса в следующий старший разряд. В таблице 6.2 показаны восемь возможных вариантов, возникающих при сложении двух двоичных чисел в одном разряде.

В параллельном сумматоре достигается более высокое быстродействие. В нем суммируемые коды поступают одновременно на все разряды.

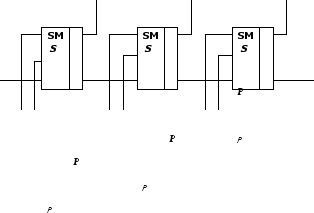

На рис. 6.6 приведена схема параллельного комбинационного сумматора.

Si –1 Si Si+ 1

Pi -1 Pi Pi+ 1 Pi+ 2

Xi –1 Yi –1 Xi Yi Xi + 1 Yi + 1

Рис.6.6 Схема параллельного комбинационного сумматора

В этом сумматоре, в каждом разряде одновременно формируется сумма. Хотя, если быть точным, то не совсем одновременно. На значение суммы влияет перенос, а он происходит последовательно и вносит некоторую задержку. При этом, до формирования окончательного результата на входах должны присутствовать входные сигналы Xi и Yi . Иногда суммирование разбивают на две операции:

-

суммирование двух слагаемых,

-

суммирование полученного результата с переносом из соседнего младшего разряда.

Xi

Yi

Xi

Yi

Si

Pi + 1

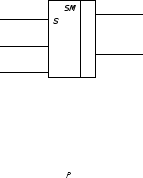

Рис. 6.7 Функциональная схема полусумматора

Xi

Si

Xi

Si

Yi Pi + 1

Рис.6.8. Условное обозначение полусумматора

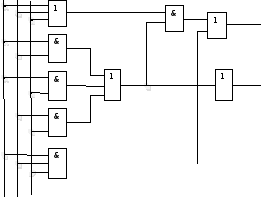

Каждая из этих операций выполняется полусумматором. На рис.6.7 приведена функциональная схема полусумматора, а на рис.6.8 – его условное обозначение.

В таблице 6.3 приведена карта состояний полусумматора.

Таблица 6.3

-

Xi

Yi

Si

Pi+ 1

0

0

0

0

0

1

1

0

1

0

1

0

1

1

0

1

Здесь Xi и Yi – входные данные (слагаемые),

Si – сумма,

Pi + 1 – единица переноса в старший разряд при переполнении младшего разряда.

Xi Yi Pi

Si

Pi + 1

Рис. 6.9 Функциональная схема одноразрядного сумматора

На рис. 6.9 и рис.6.10 приведена соответственно функциональная схема и условное обозначение одноразрядного сумматора, а в таблице 6.4 представлена карта состояний.

Xi Si

Yi

Pi Pi + 1

Рис. 6.10 Условное обозначение одноразрядного сумматора

Таблица 6.4

Карта состояния одноразрядного сумматора

-

Xi

Yi

Pi

Si

Pi + 1

0

0

0

0

0

0

0

1

1

0

0

1

0

1

0

0

1

1

0

1

1

0

0

1

0

1

0

1

0

1

1

1

0

0

1

1

1

1

1

1

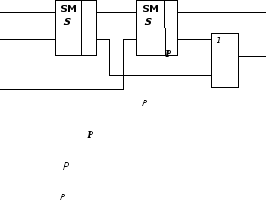

Сумматор можно реализовать также с помощью двух полусумматоров и логического элемента ИЛИ (Рис.6.11).

Xi

Si

Xi

Si

Yi

Pi + 1

Pi

Рис. 6.11 Функциональная схема сумматора

Суммирование многоразрядных кодов осуществляется с помощью одноразрядных сумматоров. При этом, в зависимости от способа ввода – вывода кодов и организации переносов, многоразрядные сумматоры бывают:

-

последовательного и

-

параллельного

принципа действия.

В последовательном сумматоре происходит поразрядное сложение кодов, начиная с младшего разряда, с помощью комбинационного сумматора на три входа. При этом перенос в старший разряд производится с задержкой до момента поступления следующего разряда слагаемых. Такой сумматор прост в реализации, но недостаточно быстродействующий.